Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# 1 pC Charge Injection, 100 pA Leakage, CMOS, ±5 V/5 V/3 V, Quad SPST Switches

Enhanced Product ADG613-EP

#### **FEATURES**

1 pC charge injection

±0.1 nA maximum at 25°C leakage currents

85 Ω on resistance

Rail-to-rail switching operation

Fast switching times

16-lead TSSOP

Typical power consumption: ≤11 nW

TTL-/CMOS-compatible inputs

V<sub>SS</sub> to V<sub>DD</sub> analog signal range

±2.7 V to ±5.5 V dual supply operation

2.7 V to 5.5 V single-supply operation

#### **ENHANCED PRODUCT FEATURES**

Fully specified at ±5 V, 3 V, and 5 V

Supports defense and aerospace applications (AQEC standard)

Military temperature range: -55°C to+125°C

Controlled manufacturing baseline

1 assembly site

1 test site

1 fabrication site

Enhanced product change notification

Qualification data available on request

#### **APPLICATIONS**

Automatic test equipment

Data acquisition systems

Battery-powered systems

Communications systems

Sample-and-hold systems

Audio signal routing

Relay replacement

Avionics

#### **GENERAL DESCRIPTION**

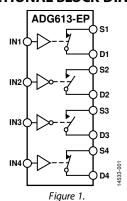

The ADG613-EP is a monolithic CMOS device containing four independently selectable switches. This switch offers ultralow charge injection of 1 pC over the full input signal range and typical leakage currents of 0.01 nA at 25°C.

The device is fully specified for  $\pm 5$  V, 5 V, and 3 V supplies. It contains four independent single-pole, single-throw (SPST) switches. The ADG613-EP contains two switches with digital control logic that turns on with logic low and two switches in which the logic is inverted.

Each switch conducts equally well in both directions when on and has an input signal range that extends to the supplies. The

Rev. A Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

#### **FUNCTIONAL BLOCK DIAGRAM**

ADG613-EP exhibits break-before-make switching action.

The ADG613-EP is available in a small, 16-lead TSSOP package.

The ADG613-EP is also a TTL-compatible device.

Additional application and technical information can be found in the ADG613 data sheet.

#### **PRODUCT HIGHLIGHTS**

- 1. Ultralow charge injection (1 pC typically).

- 2. Dual  $\pm 2.7$  V to  $\pm 5.5$  V or single 2.7 V to 5.5 V operation.

- 3. Temperature range: -55°C to +125°C.

- 4. Small, 16-lead TSSOP.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781.329.4700 ©2016 Analog Devices, Inc. All rights reserved.

Technical Support www.analog.com

# **TABLE OF CONTENTS**

| reatures                  | 1 |

|---------------------------|---|

| Enhanced Product Features |   |

|                           |   |

| Applications              |   |

| Functional Block Diagram  | 1 |

| General Description       | 1 |

| Product Highlights        | 1 |

| Revision History          | 2 |

| Specifications            | 3 |

| Dual-Supply Operation     | 3 |

|                           |   |

| Single-Supply Operation                     | 4  |

|---------------------------------------------|----|

| Absolute Maximum Ratings                    |    |

| ESD Caution                                 |    |

| Pin Configuration and Function Descriptions |    |

| Typical Performance Characteristics         | 8  |

| Test Circuits                               | 10 |

| Outline Dimensions                          | 12 |

| Ordering Guide                              | 13 |

#### **REVISION HISTORY**

10/2016-Rev. 0 to Rev. A

6/2016—Revision 0: Initial Revision

# **SPECIFICATIONS**

#### **DUAL-SUPPLY OPERATION**

$V_{DD} = 5~V~\pm~10\%, V_{SS} = -5~V~\pm~10\%, GND = 0~V, unless otherwise~noted.~V_{S}~is~the~source~voltage.~V_{D}~is~the~drain~voltage.$

Table 1.

| Parameter                                                                      | 25°C  | -55°C to +125℃       | Unit    | Test Conditions/Comments                                                                     |

|--------------------------------------------------------------------------------|-------|----------------------|---------|----------------------------------------------------------------------------------------------|

| ANALOG SWITCH                                                                  |       |                      |         |                                                                                              |

| Analog Signal Range                                                            |       | $V_{ss}$ to $V_{DD}$ | V       |                                                                                              |

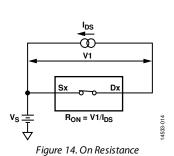

| On Resistance, R <sub>on</sub>                                                 | 85    |                      | Ωtyp    | $V_s = \pm 3 \text{ V}, I_s = -1 \text{ mA}$ ; see Figure 14                                 |

|                                                                                | 115   | 160                  | Ωmax    | $V_s = \pm 3 \text{ V, } I_s = -1 \text{ mA; see Figure 14}$                                 |

| On-Resistance Match Between Channels, ΔR <sub>ON</sub>                         | 2     |                      | Ωtyp    | $V_s = \pm 3 \text{ V, } I_s = -1 \text{ mA}$                                                |

|                                                                                | 4     | 6.5                  | Ω max   | $V_s = \pm 3 \text{ V}, I_s = -1 \text{ mA}$                                                 |

| On-Resistance Flatness, R <sub>FLAT(ON)</sub>                                  | 25    |                      | Ωtyp    | $V_s = \pm 3 \text{ V, } I_s = -1 \text{ mA}$                                                |

| ,,                                                                             | 40    | 60                   | Ω max   | $V_s = \pm 3 \text{ V, } I_s = -1 \text{ mA}$                                                |

| LEAKAGE CURRENTS                                                               |       |                      |         | $V_{DD} = +5.5 \text{ V}, V_{SS} = -5.5 \text{ V}$                                           |

| Source Off Leakage, I <sub>S(OFF)</sub>                                        | ±0.01 |                      | nA typ  | $V_D = \pm 4.5 \text{ V}, V_S = \mp 4.5 \text{ V}; \text{ see Figure 15}$                    |

|                                                                                | ±0.1  | ±2                   | nA max  | $V_D = \pm 4.5 \text{ V}, V_S = \mp 4.5 \text{ V}; \text{ see Figure 15}$                    |

| Drain Off Leakage, I <sub>D(OFF)</sub>                                         | ±0.01 |                      | nA typ  | $V_D = \pm 4.5 \text{ V, } V_S = \mp 4.5 \text{ V; see Figure 15}$                           |

| Diam on Ecanage, 10(0FF)                                                       | ±0.1  | ±2                   | nA max  | $V_D = \pm 4.5 \text{ V}, V_S = \mp 4.5 \text{ V}; \text{ see Figure 15}$                    |

| Character On Lanks and L.                                                      |       | 1 12                 |         | l -                                                                                          |

| Channel On Leakage, I <sub>D(ON)</sub> , I <sub>S(ON)</sub>                    | ±0.01 |                      | nA typ  | $V_D = V_S = \pm 4.5 \text{ V}$ ; see Figure 16                                              |

| DICITAL INDUITO                                                                | ±0.1  | ±6                   | nA max  | $V_D = V_S = \pm 4.5 \text{ V}$ ; see Figure 16                                              |

| DIGITAL INPUTS                                                                 |       | 2.4                  | V/ !    |                                                                                              |

| Input High Voltage, V <sub>NH</sub>                                            |       | 2.4                  | V min   |                                                                                              |

| Input Low Voltage, V <sub>INL</sub>                                            | 0.005 | 0.8                  | V max   |                                                                                              |

| Input Current, I <sub>INL</sub> or I <sub>INH</sub>                            | 0.005 |                      | μA typ  | $V_{IN} = V_{INL} \text{ or } V_{INH}$                                                       |

| But III as a second                                                            |       | ±0.1                 | μA max  | $V_{IN} = V_{INL} \text{ or } V_{INH}$                                                       |

| Digital Input Capacitance, $C_{\mathbb{N}}$                                    | 2     |                      | pF typ  |                                                                                              |

| DYNAMIC CHARACTERISTICS <sup>1</sup>                                           |       |                      |         |                                                                                              |

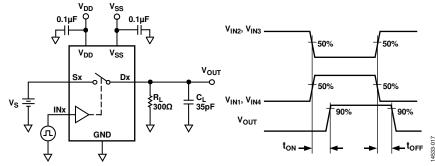

| Delay from Digital Control Input and Output Switching On, $t_{\text{ON}}$      | 45    |                      | nstyp   | $R_L = 300 \Omega$ , $C_L = 35 \text{pF}$ , $V_s = 3.0 \text{V}$ ; see Figure 17             |

|                                                                                | 65    | 90                   | ns max  | $R_L = 300 \Omega$ , $C_L = 35 \text{pF}$ , $V_S = 3.0 \text{V}$ ; see Figure 17             |

| Delay from Digital Control Input and Output<br>Switching Off, t <sub>OFF</sub> | 25    |                      | ns typ  | $R_L = 300 \Omega$ , $C_L = 35 \text{pF}$ , $V_S = 3.0 \text{V}$ ; see Figure 17             |

|                                                                                | 40    | 50                   | ns max  | $R_L = 300 \Omega$ , $C_L = 35 \text{pF}$ , $V_S = 3.0 \text{V}$ ; see Figure 17             |

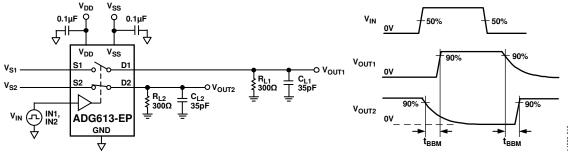

| Break-Before-Make Time Delay, t <sub>BBM</sub>                                 | 15    |                      | ns typ  | $R_L = 300 \Omega$ , $C_L = 35 \text{pF}$ , $V_{S1} = V_{S2} = 3.0 \text{V}$ ; see Figure 18 |

|                                                                                |       | 10                   | ns min  | $R_L = 300 \Omega$ , $C_L = 35 \text{pF}$ , $V_{S1} = V_{S2} = 3.0 \text{V}$ ; see Figure 18 |

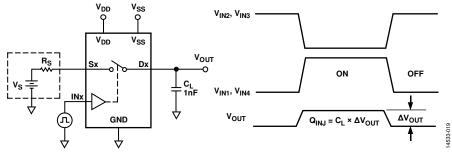

| Charge Injection                                                               | -0.5  |                      | pC typ  | $V_s = 0 \text{ V, R}_s = 0 \Omega$ , $C_L = 1 \text{ nF}$ ; see Figure 19                   |

| OffIsolation                                                                   | -65   |                      | dB typ  | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 10 MHz$ ; see Figure 20                              |

| Channel to Channel Crosstalk                                                   | -90   |                      | dB typ  | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 10 MHz$ ; see Figure 21                              |

| −3 dB Bandwidth                                                                | 680   |                      | MHz typ | $R_L = 50 \Omega$ , $C_L = 5 pF$ ; see Figure 22                                             |

| Off Switch Source Capacitance, C <sub>S(OFF)</sub>                             | 5     |                      | pF typ  | f= 1 MHz                                                                                     |

| Off Switch Drain Capacitance, CD(OFF)                                          | 5     |                      | pF typ  | f= 1 MHz                                                                                     |

| On Switch Capacitance, $C_{D(ON)}$ , $C_{S(ON)}$                               | 5     |                      | pF typ  | f= 1 MHz                                                                                     |

| POWER REQUIREMENTS                                                             |       |                      |         | $V_{DD} = +5.5 \text{ V}, V_{SS} = -5.5 \text{ V}$                                           |

| Positive Supply Current, IDD                                                   | 0.001 |                      | μA typ  | Digital inputs = 0 V or 5.5 V                                                                |

| ,                                                                              |       | 1.0                  | μA max  | Digital inputs = 0 V or 5.5 V                                                                |

| Negative Supply Current, Iss                                                   | 0.001 |                      | μA typ  | Digital inputs = 0 V or 5.5 V                                                                |

| , , , , , , , , , , , , , , , , , , , ,                                        |       | 1.0                  | μA max  | Digital inputs = 0 V or 5.5 V                                                                |

| $V_{DD}/V_{SS}$                                                                |       | ±2.7                 | V min   | - Jp                                                                                         |

| 55. 55                                                                         |       | ±5.5                 | V max   |                                                                                              |

| Power Consumption                                                              | 11    |                      | nW typ  |                                                                                              |

| ==:::=:::: =:::=::                                                             | 11    |                      | μW max  |                                                                                              |

$<sup>^{\</sup>rm 1}\, {\rm Guaranteed}$  by design; not subject to production test.

## **SINGLE-SUPPLY OPERATION**

$V_{DD}$  = 5 V  $\pm$  10%,  $V_{SS}$  = 0 V, GND = 0 V, unless otherwise noted.  $V_{S}$  is the source voltage.  $V_{D}$  is the drain voltage.

Table 2.

| Parameter                                                   | 25°C  | -55°C to +125°C        | Unit    | Test Conditions/Comments                                                                    |

|-------------------------------------------------------------|-------|------------------------|---------|---------------------------------------------------------------------------------------------|

| ANALOG SWITCH                                               |       |                        |         |                                                                                             |

| Analog Signal Range                                         |       | $0$ to $V_{\text{DD}}$ | V       |                                                                                             |

| On Resistance, R <sub>ON</sub>                              | 210   |                        | Ωtyp    | $V_S = 3.5 \text{ V, } I_S = -1 \text{ mA; see Figure 14}$                                  |

|                                                             | 290   | 380                    | Ω max   | $V_S = 3.5 \text{ V, } I_S = -1 \text{ mA; see Figure 14}$                                  |

| On-Resistance Match                                         | 3     |                        | Ωtyp    | $V_S = 3.5 \text{ V, } I_S = -1 \text{ mA}$                                                 |

| Between Channels, $\Delta R_{ON}$                           |       |                        |         |                                                                                             |

|                                                             | 10    | 13                     | Ω max   | $V_S = 3.5 \text{ V, } I_S = -1 \text{ mA}$                                                 |

| LEAKAGE CURRENTS                                            |       |                        |         | $V_{DD} = 5.5 \text{ V}$                                                                    |

| Source Off Leakage, I <sub>S(OFF)</sub>                     | ±0.01 |                        | nA typ  | $V_S = 1 \text{ V or } 4.5 \text{ V, } V_D = 4.5 \text{ V or } 1 \text{ V; see Figure } 15$ |

|                                                             | ±0.1  | ±2                     | nA max  | $V_S = 1 \text{ V or } 4.5 \text{ V, } V_D = 4.5 \text{ V or } 1 \text{ V; see Figure } 15$ |

| Drain Off Leakage, I <sub>D(OFF)</sub>                      | ±0.01 |                        | nA typ  | $V_S = 1 \text{ V or } 4.5 \text{ V, } V_D = 4.5 \text{ V or } 1 \text{ V; see Figure } 15$ |

|                                                             | ±0.1  | ±2                     | nA max  | $V_S = 1 \text{ V or } 4.5 \text{ V, } V_D = 4.5 \text{ V or } 1 \text{ V; see Figure } 15$ |

| Channel On Leakage, I <sub>D(ON)</sub> , I <sub>S(ON)</sub> | ±0.01 |                        | nA typ  | $V_S = V_D = 1 \text{ V or } 4.5 \text{ V}$ ; see Figure 16                                 |

|                                                             | ±0.1  | ±6                     | nA max  | $V_S = V_D = 1 \text{ V or } 4.5 \text{ V}$ ; see Figure 16                                 |

| DIGITAL INPUTS                                              |       |                        |         |                                                                                             |

| Input High Voltage, V <sub>INH</sub>                        |       | 2.4                    | V min   |                                                                                             |

| Input Low Voltage, V <sub>INL</sub>                         |       | 0.8                    | V max   |                                                                                             |

| Input Current, I <sub>INL</sub> or I <sub>INH</sub>         | 0.005 |                        | μA typ  | $V_{IN} = V_{INL}$ or $V_{INH}$                                                             |

|                                                             |       | ±0.1                   | μA max  | $V_{IN} = V_{INL}$ or $V_{INH}$                                                             |

| Digital Input Capacitance, C <sub>IN</sub>                  | 2     |                        | pF typ  |                                                                                             |

| DYNAMIC CHARACTERISTICS <sup>1</sup>                        |       |                        |         |                                                                                             |

| t <sub>ON</sub>                                             | 70    |                        | ns typ  | $R_L = 300 \Omega$ , $C_L = 35 \text{pF}$ , $V_S = 3.0 \text{V}$ ; see Figure 17            |

|                                                             | 100   | 150                    | ns max  | $R_L = 300 \Omega$ , $C_L = 35 \text{pF}$ , $V_S = 3.0 \text{V}$ ; see Figure 17            |

| t <sub>OFF</sub>                                            | 25    |                        | ns typ  | $R_L = 300 \Omega$ , $C_L = 35 \text{pF}$ , $V_S = 3.0 \text{V}$ ; see Figure 17            |

|                                                             | 40    | 50                     | ns max  | $R_L = 300 \Omega$ , $C_L = 35 \text{pF}$ , $V_S = 3.0 \text{V}$ ; see Figure 17            |

| Break-Before-Make Time Delay, t <sub>BBM</sub>              | 25    |                        | ns typ  | $R_L = 300 \Omega$ , $C_L = 35 pF$ , $V_{S1} = V_{S2} = 3.0 V$ ; see Figure 18              |

|                                                             |       | 10                     | ns min  | $R_L = 300 \Omega$ , $C_L = 35 pF$ , $V_{S1} = V_{S2} = 3.0 V$ ; see Figure 18              |

| Charge Injection                                            | 1     |                        | pC typ  | $V_S = 0 \text{ V, } R_S = 0 \Omega, C_L = 1 \text{ nF; see Figure 19}$                     |

| Off Isolation                                               | -62   |                        | dB typ  | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 10 MHz$ ; see Figure 20                             |

| Channel to Channel Crosstalk                                | -90   |                        | dB typ  | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 10 MHz$ ; see Figure 21                             |

| −3 dB Bandwidth                                             | 680   |                        | MHz typ | $R_L = 50 \Omega$ , $C_L = 5 pF$ ; see Figure 22                                            |

| $C_{S(OFF)}$                                                | 5     |                        | pF typ  | f = 1 MHz                                                                                   |

| $C_{D(OFF)}$                                                | 5     |                        | pF typ  | f = 1 MHz                                                                                   |

| $C_{D(ON)}$ , $C_{S(ON)}$                                   | 5     |                        | pF typ  | f = 1 MHz                                                                                   |

| POWER REQUIREMENTS                                          |       |                        |         | $V_{DD} = 5.5 \text{ V}$                                                                    |

| $I_{DD}$                                                    | 0.001 |                        | μA typ  | Digital inputs = 0 V or 5.5 V                                                               |

|                                                             |       | 1.0                    | μA max  | Digital inputs = 0 V or 5.5 V                                                               |

| $V_{DD}$                                                    |       | 2.7                    | V min   |                                                                                             |

|                                                             |       | 5.5                    | V max   |                                                                                             |

| Power Consumption                                           | 5.5   |                        | nW typ  |                                                                                             |

|                                                             | 5.5   | 1                      | μW max  |                                                                                             |

<sup>&</sup>lt;sup>1</sup> Guaranteed by design; not subject to production test.

$V_{DD}$  = 3 V  $\pm$  10%,  $V_{SS}$  = 0 V, GND = 0 V, unless otherwise noted.  $V_{S}$  is the source voltage.  $V_{D}$  is the drain voltage.

Table 3.

| Parameter                                                   | 25°C  | -55°C to +125°C | Unit    | Test Conditions/Comments                                                                |

|-------------------------------------------------------------|-------|-----------------|---------|-----------------------------------------------------------------------------------------|

| ANALOG SWITCH                                               |       |                 |         |                                                                                         |

| Analog Signal Range                                         |       | $0$ to $V_{DD}$ | V       |                                                                                         |

| On Resistance, R <sub>ON</sub>                              | 380   | 460             | Ω typ   | $V_S = 1.5 \text{ V, } I_S = -1 \text{ mA; see Figure 14}$                              |

| LEAKAGE CURRENTS                                            |       |                 |         | V <sub>DD</sub> = 3.3 V                                                                 |

| Source Off Leakage, I <sub>S(OFF)</sub>                     | ±0.01 |                 | nA typ  | $V_S = 1 \text{ V or } 3 \text{ V, } V_D = 3 \text{ V or } 1 \text{ V; see Figure } 15$ |

|                                                             | ±0.1  | ±2              | nA max  | $V_S = 1 \text{ V or } 3 \text{ V, } V_D = 3 \text{ V or } 1 \text{ V; see Figure } 15$ |

| Drain Off Leakage, I <sub>D(OFF)</sub>                      | ±0.01 |                 | nA typ  | $V_S = 1 \text{ V or } 3 \text{ V, } V_D = 3 \text{ V or } 1 \text{ V; see Figure } 15$ |

|                                                             | ±0.1  | ±2              | nA max  | $V_S = 1 \text{ V or } 3 \text{ V, } V_D = 3 \text{ V or } 1 \text{ V; see Figure } 15$ |

| Channel On Leakage, I <sub>D(ON)</sub> , I <sub>S(ON)</sub> | ±0.01 |                 | nA typ  | $V_S = V_D = 1 \text{ V or } 3 \text{ V}$ ; see Figure 16                               |

|                                                             | ±0.1  | ±6              | nA max  | $V_S = V_D = 1 \text{ V or } 3 \text{ V}$ ; see Figure 16                               |

| DIGITAL INPUTS                                              |       |                 |         |                                                                                         |

| Input High Voltage, V <sub>INH</sub>                        |       | 2.0             | V min   |                                                                                         |

| Input Low Voltage, V <sub>INL</sub>                         |       | 0.8             | V max   |                                                                                         |

| Input Current, I <sub>INL</sub> or I <sub>INH</sub>         | 0.005 |                 | μA typ  | $V_{IN} = V_{INL} \text{ or } V_{INH}$                                                  |

|                                                             |       | ±0.1            | μA max  | $V_{IN} = V_{INL}$ or $V_{INH}$                                                         |

| Digital Input Capacitance, C <sub>IN</sub>                  | 2     |                 | pF typ  |                                                                                         |

| DYNAMIC CHARACTERISTICS <sup>1</sup>                        |       |                 |         |                                                                                         |

| ton                                                         | 130   |                 | ns typ  | $R_L = 300 \Omega$ , $C_L = 35 \text{pF}$ , $V_S = 2 \text{V}$ ; see Figure 17          |

|                                                             | 185   | 260             | ns max  | $R_L = 300 \Omega$ , $C_L = 35 \text{pF}$ , $V_S = 2 \text{V}$ ; see Figure 17          |

| t <sub>OFF</sub>                                            | 40    |                 | ns typ  | $R_L = 300 \Omega$ , $C_L = 35 \text{pF}$ , $V_S = 2 \text{V}$ ; see Figure 17          |

|                                                             | 55    | 65              | ns max  | $R_L = 300 \Omega$ , $C_L = 35 \text{pF}$ , $V_S = 2 \text{V}$ ; see Figure 17          |

| Break-Before-Make Time Delay, t <sub>BBM</sub>              | 50    |                 | ns typ  | $R_L = 300 \Omega$ , $C_L = 35 pF$ , $V_{S1} = V_{S2} = 2 V$ ; see Figure 18            |

|                                                             |       | 10              | ns min  | $R_L = 300 \Omega$ , $C_L = 35 pF$ , $V_{S1} = V_{S2} = 2 V$ ; see Figure 18            |

| Charge Injection                                            | 1.5   |                 | pC typ  | $V_S = 0 \text{ V}$ , $R_S = 0 \Omega$ , $C_L = 1 \text{ nF}$ ; see Figure 19           |

| Off Isolation                                               | -62   |                 | dB typ  | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 10 MHz$ ; see Figure 20                         |

| Channel to Channel Crosstalk                                | -90   |                 | dB typ  | $R_L = 50 \Omega$ , $C_L = 5 pF$ , $f = 10 MHz$ ; see Figure 21                         |

| –3 dB Bandwidth                                             | 680   |                 | MHz typ | $R_L = 50 \Omega$ , $C_L = 5 pF$ ; see Figure 22                                        |

| $C_{S(OFF)}$                                                | 5     |                 | pF typ  | f = 1 MHz                                                                               |

| $C_{D(OFF)}$                                                | 5     |                 | pF typ  | f = 1 MHz                                                                               |

| $C_{D(ON)}$ , $C_{S(ON)}$                                   | 5     |                 | pF typ  | f = 1 MHz                                                                               |

| POWER REQUIREMENTS                                          |       |                 |         | $V_{DD} = 3.3 \text{ V}$                                                                |

| $I_{DD}$                                                    | 0.001 |                 | μA typ  | Digital inputs = 0 V or 3.3 V                                                           |

|                                                             |       | 1.0             | μA max  | Digital inputs = 0 V or 3.3 V                                                           |

| $V_{DD}$                                                    |       | 2.7             | V min   |                                                                                         |

|                                                             |       | 5.5             | V max   |                                                                                         |

| Power Consumption                                           | 3.3   |                 | nW typ  |                                                                                         |

|                                                             | 3.3   |                 | μW max  |                                                                                         |

<sup>&</sup>lt;sup>1</sup> Guaranteed by design; not subject to production test.

### ABSOLUTE MAXIMUM RATINGS

$T_A = 25$ °C, unless otherwise noted

Table 4.

| Table 4.                                        |                                                                   |  |  |  |  |

|-------------------------------------------------|-------------------------------------------------------------------|--|--|--|--|

| Parameter                                       | Rating                                                            |  |  |  |  |

| V <sub>DD</sub> to V <sub>SS</sub> <sup>1</sup> | 13 V                                                              |  |  |  |  |

| $V_{DD}$ to $GND^1$                             | −0.3 V to +6.5 V                                                  |  |  |  |  |

| V <sub>SS</sub> to GND <sup>1</sup>             | +0.3 V to -6.5 V                                                  |  |  |  |  |

| Analog Inputs <sup>2</sup>                      | $V_{SS} - 0.3  V  to  V_{DD} + 0.3  V$                            |  |  |  |  |

| Digital Inputs <sup>2</sup>                     | GND $-0.3$ V to $V_{DD} + 0.3$ V or 30 mA, whichever occurs first |  |  |  |  |

| Peak Current, Sx or Dx                          | 20 mA (pulsed at 1 ms, 10% duty cycle maximum)                    |  |  |  |  |

| Continuous Current, Sx or Dx                    | 10 mA                                                             |  |  |  |  |

| 3 V Operation, 85℃ to 125℃                      | 7.5 mA                                                            |  |  |  |  |

| Operating Temperature Range                     | –55℃ to +125℃                                                     |  |  |  |  |

| Storage Temperature Range                       | –65℃ to +150℃                                                     |  |  |  |  |

| Junction Temperature                            | 150℃                                                              |  |  |  |  |

| $\theta_{JA}$ Thermal Impedance                 |                                                                   |  |  |  |  |

| 16-Lead TSSOP                                   | 150.4°C/W                                                         |  |  |  |  |

| Lead Soldering                                  |                                                                   |  |  |  |  |

| Lead Temperature, Soldering (10 sec)            | 300℃                                                              |  |  |  |  |

| IR Reflow, Peak Temperature (<20 sec)           | 220℃                                                              |  |  |  |  |

| Pb-Free Soldering                               |                                                                   |  |  |  |  |

| Reflow, Peak Temperature                        | 260 (+0/−5)°C                                                     |  |  |  |  |

| Time at Peak Temperature                        | 20 sec to 40 sec                                                  |  |  |  |  |

| •                                               | ·                                                                 |  |  |  |  |

$<sup>^{1}</sup>$  Tested at  $-55^{\circ}$ C to  $+125^{\circ}$ C.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

Only one absolute maximum rating can be applied at any one time.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

$<sup>^2</sup>$  Overvoltages at INx, Sx, or Dx are clamped by internal diodes. Limit the current to the maximum ratings given. Tested at  $-55^\circ\text{C}$  to +125°C.

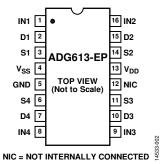

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 2. Pin Configuration

**Table 5. Pin Function Descriptions**

| Pin No. | Mnemonic | Description                                                                                                 |  |  |  |

|---------|----------|-------------------------------------------------------------------------------------------------------------|--|--|--|

| 1       | IN1      | Switch 1 Digital Control Input.                                                                             |  |  |  |

| 2       | D1       | Drain Terminal of Switch 1. This pin can be an input or output.                                             |  |  |  |

| 3       | S1       | Source Terminal of Switch 1. This pin can be an input or output.                                            |  |  |  |

| 4       | $V_{SS}$ | Most Negative Power Supply Terminal. Tie this pin to GND when using the device with single-supply voltages. |  |  |  |

| 5       | GND      | Ground (0 V) Reference.                                                                                     |  |  |  |

| 6       | S4       | Source Terminal of Switch 4. This pin can be an input or output.                                            |  |  |  |

| 7       | D4       | Drain Terminal of Switch 4. This pin can be an input or output.                                             |  |  |  |

| 8       | IN4      | witch 4 Digital Control Input.                                                                              |  |  |  |

| 9       | IN3      | Switch 3 Digital Control Input.                                                                             |  |  |  |

| 10      | D3       | Drain Terminal of Switch 3. This pin can be an input or output.                                             |  |  |  |

| 11      | S3       | Source Terminal of Switch 3. This pin can be an input or output.                                            |  |  |  |

| 12      | NIC      | Not Internally Connected.                                                                                   |  |  |  |

| 13      | $V_{DD}$ | Most Positive Power Supply Terminal.                                                                        |  |  |  |

| 14      | S2       | Source Terminal of Switch 2. This pin can be an input or output.                                            |  |  |  |

| 15      | D2       | Drain Terminal of Switch 2. This pin can be an input or output.                                             |  |  |  |

| 16      | IN2      | Switch 2 Digital Control Input.                                                                             |  |  |  |

#### Table 6. Truth Table

| Logic | S1 and S4 | S2 and S3 |

|-------|-----------|-----------|

| 0     | Off       | On        |

| _1    | On        | Off       |

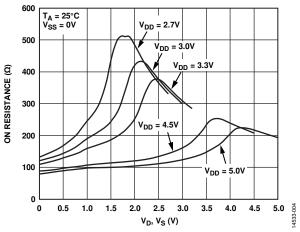

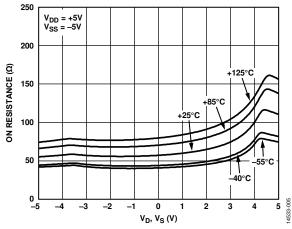

## TYPICAL PERFORMANCE CHARACTERISTICS

Figure 3. On Resistance vs. V<sub>D</sub>, V<sub>S</sub>; Dual Supplies

Figure 4. On Resistance vs. V<sub>D</sub>, V<sub>S</sub>; Single Supply

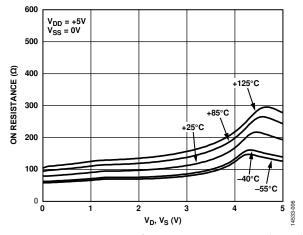

Figure 5. On Resistance vs.  $V_D$ ,  $V_S$  for Various Temperatures, Dual Supplies

Figure 6. On Resistance vs.  $V_D$ ,  $V_S$  for Various Temperatures, Single Supply

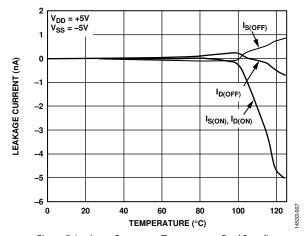

Figure 7. Leakage Current vs. Temperature, Dual Supplies

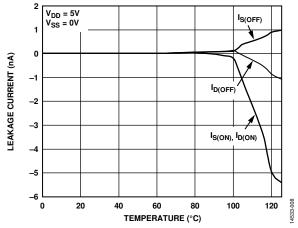

Figure 8. Leakage Current vs. Temperature, Single Supply

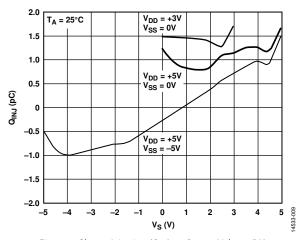

Figure 9. Charge Injection  $(Q_{INJ})$  vs. Source Voltage  $(V_S)$

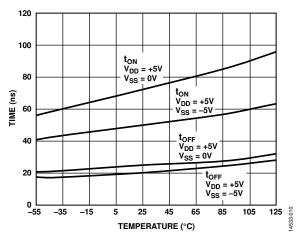

Figure 10.  $t_{ON}/t_{OFF}$  Times vs. Temperature

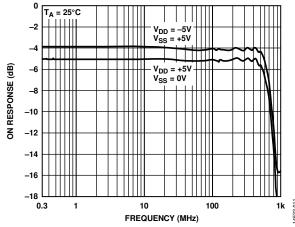

Figure 11. On Response vs. Frequency

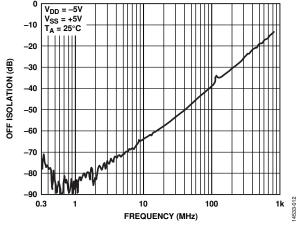

Figure 12. Off Isolation vs. Frequency

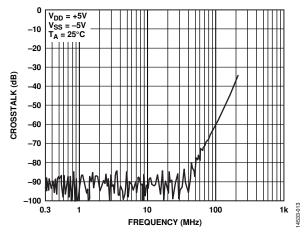

Figure 13. Crosstalk vs. Frequency

# **TEST CIRCUITS**

$V_S = V_D = V_D$

Figure 17. Switching Times

Figure 18. Break-Before-Make Time Delay

Figure 19. Charge Injection

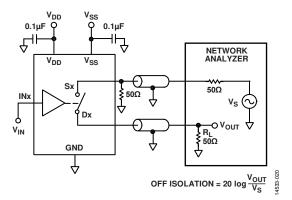

Figure 20. Off Isolation

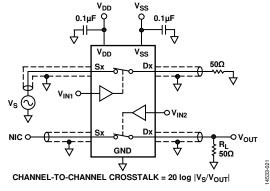

Figure 21. Channel-to-Channel Crosstalk

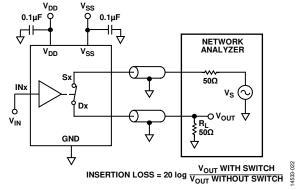

Figure 22. Bandwidth

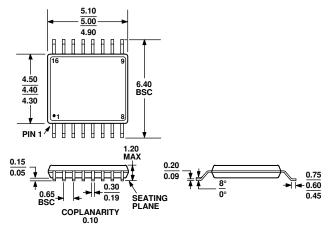

# **OUTLINE DIMENSIONS**

COMPLIANT TO JEDEC STANDARDS MO-153-AB

Figure 23. 16-Lead Thin Shrink Small Outline Package [TSSOP] (RU-16) Dimensions shown in millimeters

#### **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description                               | Package Option |

|--------------------|-------------------|---------------------------------------------------|----------------|

| ADG613SRUZ-EP      | –55℃ to +125℃     | 16-Lead Thin Shrink Small Outline Package [TSSOP] | RU-16          |

| ADG613SRUZ-EP-RL7  | –55℃ to +125℃     | 16-Lead Thin Shrink Small Outline Package [TSSOP] | RU-16          |

<sup>&</sup>lt;sup>1</sup> Z = RoHS Compliant Part.