32

# SH726A Group, SH726B Group

User's Manual: Hardware

Renesas 32-Bit RISC Microcomputer SuperH<sup>™</sup> RISC engine Family / SH7260 Series

SH726A R5S726A

SH726B R5S726B

#### Notice

- All information included in this document is current as of the date this document is issued. Such information, however, is

subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please

confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to

additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights

of third parties by or arising from the use of Renesas Electronics products or technical information described in this document.

No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights

of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application categorized as "Specific" without the prior written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics. The quality grade of each Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics data sheets or data books, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# **General Precautions on Handling of Product**

### 1. Treatment of NC Pins

Note: Do not connect anything to the NC pins.

The NC (not connected) pins are either not connected to any of the internal circuitry or are used as test pins or to reduce noise. If something is connected to the NC pins, the operation of the LSI is not guaranteed.

# 2. Treatment of Unused Input Pins

Note: Fix all unused input pins to high or low level.

Generally, the input pins of CMOS products are high-impedance input pins. If unused pins are in their open states, intermediate levels are induced by noise in the vicinity, a pass-through current flows internally, and a malfunction may occur.

# 3. Processing before Initialization

Note: When power is first supplied, the product's state is undefined.

The states of internal circuits are undefined until full power is supplied throughout the chip and a low level is input on the reset pin. During the period where the states are undefined, the register settings and the output state of each pin are also undefined. Design your system so that it does not malfunction because of processing while it is in this undefined state. For those products which have a reset function, reset the LSI immediately after the power supply has been turned on.

### 4. Prohibition of Access to Undefined or Reserved Addresses

Note: Access to undefined or reserved addresses is prohibited.

The undefined or reserved addresses may be used to expand functions, or test registers may have been be allocated to these addresses. Do not access these registers; the system's operation is not guaranteed if they are accessed.

# Configuration of This Manual

This manual comprises the following items:

- 1. General Precautions on Handling of Product

- 2. Configuration of This Manual

- 3 Preface

- 4. Contents

- 5 Overview

- 6. Description of Functional Modules

- CPU and System-Control Modules

- On-Chip Peripheral Modules

The configuration of the functional description of each module differs according to the module. However, the generic style includes the following items:

- i) Feature

- ii) Input/Output Pin

- iii) Register Description

- iv) Operation

- v) Usage Note

When designing an application system that includes this LSI, take notes into account. Each section includes notes in relation to the descriptions given, and usage notes are given, as required, as the final part of each section.

- 7. List of Registers

- 8. Electrical Characteristics

- 9. States and Handling of Pins

- 10. Appendix

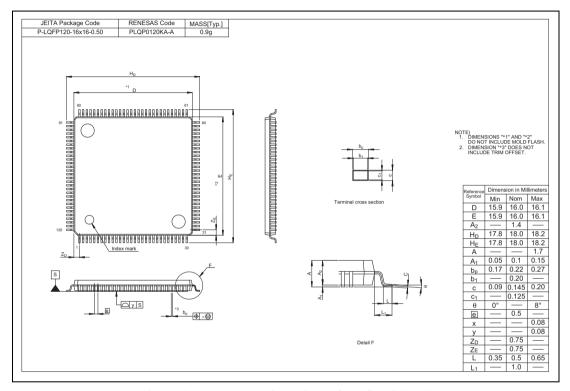

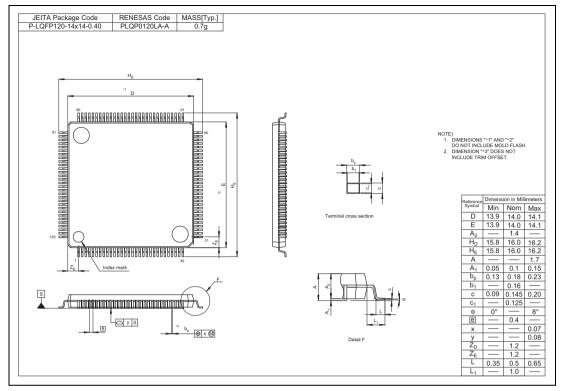

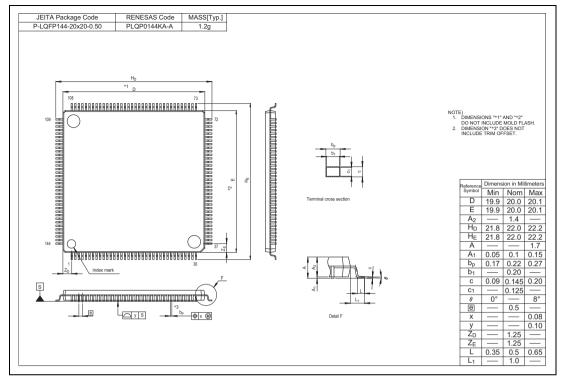

- Package Dimensions, etc.

- 11. Main Revisions and Additions in this Edition (only for revised versions)

The list of revisions is a summary of points that have been revised or added to earlier versions. This does not include all of the revised contents. For details, see the actual locations in this manual.

12. Index

# **Preface**

This LSI is an RISC (Reduced Instruction Set Computer) microcomputer which includes a Renesas-original RISC CPU as its core, and the peripheral functions required to configure a system.

Target Users: This manual was written for users who will be using this LSI in the design of

application systems. Target users are expected to understand the fundamentals of

electrical circuits, logical circuits, and microcomputers.

Objective: This manual was written to explain the hardware functions and electrical

characteristics of this LSI to the target users.

Refer to the SH-2A, SH2A-FPU Software Manual for a detailed description of the

instruction set.

Notes on reading this manual:

• In order to understand the overall functions of the chip

Read the manual according to the contents. This manual can be roughly categorized into parts

on the CPU, system control functions, peripheral functions and electrical characteristics.

• In order to understand the details of the CPU's functions

Read the SH-2A, SH2A-FPU Software Manual.

• In order to understand the details of a register when its name is known

Read the index that is the final part of the manual to find the page number of the entry on the register. The addresses, bits, and initial values of the registers are summarized in section 34, List of Registers.

# Description of Numbers and Symbols

Aspects of the notations for register names, bit names, numbers, and symbolic names in this manual are explained below.

#### (1) Overall notation

In descriptions involving the names of bits and bit fields within this manual, the modules and registers to which the bits belong may be clarified by giving the names in the forms "module name". "register name". "bit name" or "register name". "bit name".

#### (2) Register notation

The style "register name" "instance number" is used in cases where there is more than one instance of the same function or similar functions. [Example] CMCSR\_0: Indicates the CMCSR register for the compare-match timer of channel 0.

#### (3) Number notation

Binary numbers are given as B'nnnn (B' may be omitted if the number is obviously binary). hexadecimal numbers are given as H'nnnn or 0xnnnn, and decimal numbers are given as nnnn. B'11 or 11

[Examples] Binary:

Hexadecimal: H'EFA0 or 0xEFA0

Decimal: 1234

#### (4) Notation for active-low

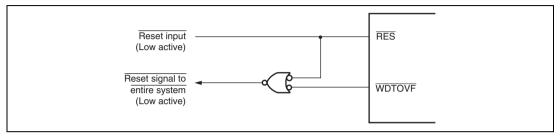

An overbar on the name indicates that a signal or pin is active-low. [Example] WDTOVF

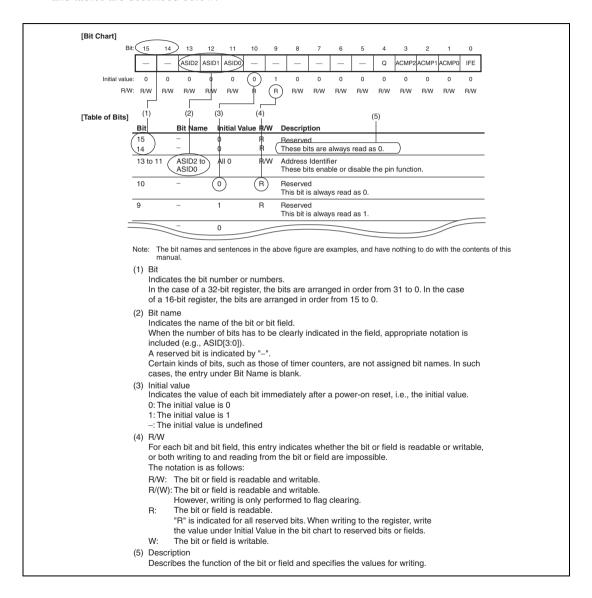

Note: The bit names and sentences in the above figure are examples and do not refer to specific data in this manual.

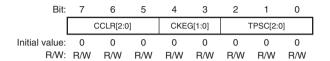

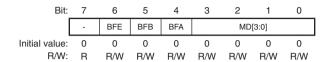

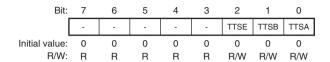

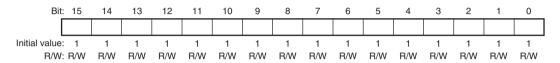

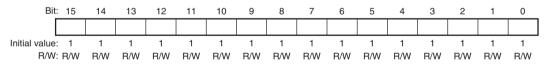

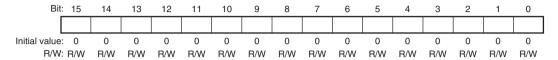

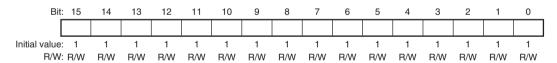

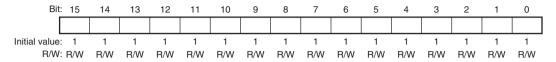

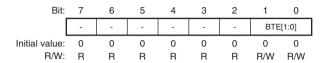

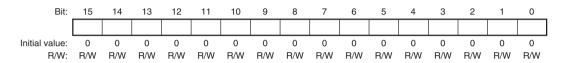

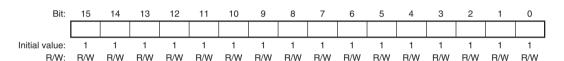

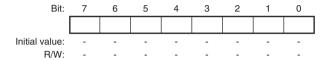

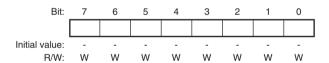

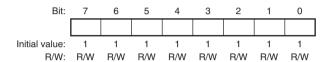

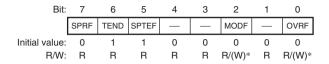

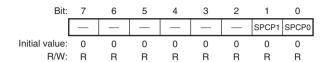

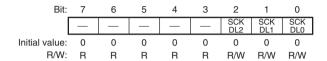

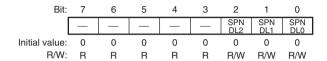

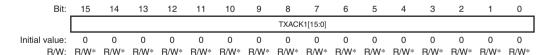

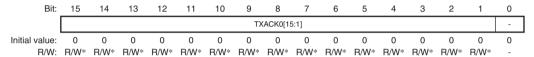

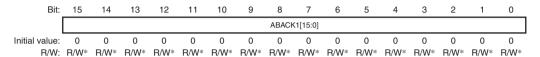

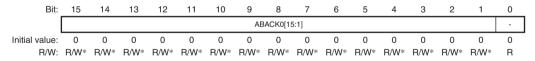

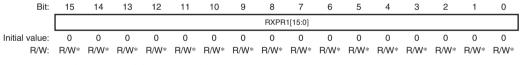

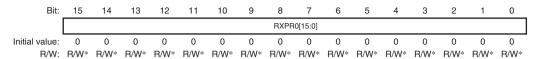

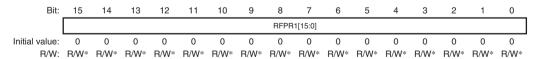

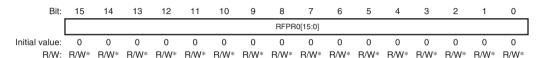

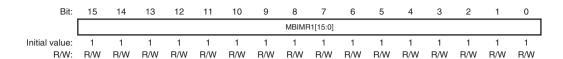

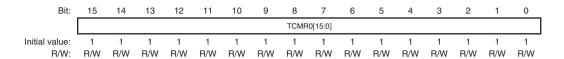

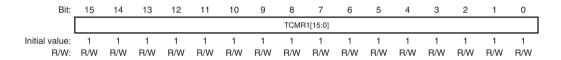

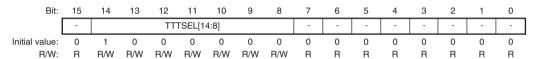

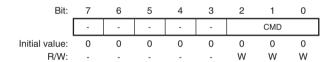

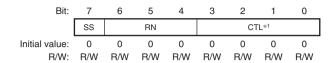

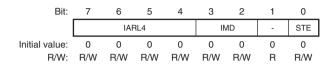

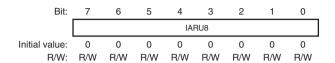

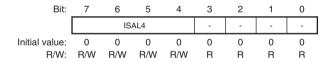

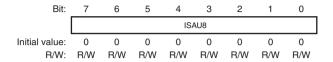

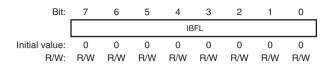

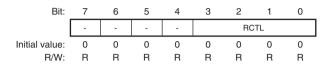

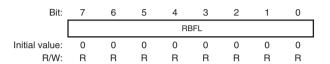

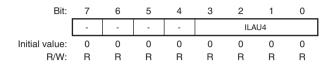

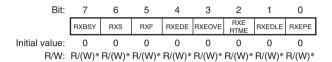

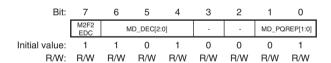

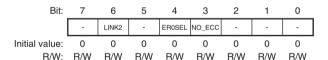

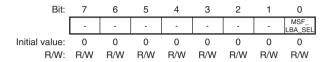

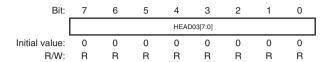

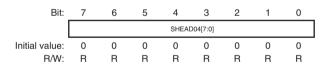

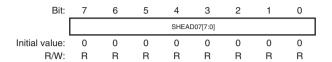

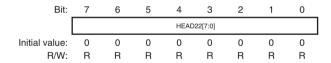

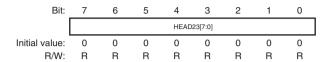

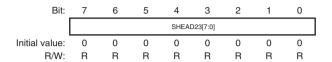

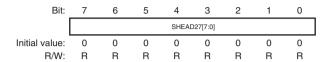

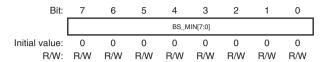

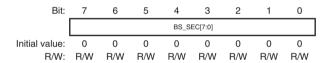

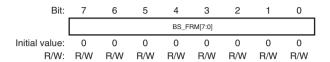

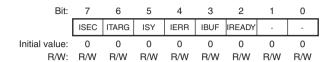

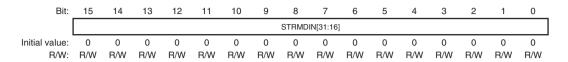

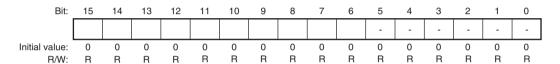

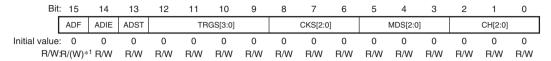

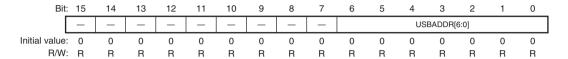

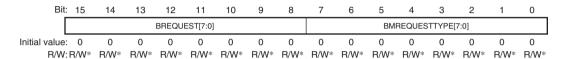

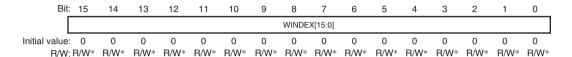

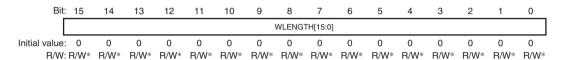

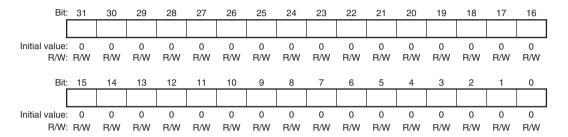

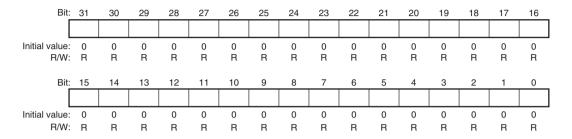

### Description of Registers

Each register description includes a bit chart, illustrating the arrangement of bits, and a table of bits, describing the meanings of the bit settings. The standard format and notation for bit charts and tables are described below.

All trademarks and registered trademarks are the property of their respective owners.

# Contents

| Section | on 1 Ove             | rview                                 | 1    |  |  |

|---------|----------------------|---------------------------------------|------|--|--|

| 1.1     | SH726A/726B Features |                                       |      |  |  |

| 1.2     | Product Lineup       |                                       |      |  |  |

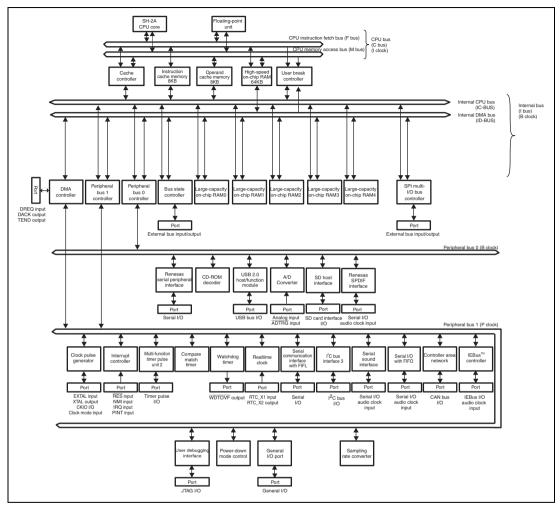

| 1.3     | Block Dia            | agramagram                            | . 12 |  |  |

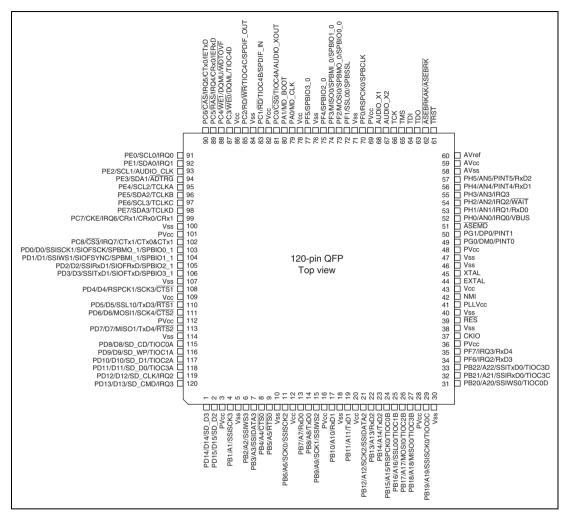

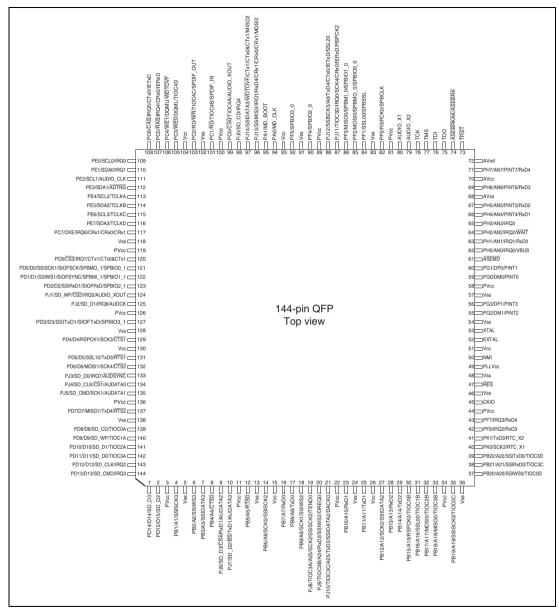

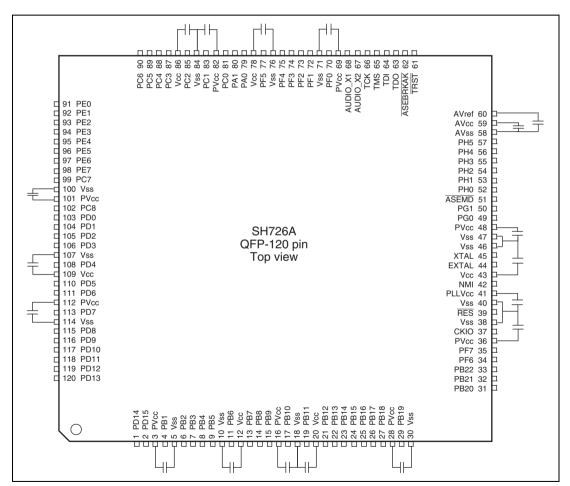

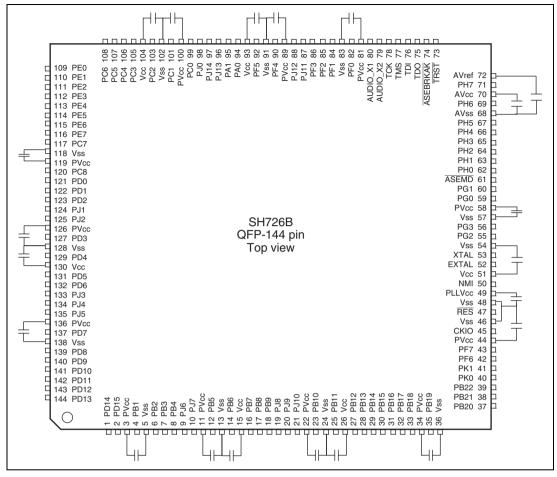

| 1.4     | Pin Assig            | nment                                 | . 13 |  |  |

| 1.5     | Pin Funct            | tions                                 | . 15 |  |  |

| 1.6     | List of Pi           | ns                                    | . 23 |  |  |

| C4:     | 2 CDI                | т                                     | 27   |  |  |

|         |                      | J                                     |      |  |  |

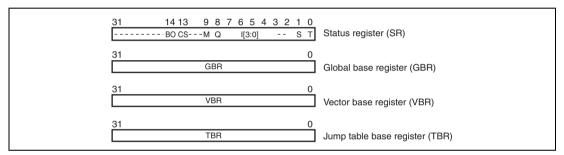

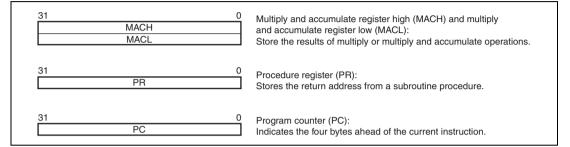

| 2.1     | _                    | Configuration                         |      |  |  |

|         | 2.1.1                | General Registers                     |      |  |  |

|         | 2.1.2                | Control Registers                     |      |  |  |

|         | 2.1.3                | System Registers                      |      |  |  |

|         | 2.1.4                | Register Banks                        |      |  |  |

|         | 2.1.5                | Initial Values of Registers           |      |  |  |

| 2.2     |                      | mats                                  |      |  |  |

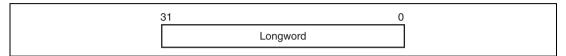

|         | 2.2.1                | Data Format in Registers              |      |  |  |

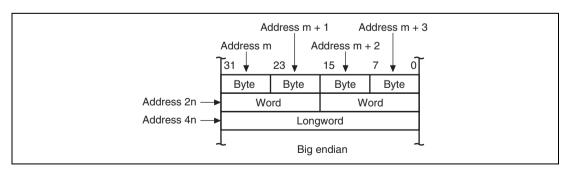

|         | 2.2.2                | Data Formats in Memory                |      |  |  |

|         | 2.2.3                | Immediate Data Format                 |      |  |  |

| 2.3     | Instruction Features |                                       |      |  |  |

|         | 2.3.1                | RISC-Type Instruction Set             |      |  |  |

|         | 2.3.2                | Addressing Modes                      |      |  |  |

|         | 2.3.3                | Instruction Format                    | . 53 |  |  |

| 2.4     | Instructio           | on Set                                | . 57 |  |  |

|         | 2.4.1                | Instruction Set by Classification     | . 57 |  |  |

|         | 2.4.2                | Data Transfer Instructions            | . 63 |  |  |

|         | 2.4.3                | Arithmetic Operation Instructions     | . 67 |  |  |

|         | 2.4.4                | Logic Operation Instructions          | . 70 |  |  |

|         | 2.4.5                | Shift Instructions                    | .71  |  |  |

|         | 2.4.6                | Branch Instructions                   | . 72 |  |  |

|         | 2.4.7                | System Control Instructions           | . 73 |  |  |

|         | 2.4.8                | Floating-Point Operation Instructions | . 75 |  |  |

|         | 2.4.9                | FPU-Related CPU Instructions          | . 77 |  |  |

|         | 2.4.10               | Bit Manipulation Instructions         | . 78 |  |  |

| 2.5     | Processing States    |                                       |      |  |  |

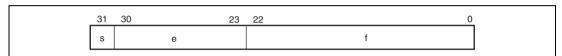

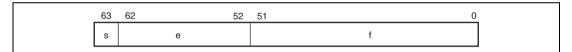

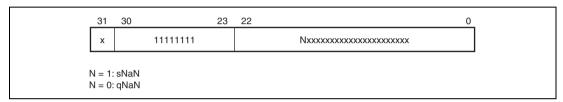

| Sect | ion 3 Fl  | oating-Point Unit (FPU)                                        | 81  |

|------|-----------|----------------------------------------------------------------|-----|

| 3.1  |           | S                                                              |     |

| 3.2  | Data Fo   | ormats                                                         | 82  |

|      | 3.2.1     | Floating-Point Format                                          | 82  |

|      | 3.2.2     | Non-Numbers (NaN)                                              | 85  |

|      | 3.2.3     | Denormalized Numbers                                           | 86  |

| 3.3  | Registe   | r Descriptions                                                 | 87  |

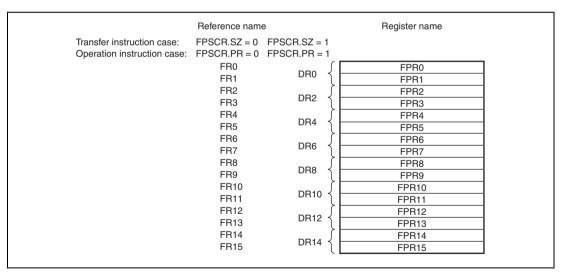

|      | 3.3.1     | Floating-Point Registers                                       | 87  |

|      | 3.3.2     | Floating-Point Status/Control Register (FPSCR)                 | 88  |

|      | 3.3.3     | Floating-Point Communication Register (FPUL)                   | 90  |

| 3.4  | Roundi    | ng                                                             | 91  |

| 3.5  | FPU Ex    | cceptions                                                      | 92  |

|      | 3.5.1     | FPU Exception Sources                                          | 92  |

|      | 3.5.2     | FPU Exception Handling                                         | 92  |

| Sect | ion 4 Bo  | oot Mode                                                       | 95  |

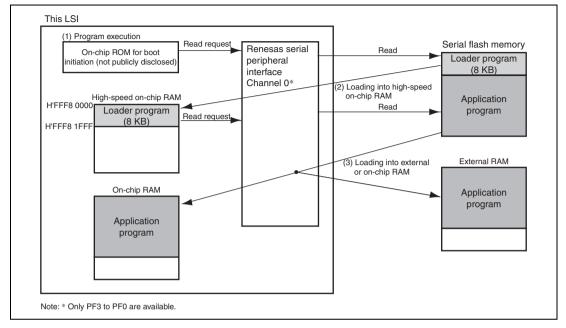

| 4.1  | Feature   | S                                                              | 95  |

| 4.2  | Boot M    | ode and Pin Function Setting                                   | 95  |

| 4.3  | Operation |                                                                |     |

|      | 4.3.1     | Boot Mode 0                                                    | 96  |

|      | 4.3.2     | Boot Mode 1                                                    | 96  |

| 4.4  | Notes     |                                                                | 98  |

|      | 4.4.1     | Boot Related Pins                                              | 98  |

| Sect | ion 5 Cl  | ock Pulse Generator                                            | 99  |

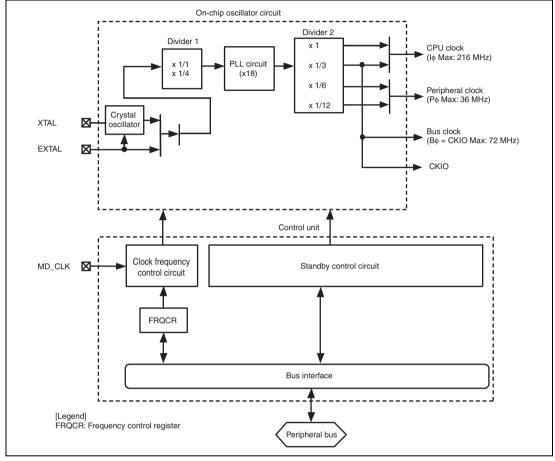

| 5.1  | Feature   | S                                                              | 99  |

| 5.2  | Input/C   | Output Pins                                                    | 102 |

| 5.3  | Clock (   | Operating Modes                                                | 103 |

| 5.4  | Registe   | r Descriptions                                                 | 105 |

|      | 5.4.1     | Frequency Control Register (FRQCR)                             | 105 |

| 5.5  | Changi    | ng the Frequency                                               | 108 |

|      | 5.5.1     | Changing the Division Ratio                                    | 108 |

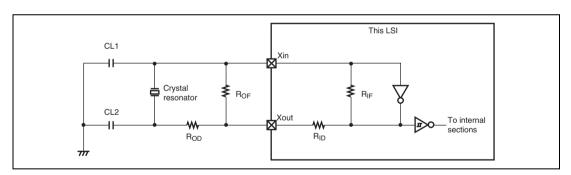

| 5.6  | Usage of  | of the Clock Pins                                              | 109 |

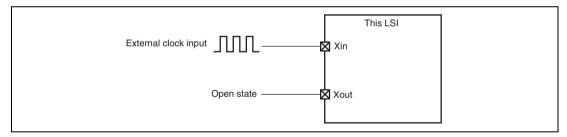

|      | 5.6.1     | In the Case of Inputting an External Clock                     | 109 |

|      | 5.6.2     | In the Case of Using a Crystal Resonator                       | 110 |

|      | 5.6.3     | In the Case of Not Using the Clock Pin                         | 110 |

| 5.7  | Oscillat  | tion Stabilizing Time                                          | 111 |

|      | 5.7.1     | Oscillation Stabilizing Time of the On-chip Crystal Oscillator | 111 |

|      | 5.7.2     | Oscillation Stabilizing Time of the PLL circuit                |     |

| 5.8  | Notes o   | on Board Design                                                | 112 |

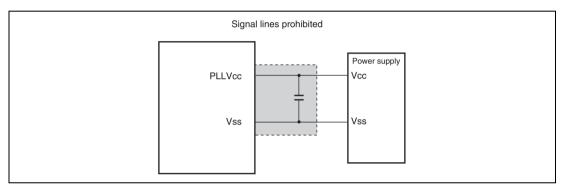

|       | 5.8.1     | Note on Using a PLL Oscillation Circuit                               | 112  |

|-------|-----------|-----------------------------------------------------------------------|------|

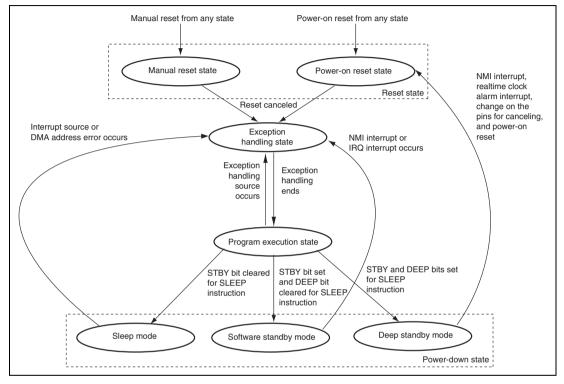

| Secti | on 6 Exc  | ception Handling                                                      | .113 |

| 6.1   |           | W                                                                     |      |

|       | 6.1.1     | Types of Exception Handling and Priority                              | 113  |

|       | 6.1.2     | Exception Handling Operations                                         | 114  |

|       | 6.1.3     | Exception Handling Vector Table                                       | 116  |

| 6.2   | Resets    |                                                                       | 119  |

|       | 6.2.1     | Input/Output Pins                                                     | 119  |

|       | 6.2.2     | Types of Reset                                                        | 119  |

|       | 6.2.3     | Power-On Reset                                                        | 121  |

|       | 6.2.4     | Manual Reset                                                          | 122  |

| 6.3   | Address   | Errors                                                                | 124  |

|       | 6.3.1     | Address Error Sources                                                 | 124  |

|       | 6.3.2     | Address Error Exception Handling                                      | 125  |

| 6.4   | Register  | Bank Errors                                                           | 125  |

|       | 6.4.1     | Register Bank Error Sources                                           | 125  |

|       | 6.4.2     | Register Bank Error Exception Handling                                | 126  |

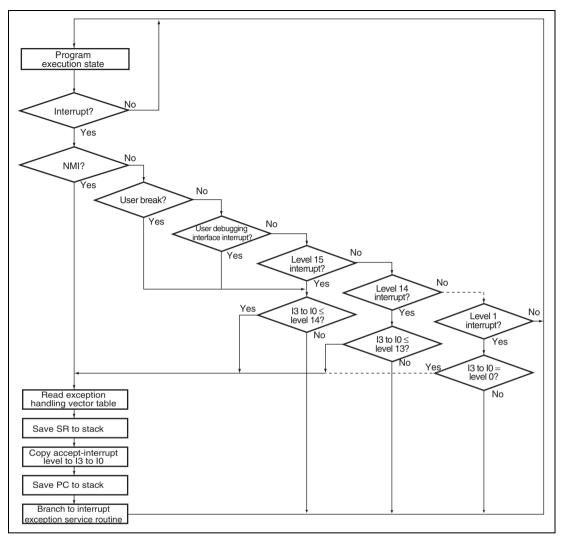

| 6.5   | Interrupt | S                                                                     | 126  |

|       | 6.5.1     | Interrupt Sources                                                     | 126  |

|       | 6.5.2     | Interrupt Priority Level                                              | 127  |

|       | 6.5.3     | Interrupt Exception Handling                                          | 128  |

| 6.6   | Exceptio  | ons Triggered by Instructions                                         | 129  |

|       | 6.6.1     | Types of Exceptions Triggered by Instructions                         | 129  |

|       | 6.6.2     | Trap Instructions                                                     | 130  |

|       | 6.6.3     | Slot Illegal Instructions                                             | 130  |

|       | 6.6.4     | General Illegal Instructions                                          | 131  |

|       | 6.6.5     | Integer Division Exceptions                                           | 131  |

|       | 6.6.6     | FPU Exceptions                                                        |      |

| 6.7   | When Ex   | xception Sources Are Not Accepted                                     | 133  |

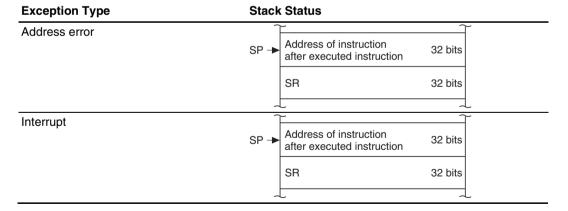

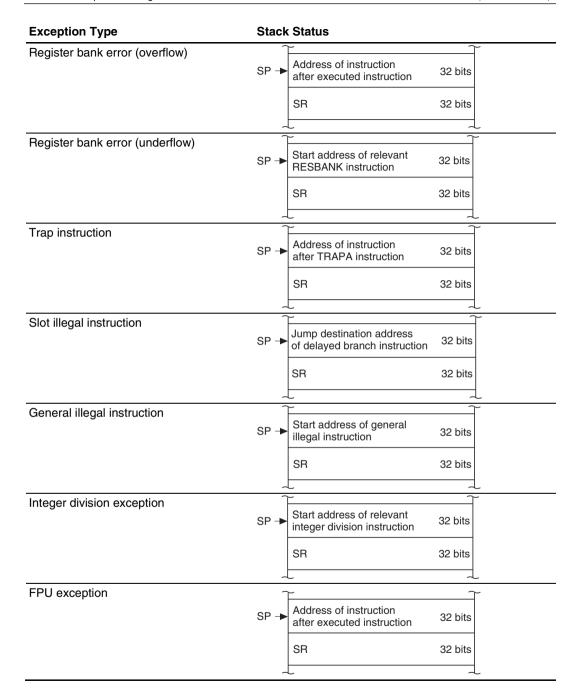

| 6.8   | Stack Sta | atus after Exception Handling Ends                                    | 133  |

| 6.9   | Usage N   | otes                                                                  | 135  |

|       | 6.9.1     | Value of Stack Pointer (SP)                                           | 135  |

|       | 6.9.2     | Value of Vector Base Register (VBR)                                   |      |

|       | 6.9.3     | Address Errors Caused by Stacking of Address Error Exception Handling | 135  |

|       | 6.9.4     | Note before Exception Handling Begins Running                         | 136  |

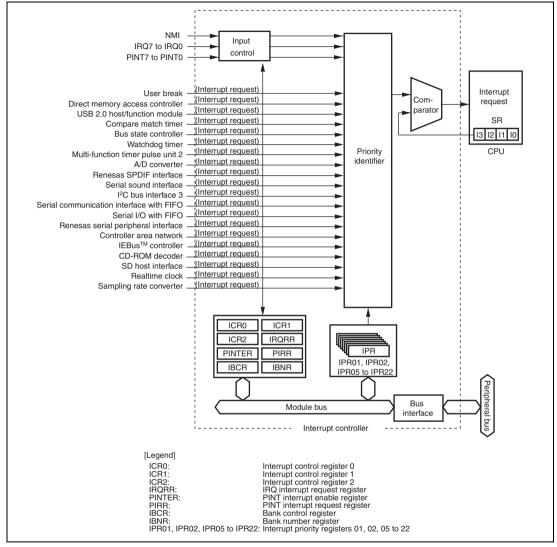

| Secti | on 7 Inte | errupt Controller                                                     | .139 |

| 7.1   |           |                                                                       |      |

| 7.2   | Input/Ou  | ıtput Pins                                                            | 141  |

| 7.3   | Registe                                      | er Descriptions                                                         | 142 |

|-------|----------------------------------------------|-------------------------------------------------------------------------|-----|

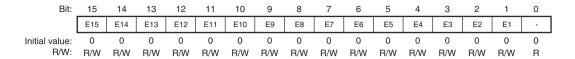

|       | 7.3.1                                        | Interrupt Priority Registers 01, 02, 05 to 22                           |     |

|       |                                              | (IPR01, IPR02, IPR05 to IPR22)                                          | 144 |

|       | 7.3.2                                        | Interrupt Control Register 0 (ICR0)                                     | 146 |

|       | 7.3.3                                        | Interrupt Control Register 1 (ICR1)                                     | 148 |

|       | 7.3.4                                        | Interrupt Control Register 2 (ICR2)                                     | 149 |

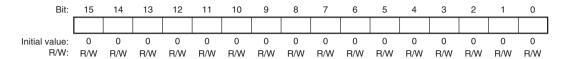

|       | 7.3.5                                        | IRQ Interrupt Request Register (IRQRR)                                  | 150 |

|       | 7.3.6                                        | PINT Interrupt Enable Register (PINTER)                                 | 151 |

|       | 7.3.7                                        | PINT Interrupt Request Register (PIRR)                                  | 152 |

|       | 7.3.8                                        | Bank Control Register (IBCR)                                            | 153 |

|       | 7.3.9                                        | Bank Number Register (IBNR)                                             | 154 |

| 7.4   | Interruj                                     | pt Sources                                                              | 155 |

|       | 7.4.1                                        | NMI Interrupt                                                           | 155 |

|       | 7.4.2                                        | User Break Interrupt                                                    | 156 |

|       | 7.4.3                                        | User Debugging Interface Interrupt                                      | 156 |

|       | 7.4.4                                        | IRQ Interrupts                                                          | 156 |

|       | 7.4.5                                        | PINT Interrupts                                                         | 157 |

|       | 7.4.6                                        | On-Chip Peripheral Module Interrupts                                    | 158 |

| 7.5   | Interruj                                     | pt Exception Handling Vector Table and Priority                         | 159 |

| 7.6   | Operation                                    |                                                                         |     |

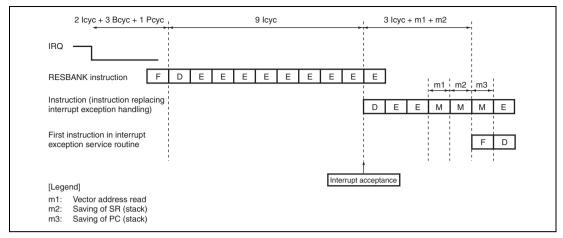

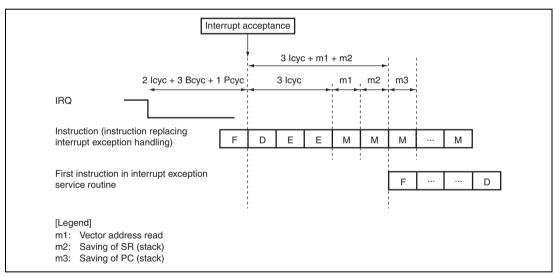

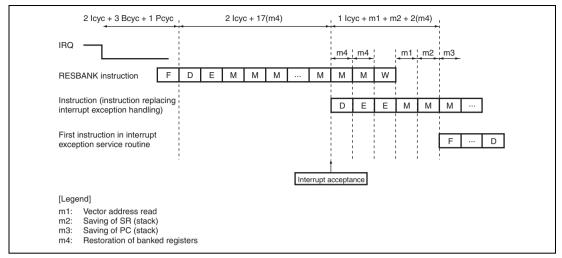

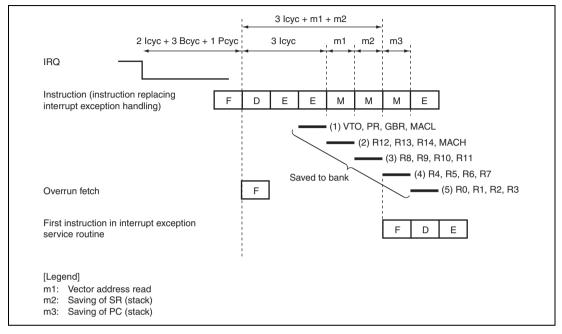

|       | 7.6.1                                        | Interrupt Operation Sequence                                            | 173 |

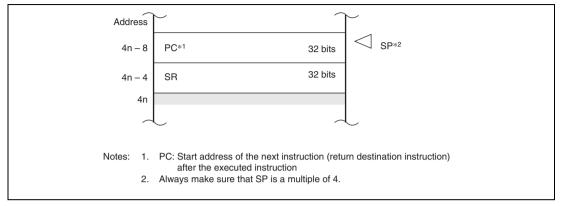

|       | 7.6.2                                        | Stack after Interrupt Exception Handling                                | 176 |

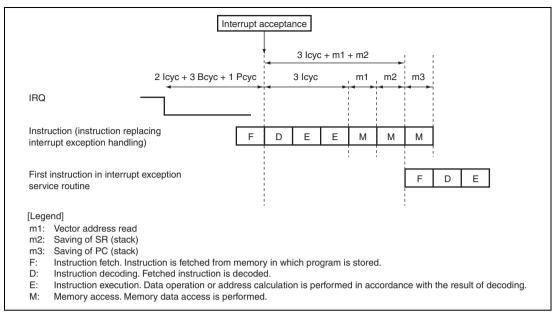

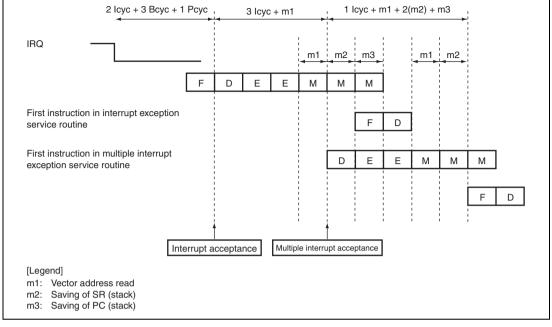

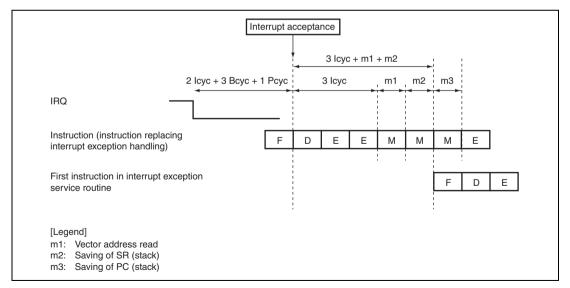

| 7.7   | Interruj                                     | pt Response Time                                                        | 177 |

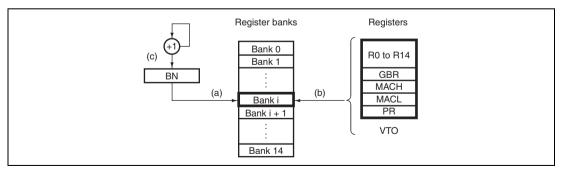

| 7.8   | Register Banks                               |                                                                         |     |

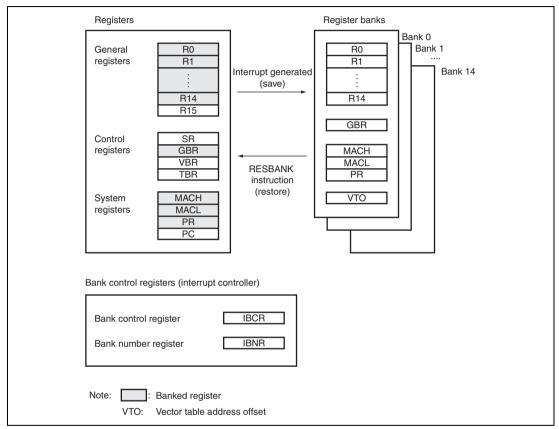

|       | 7.8.1                                        | Banked Register and Input/Output of Banks                               | 184 |

|       | 7.8.2                                        | Bank Save and Restore Operations                                        | 184 |

|       | 7.8.3                                        | Save and Restore Operations after Saving to All Banks                   | 186 |

|       | 7.8.4                                        | Register Bank Exception                                                 | 187 |

|       | 7.8.5                                        | Register Bank Error Exception Handling                                  | 187 |

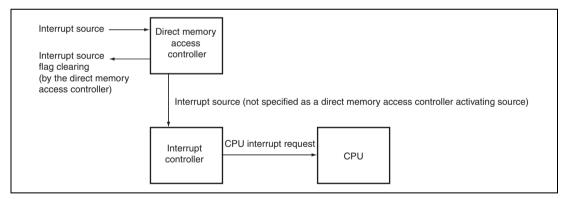

| 7.9   | Data Transfer with Interrupt Request Signals |                                                                         |     |

|       | 7.9.1                                        | Handling Interrupt Request Signals as Sources for CPU Interrupt but Not |     |

|       |                                              | Direct Memory Access Controller Activating                              | 189 |

|       | 7.9.2                                        | Handling Interrupt Request Signals as Sources for Activating Direct     |     |

|       |                                              | Memory Access Controller but Not CPU Interrupt                          | 189 |

| 7.10  | Usage 1                                      | Note                                                                    | 190 |

|       | 7.10.1                                       | Timing to Clear an Interrupt Source                                     | 190 |

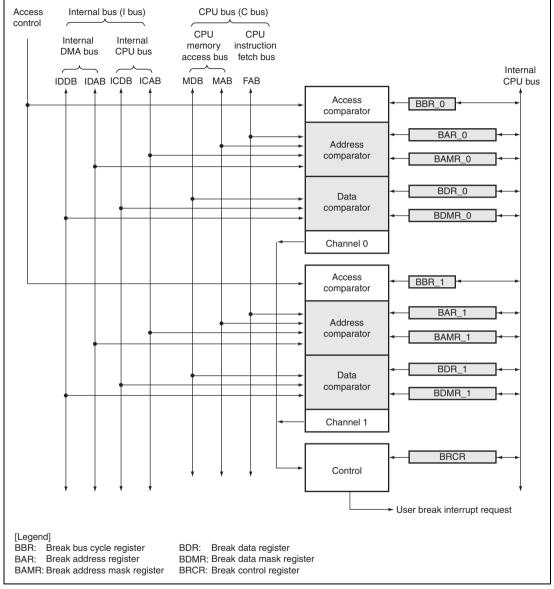

| Secti | on 8 Us                                      | ser Break Controller                                                    | 191 |

| 8.1   | Feature                                      | s                                                                       | 191 |

| 8.2   | Registe                                      | or Descriptions                                                         | 103 |

|      | 8.2.1                 | Break Address Register (BAR)                                     | 194 |

|------|-----------------------|------------------------------------------------------------------|-----|

|      | 8.2.2                 | Break Address Mask Register (BAMR)                               | 195 |

|      | 8.2.3                 | Break Data Register (BDR)                                        | 196 |

|      | 8.2.4                 | Break Data Mask Register (BDMR)                                  | 197 |

|      | 8.2.5                 | Break Bus Cycle Register (BBR)                                   | 198 |

|      | 8.2.6                 | Break Control Register (BRCR)                                    | 201 |

| 8.3  | Operati               | on                                                               | 203 |

|      | 8.3.1                 | Flow of the User Break Operation                                 | 203 |

|      | 8.3.2                 | Break on Instruction Fetch Cycle                                 | 204 |

|      | 8.3.3                 | Break on Data Access Cycle                                       | 205 |

|      | 8.3.4                 | Value of Saved Program Counter                                   | 206 |

|      | 8.3.5                 | Usage Examples                                                   | 207 |

| 8.4  | Usage l               | Notes                                                            | 210 |

| Sect | ion 9 Ca              | iche                                                             | 211 |

| 9.1  |                       | S                                                                |     |

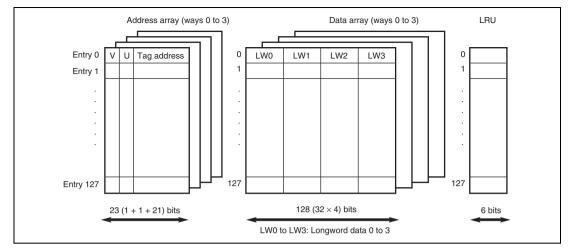

|      | 9.1.1                 | Cache Structure                                                  |     |

| 9.2  | Register Descriptions |                                                                  |     |

|      | 9.2.1                 | Cache Control Register 1 (CCR1)                                  |     |

|      | 9.2.2                 | Cache Control Register 2 (CCR2)                                  |     |

| 9.3  | Operation             |                                                                  |     |

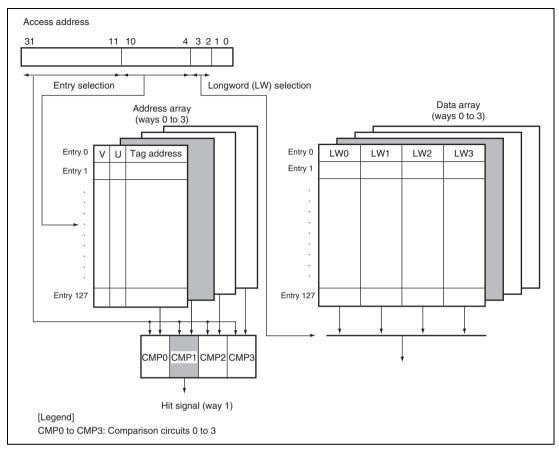

|      | 9.3.1                 | Searching Cache                                                  |     |

|      | 9.3.2                 | Read Access                                                      |     |

|      | 9.3.3                 | Prefetch Operation (Only for Operand Cache)                      |     |

|      | 9.3.4                 | Write Operation (Only for Operand Cache)                         |     |

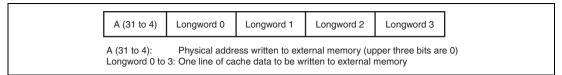

|      | 9.3.5                 | Write-Back Buffer (Only for Operand Cache)                       | 223 |

|      | 9.3.6                 | Coherency of Cache and External Memory or Large-Capacity On-Chip |     |

|      |                       | RAM                                                              |     |

| 9.4  |                       | y-Mapped Cache                                                   |     |

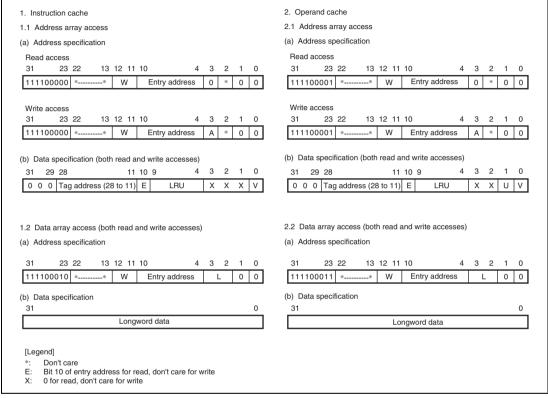

|      | 9.4.1                 | Address Array                                                    |     |

|      | 9.4.2                 | Data Array                                                       |     |

|      | 9.4.3                 | Usage Examples                                                   |     |

|      | 9.4.4                 | Usage Notes                                                      | 231 |

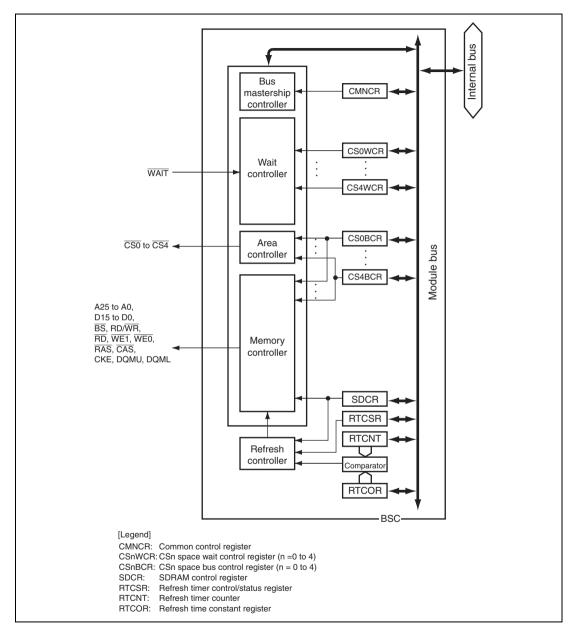

| Sect | ion 10 B              | Bus State Controller                                             | 233 |

| 10.1 | Feature               | s                                                                | 233 |

| 10.2 | Input/O               | output Pins                                                      | 236 |

| 10.3 | Area O                | verview                                                          | 237 |

|      | 10 3 1                | Address Man                                                      | 237 |

|       | 10.3.2    | Data Bus Width and Endian Specification for Each Area Depending on |     |

|-------|-----------|--------------------------------------------------------------------|-----|

|       |           | Boot Mode and Settings of Pins Related to This Module              | 239 |

| 10.4  | Register  | Descriptions                                                       | 241 |

|       | 10.4.1    | Common Control Register (CMNCR)                                    | 242 |

|       | 10.4.2    | CSn Space Bus Control Register (CSnBCR) (n = 0 to 4)               | 245 |

|       | 10.4.3    | CSn Space Wait Control Register (CSnWCR) (n = 0 to 4)              | 250 |

|       | 10.4.4    | SDRAM Control Register (SDCR)                                      | 272 |

|       | 10.4.5    | Refresh Timer Control/Status Register (RTCSR)                      | 276 |

|       | 10.4.6    | Refresh Timer Counter (RTCNT)                                      | 278 |

|       | 10.4.7    | Refresh Time Constant Register (RTCOR)                             | 279 |

| 10.5  | Operation | on                                                                 | 280 |

|       | 10.5.1    | Endian/Access Size and Data Alignment                              | 280 |

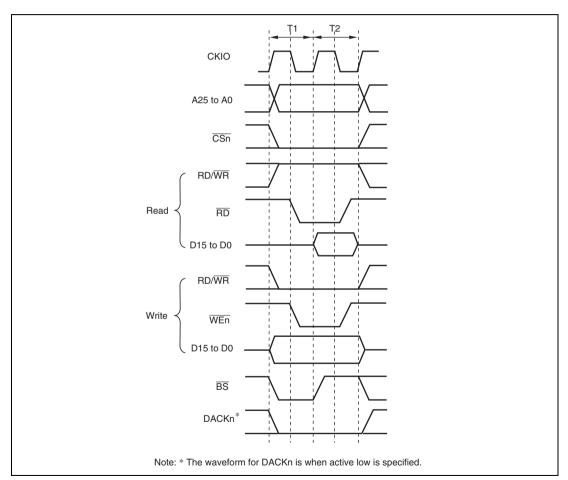

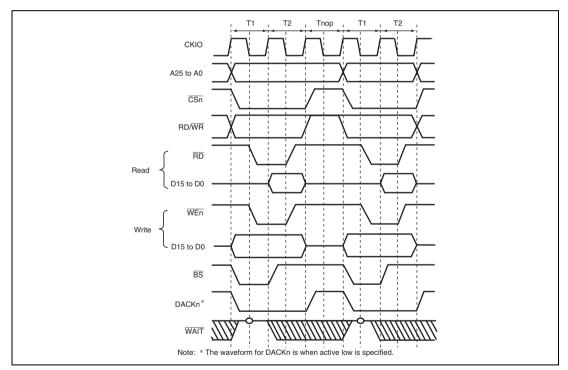

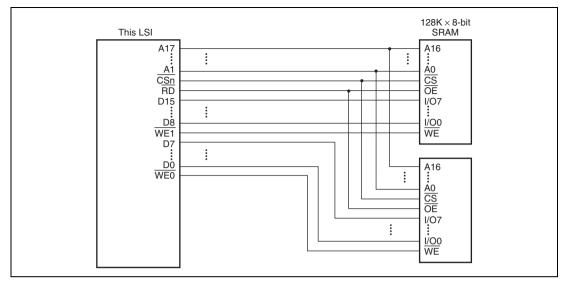

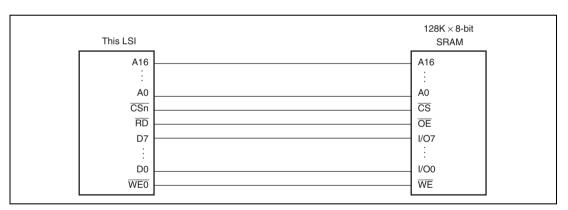

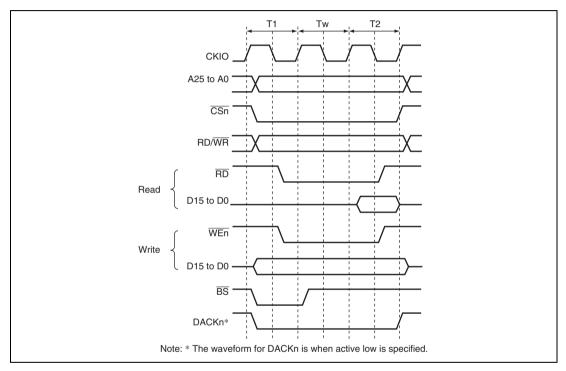

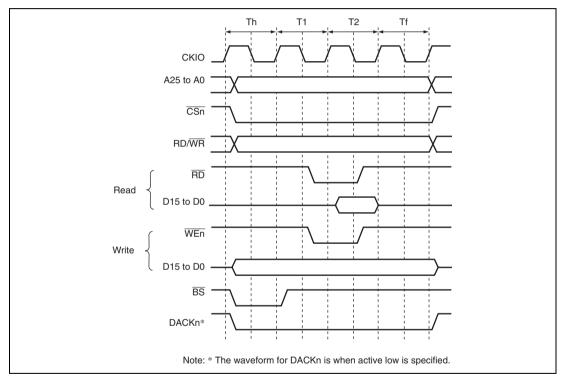

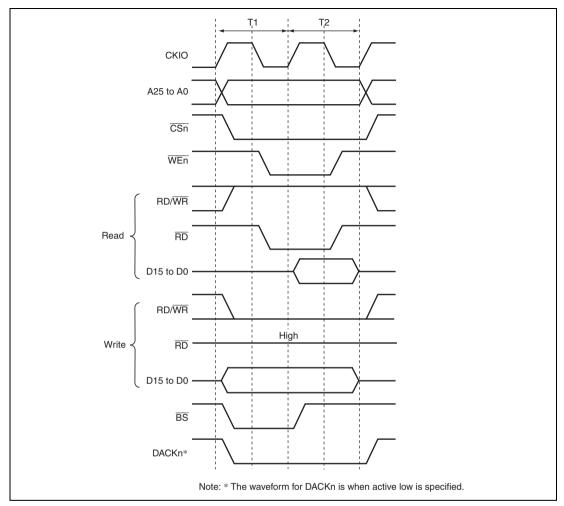

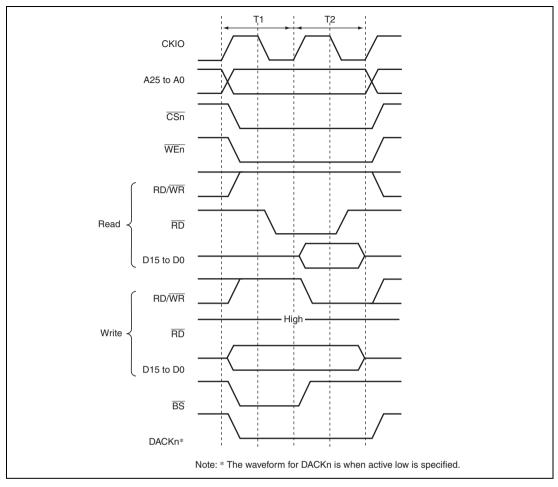

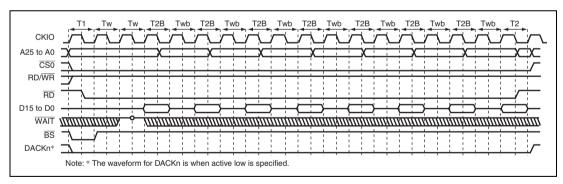

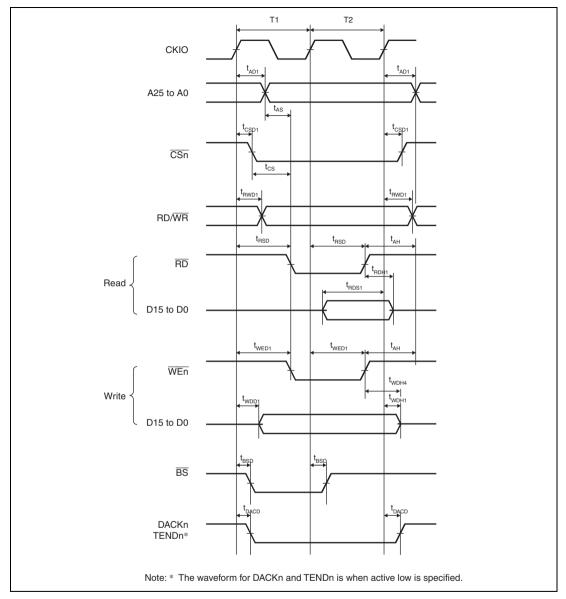

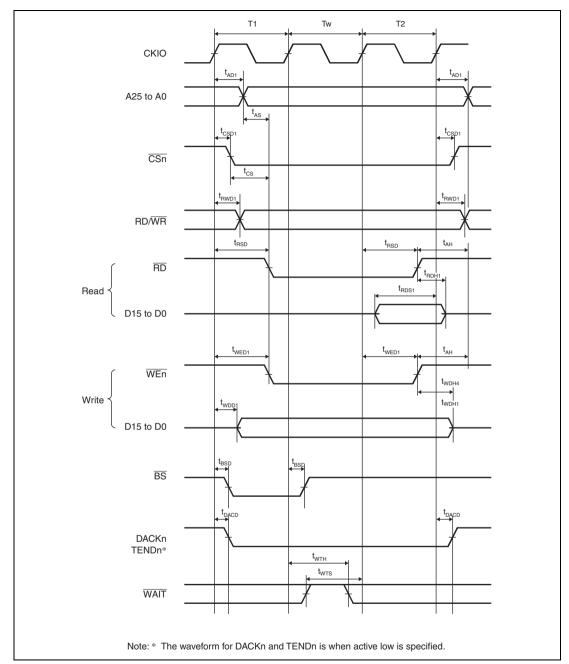

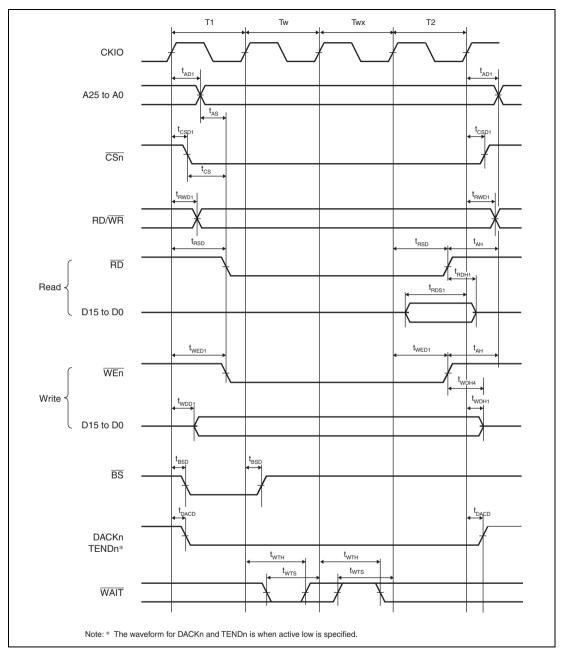

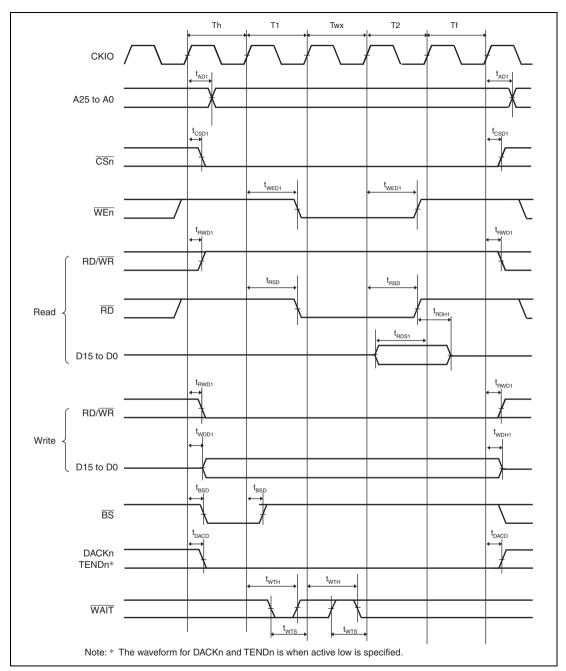

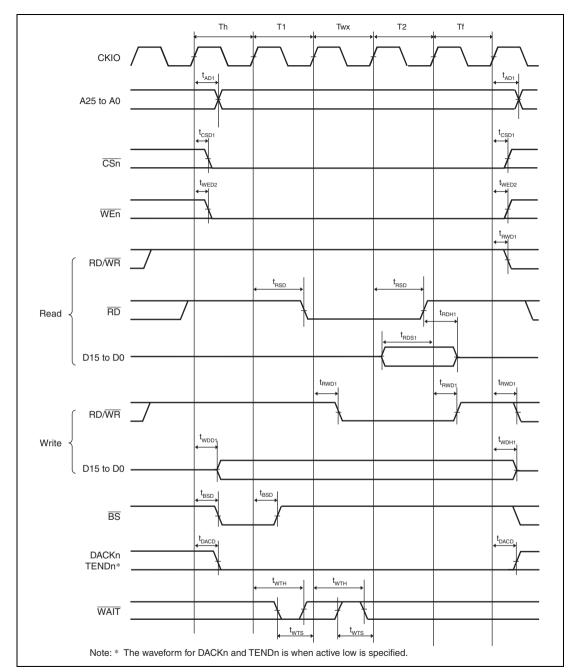

|       | 10.5.2    | Normal Space Interface                                             | 283 |

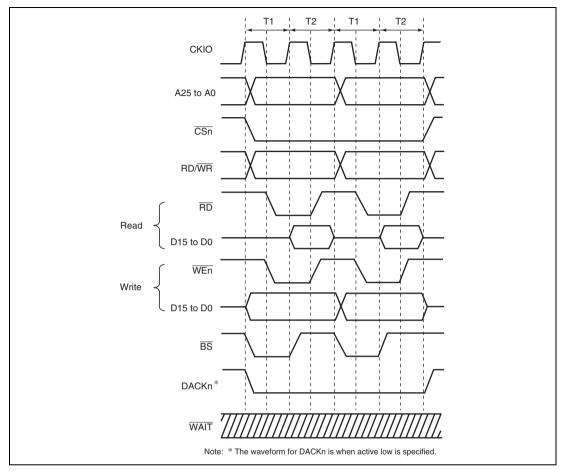

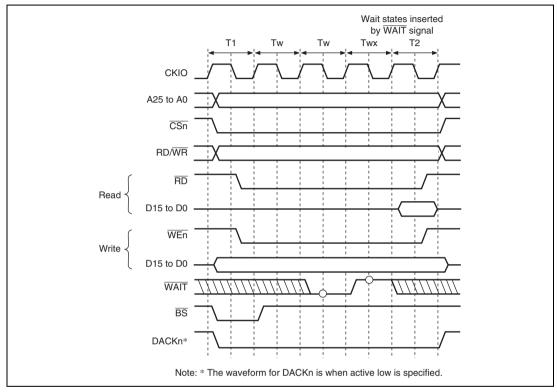

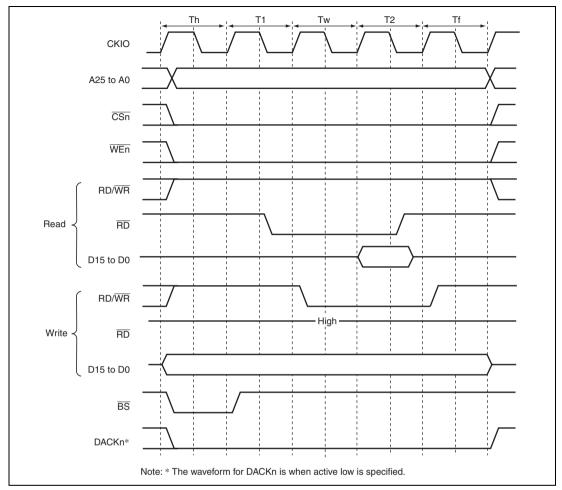

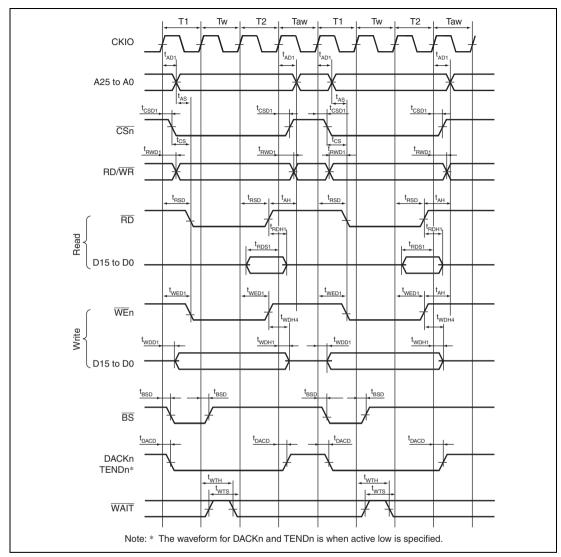

|       | 10.5.3    | Access Wait Control                                                | 287 |

|       | 10.5.4    | CSn Assert Period Expansion                                        | 289 |

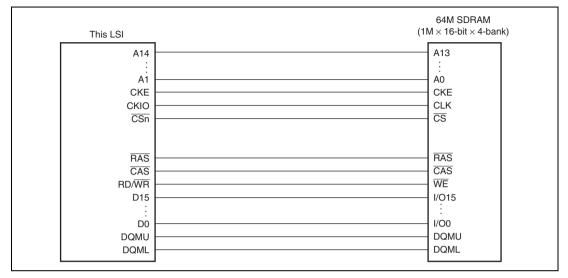

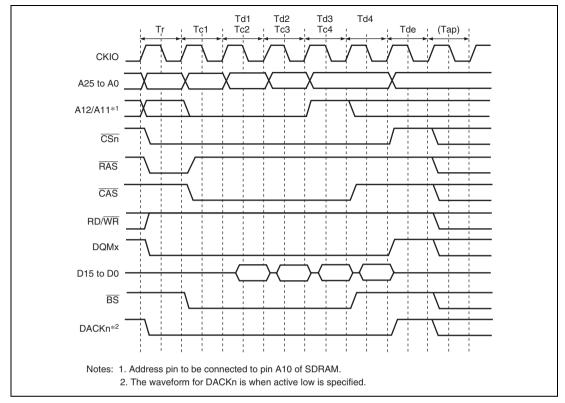

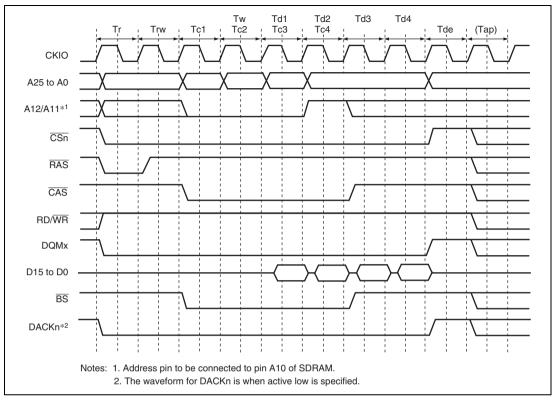

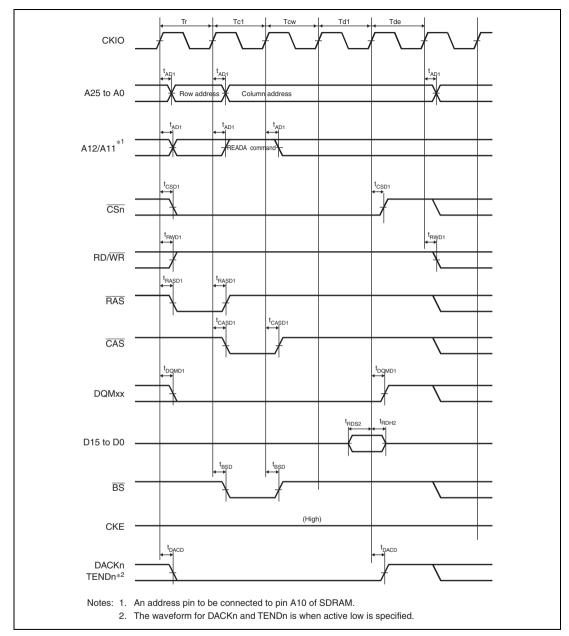

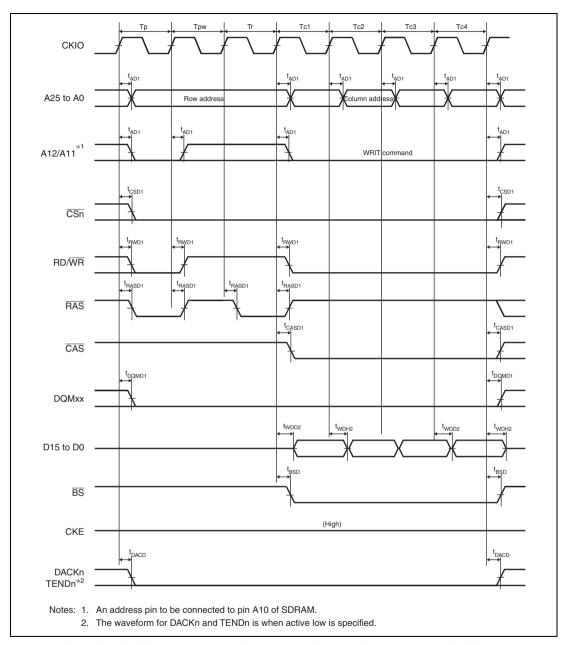

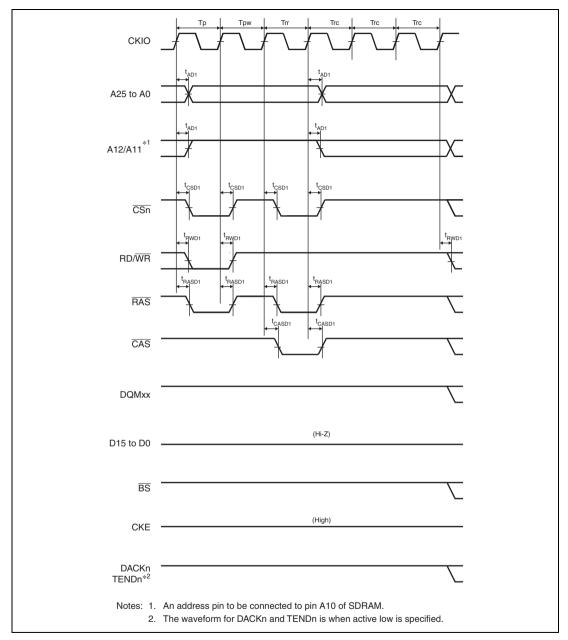

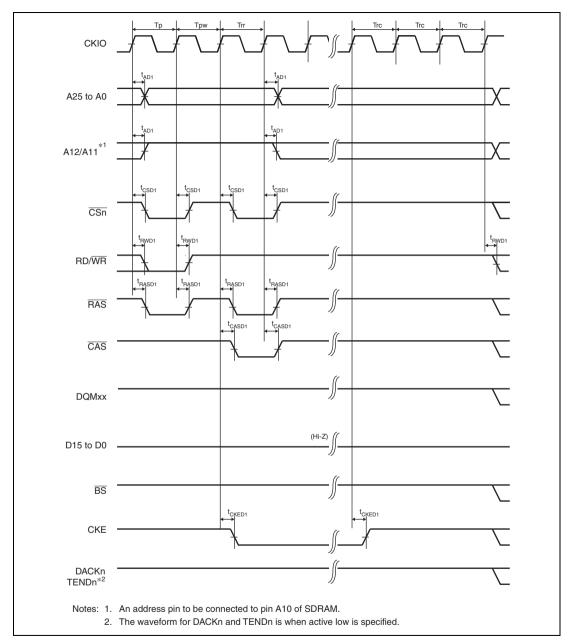

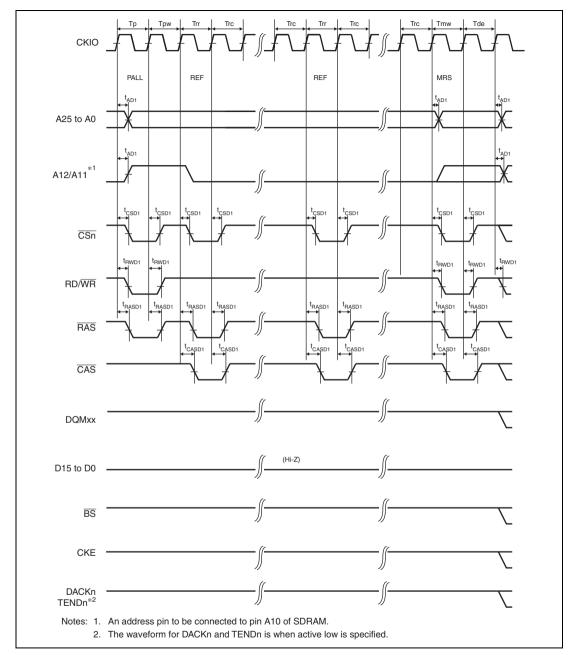

|       | 10.5.5    | SDRAM Interface                                                    | 290 |

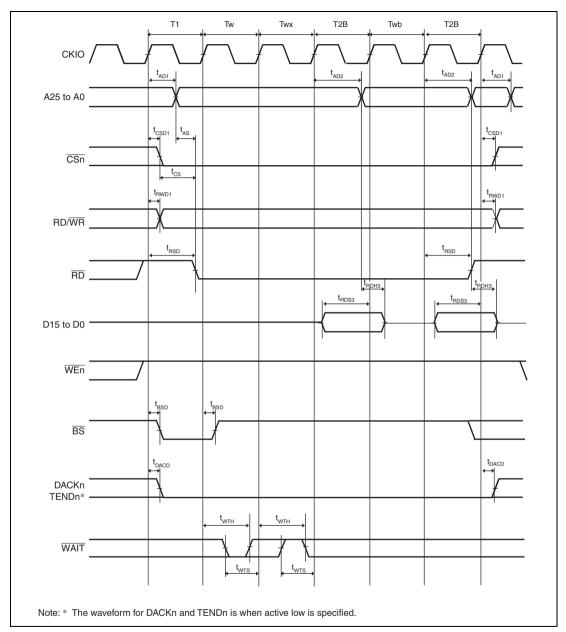

|       | 10.5.6    | Burst ROM (Clocked Asynchronous) Interface                         | 325 |

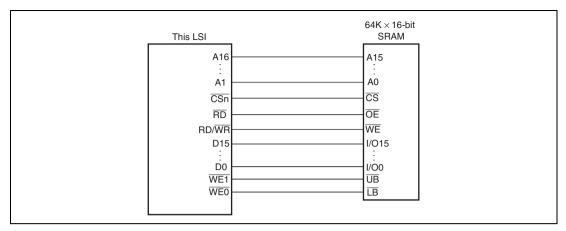

|       | 10.5.7    | SRAM Interface with Byte Selection                                 | 327 |

|       | 10.5.8    | Burst ROM (Clocked Synchronous) Interface                          | 332 |

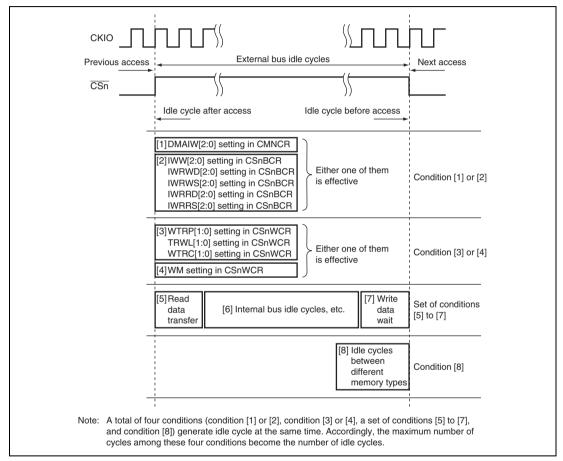

|       | 10.5.9    | Wait between Access Cycles                                         | 333 |

|       | 10.5.10   | Others                                                             | 341 |

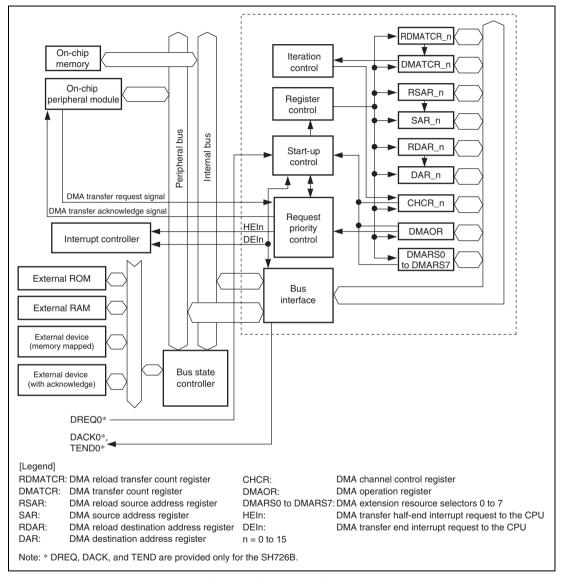

| Secti | on 11 D   | irect Memory Access Controller                                     | 345 |

| 11.1  |           |                                                                    |     |

| 11.2  | Input/O   | ıtput Pins                                                         | 348 |

| 11.3  | -         | Descriptions                                                       |     |

|       | 11.3.1    | DMA Source Address Registers (SAR)                                 |     |

|       | 11.3.2    | DMA Destination Address Registers (DAR)                            |     |

|       | 11.3.3    | DMA Transfer Count Registers (DMATCR)                              | 359 |

|       | 11.3.4    | DMA Channel Control Registers (CHCR)                               |     |

|       | 11.3.5    | DMA Reload Source Address Registers (RSAR)                         |     |

|       | 11.3.6    | DMA Reload Destination Address Registers (RDAR)                    |     |

|       | 11.3.7    | DMA Reload Transfer Count Registers (RDMATCR)                      |     |

|       | 11.3.8    | DMA Operation Register (DMAOR)                                     |     |

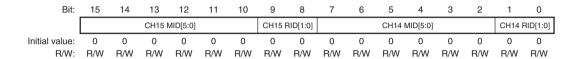

|       | 11.3.9    | DMA Extension Resource Selectors 0 to 7 (DMARS0 to DMARS7)         | 375 |

| 11.4  | Operation | on                                                                 | 380 |

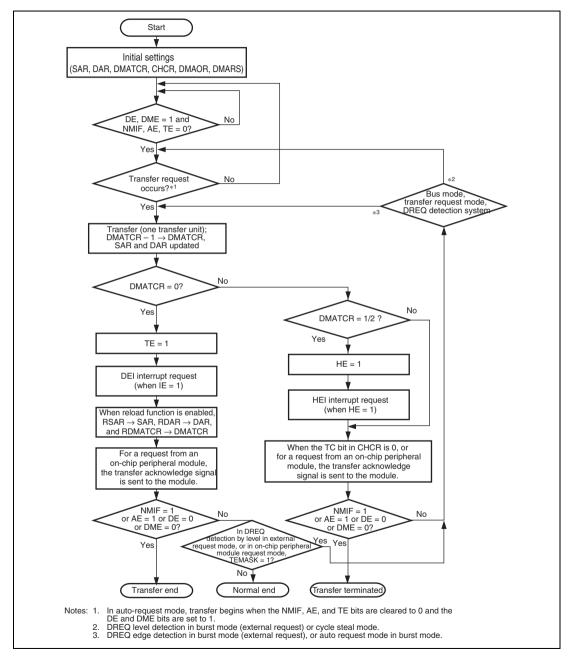

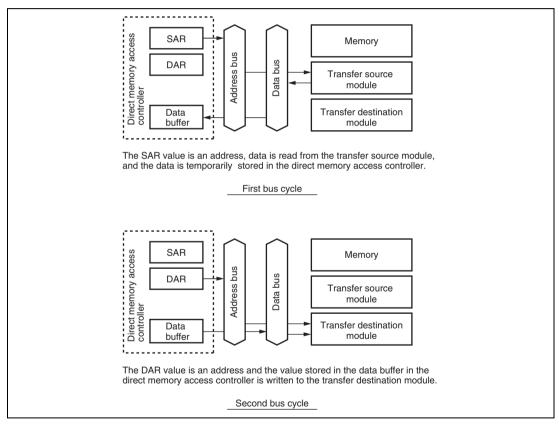

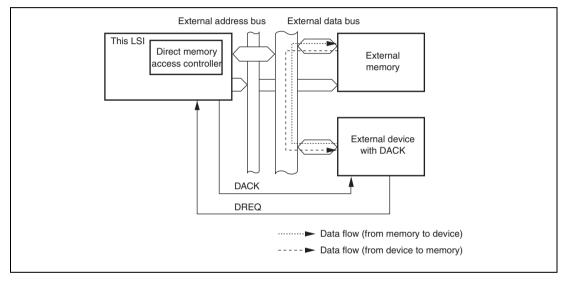

|       | 11.4.1    | Transfer Flow                                                      | 380 |

|       | 11.4.2    | DMA Transfer Requests                                              | 382 |

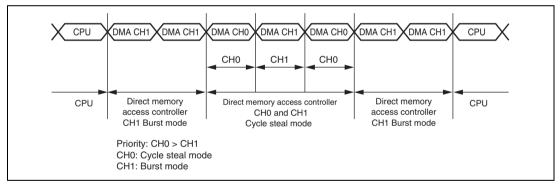

|       | 11.4.3    | Channel Priority                                                   |     |

|       | 11.4.4    | DMA Transfer Types                                                 | 389 |

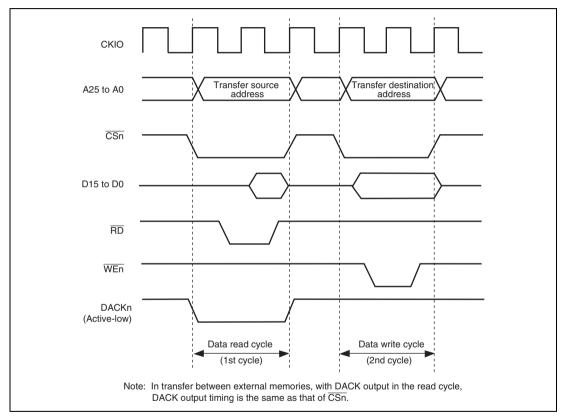

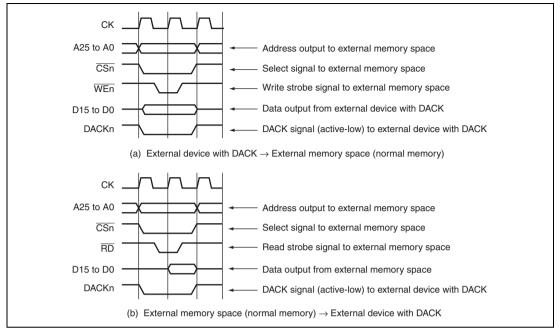

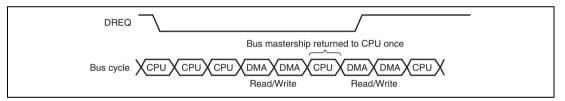

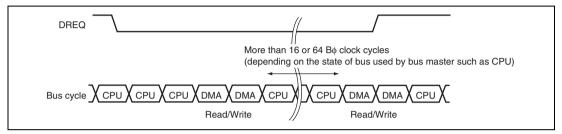

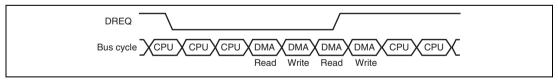

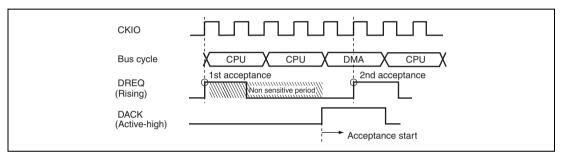

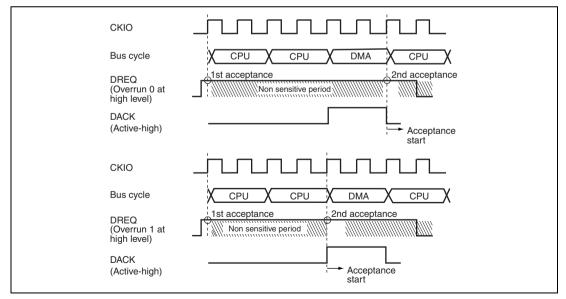

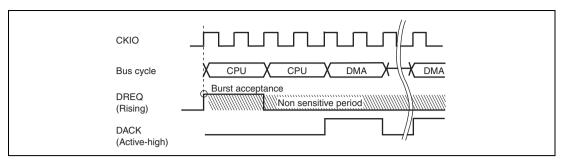

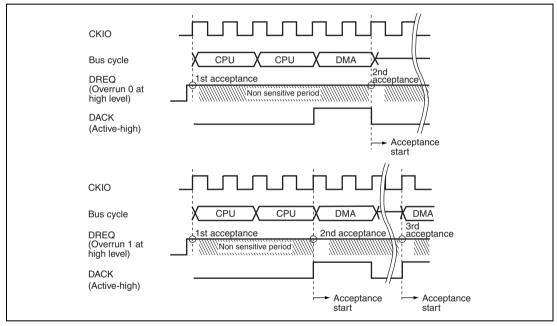

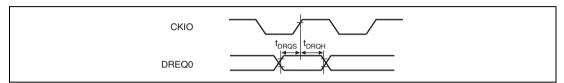

|      | 11.4.5   | Number of Bus Cycles and DREQ Pin Sampling Timing            | 400 |

|------|----------|--------------------------------------------------------------|-----|

| 11.5 | Usage N  | lotes                                                        | 404 |

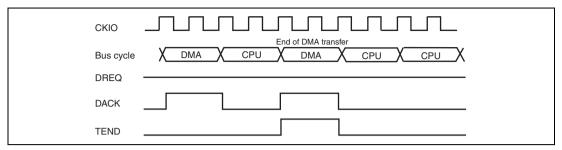

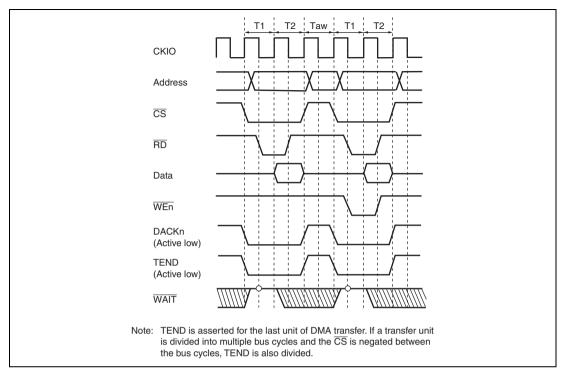

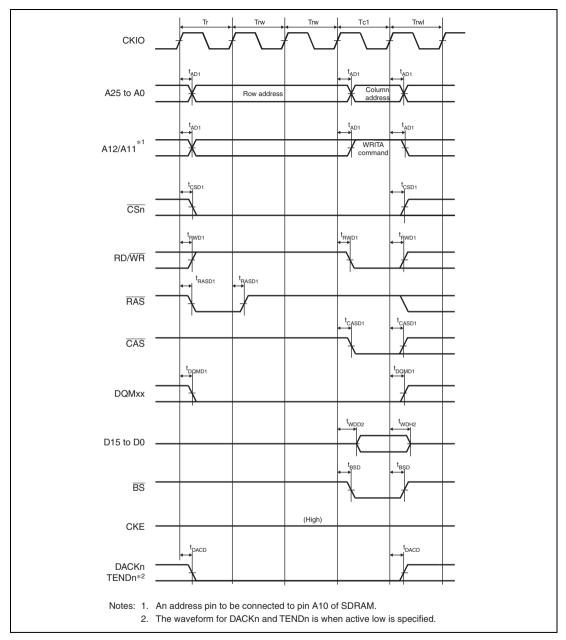

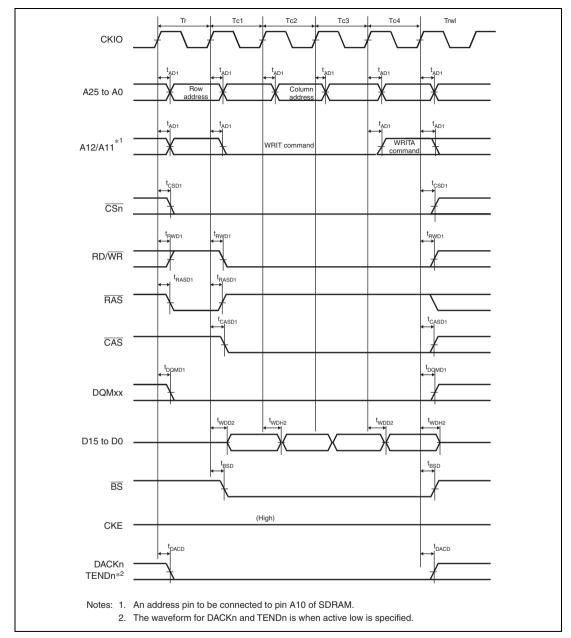

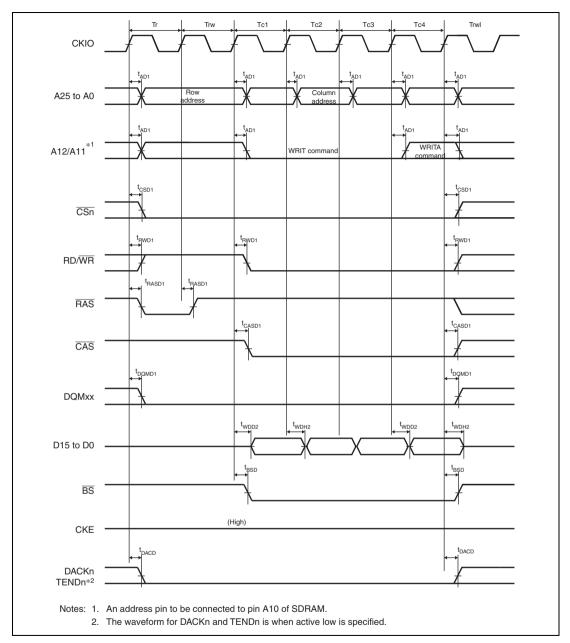

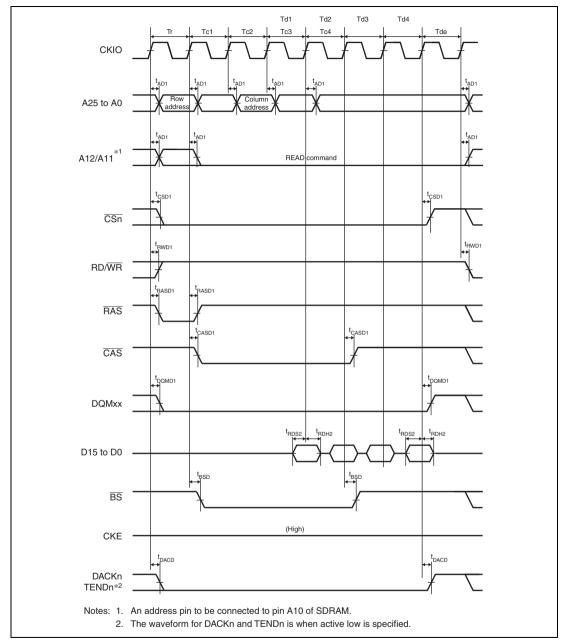

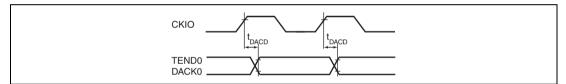

|      | 11.5.1   | Timing of DACK and TEND Outputs                              | 404 |

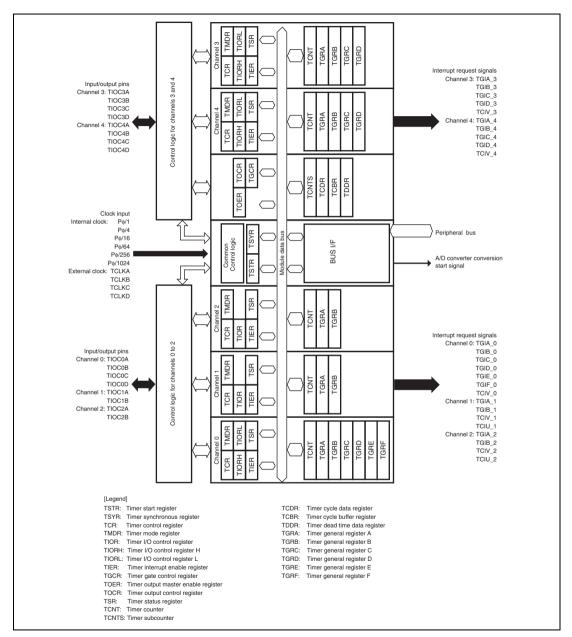

| Sect | ion 12 M | Iulti-Function Timer Pulse Unit 2                            | 405 |

| 12.1 | Features |                                                              | 405 |

| 12.2 | Input/O  | utput Pins                                                   | 410 |

| 12.3 | Register | Descriptions                                                 |     |

|      | 12.3.1   | Timer Control Register (TCR)                                 | 415 |

|      | 12.3.2   | Timer Mode Register (TMDR)                                   | 419 |

|      | 12.3.3   | Timer I/O Control Register (TIOR)                            | 422 |

|      | 12.3.4   | Timer Interrupt Enable Register (TIER)                       | 440 |

|      | 12.3.5   | Timer Status Register (TSR)                                  | 443 |

|      | 12.3.6   | Timer Buffer Operation Transfer Mode Register (TBTM)         |     |

|      | 12.3.7   | Timer Input Capture Control Register (TICCR)                 | 449 |

|      | 12.3.8   | Timer A/D Converter Start Request Control Register (TADCR)   | 451 |

|      | 12.3.9   | Timer A/D Converter Start Request Cycle Set Registers        |     |

|      |          | (TADCORA_4 and TADCORB_4)                                    | 454 |

|      | 12.3.10  | Timer A/D Converter Start Request Cycle Set Buffer Registers |     |

|      |          | (TADCOBRA_4 and TADCOBRB_4)                                  | 454 |

|      | 12.3.11  | Timer Counter (TCNT)                                         | 455 |

|      | 12.3.12  | Timer General Register (TGR)                                 | 455 |

|      | 12.3.13  | Timer Start Register (TSTR)                                  | 456 |

|      | 12.3.14  | Timer Synchronous Register (TSYR)                            | 457 |

|      | 12.3.15  | Timer Read/Write Enable Register (TRWER)                     | 459 |

|      | 12.3.16  | Timer Output Master Enable Register (TOER)                   | 460 |

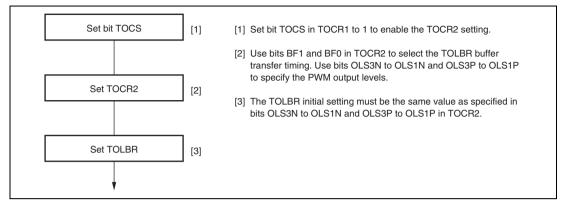

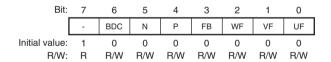

|      | 12.3.17  | Timer Output Control Register 1 (TOCR1)                      | 462 |

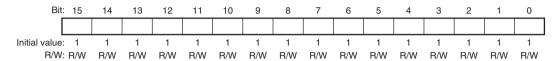

|      | 12.3.18  | Timer Output Control Register 2 (TOCR2)                      | 466 |

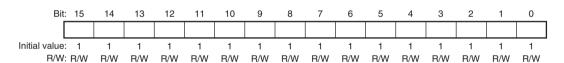

|      | 12.3.19  | Timer Output Level Buffer Register (TOLBR)                   | 469 |

|      | 12.3.20  | Timer Gate Control Register (TGCR)                           | 470 |

|      | 12.3.21  | Timer Subcounter (TCNTS)                                     |     |

|      | 12.3.22  | Timer Dead Time Data Register (TDDR)                         | 473 |

|      | 12.3.23  | Timer Cycle Data Register (TCDR)                             | 473 |

|      | 12.3.24  | Timer Cycle Buffer Register (TCBR)                           | 474 |

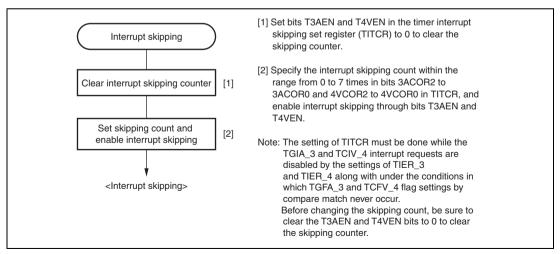

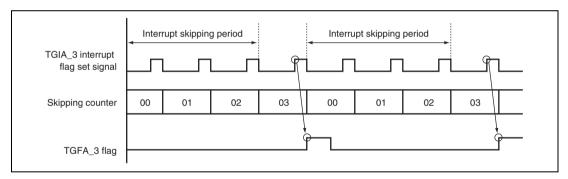

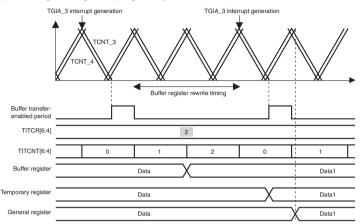

|      | 12.3.25  | Timer Interrupt Skipping Set Register (TITCR)                | 474 |

|      | 12.3.26  | Timer Interrupt Skipping Counter (TITCNT)                    | 476 |

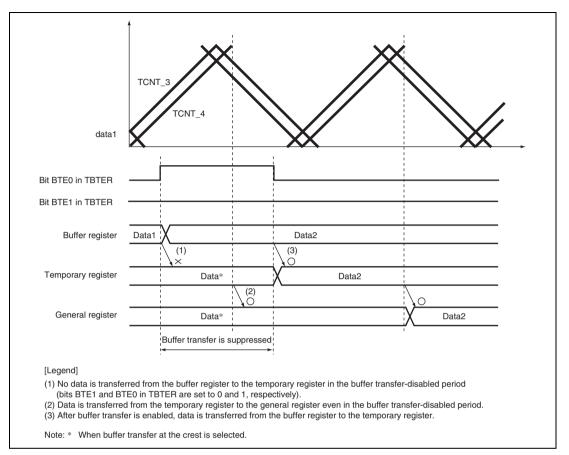

|      | 12.3.27  | Timer Buffer Transfer Set Register (TBTER)                   | 477 |

|      | 12.3.28  | Timer Dead Time Enable Register (TDER)                       | 479 |

|      | 12.3.29  | Timer Waveform Control Register (TWCR)                       | 480 |

|      | 12.3.30  | Bus Master Interface                                         | 481 |

| 12.4 | Operatio    | n                                                           | 482 |

|------|-------------|-------------------------------------------------------------|-----|

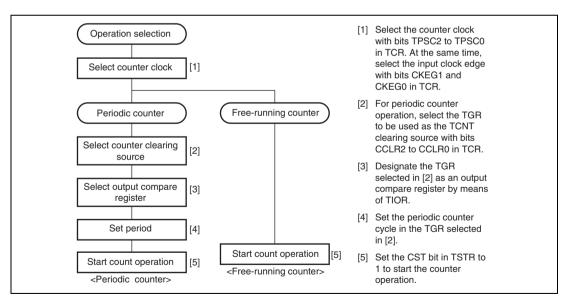

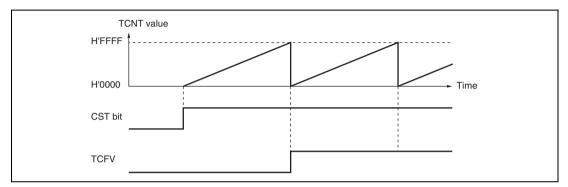

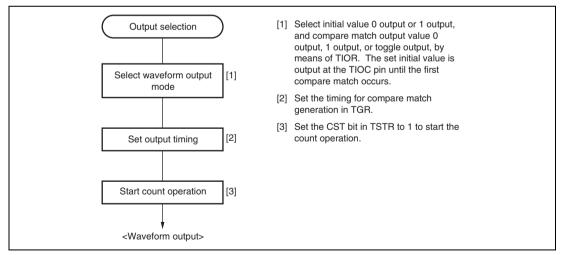

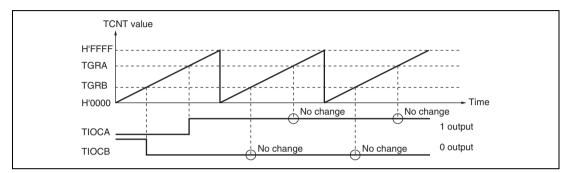

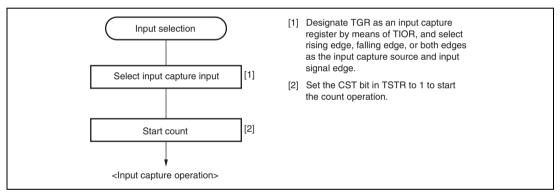

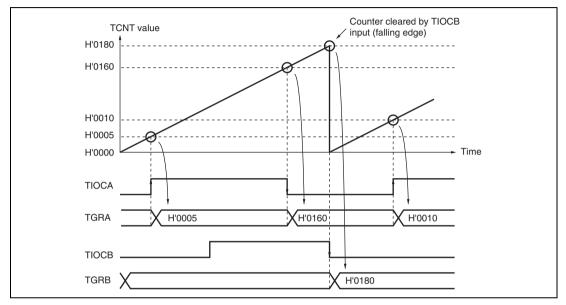

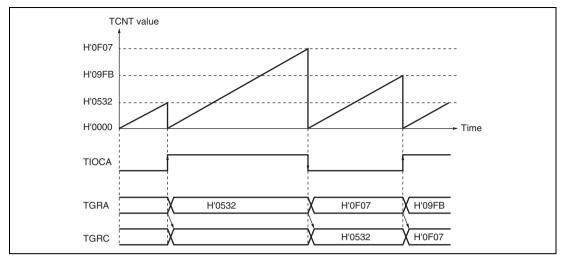

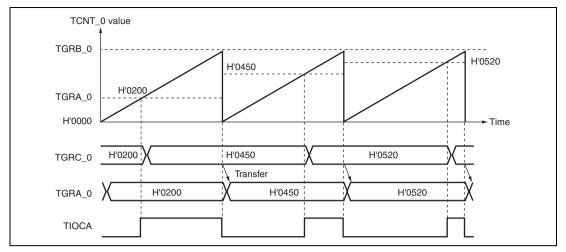

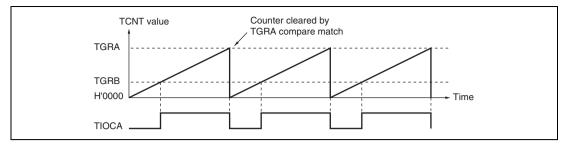

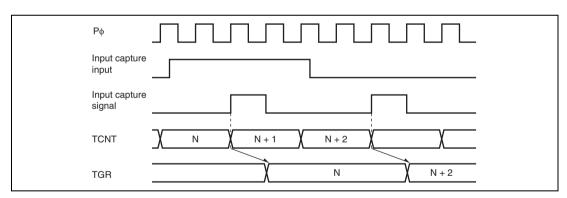

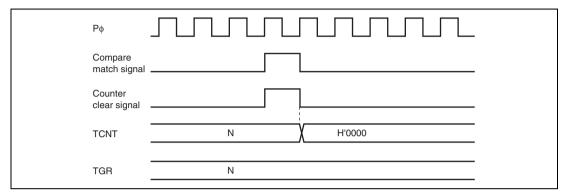

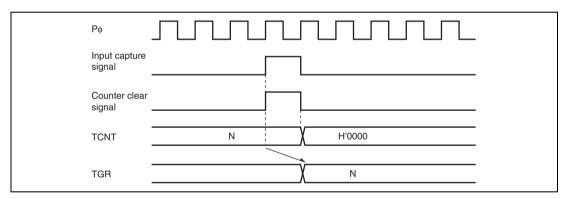

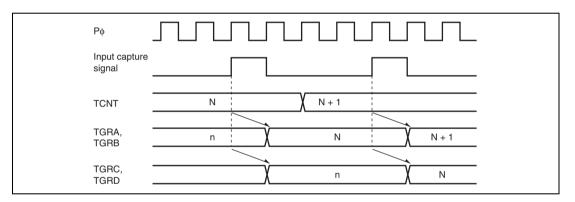

|      | 12.4.1      | Basic Functions                                             | 482 |

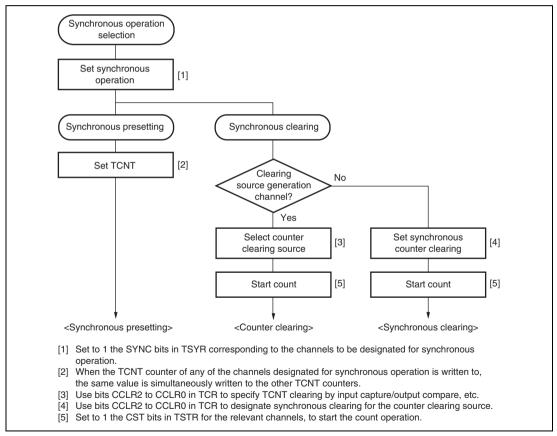

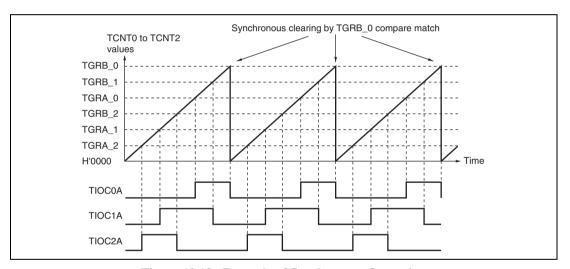

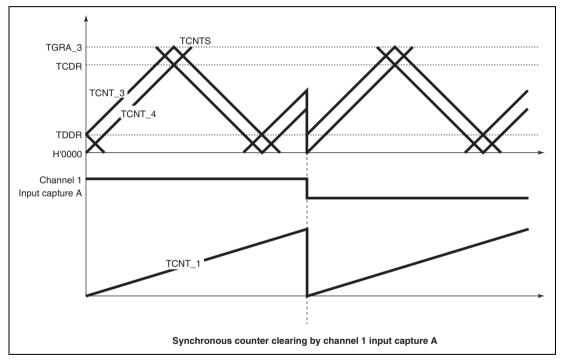

|      | 12.4.2      | Synchronous Operation                                       | 488 |

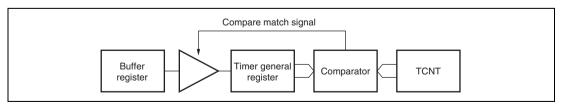

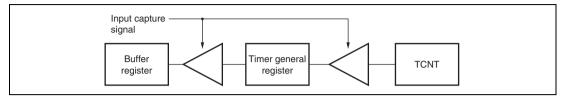

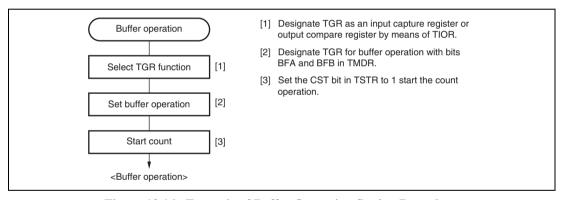

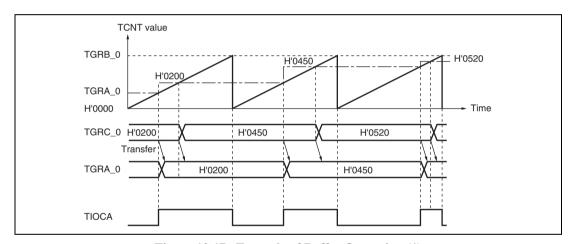

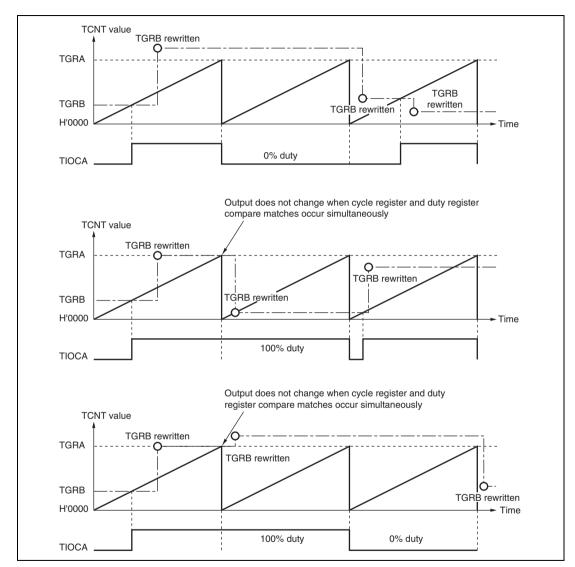

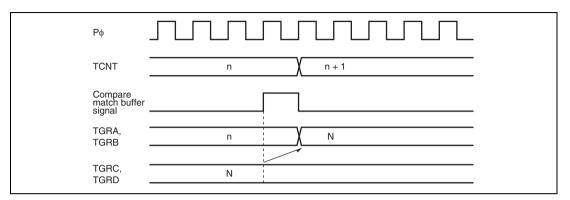

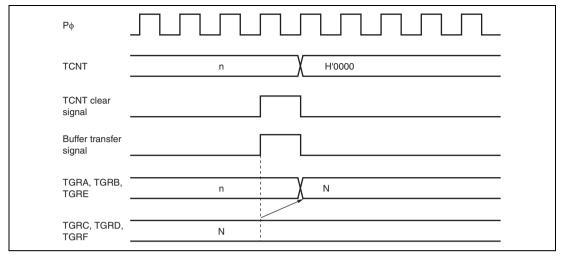

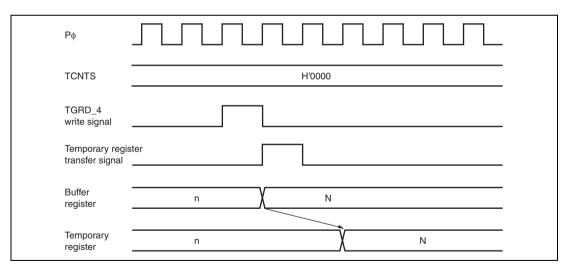

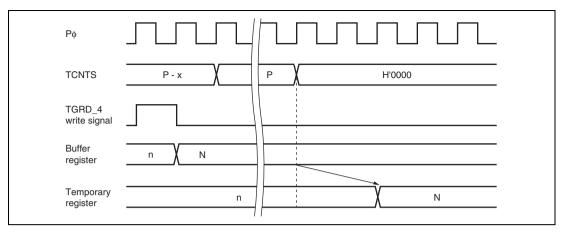

|      | 12.4.3      | Buffer Operation                                            | 490 |

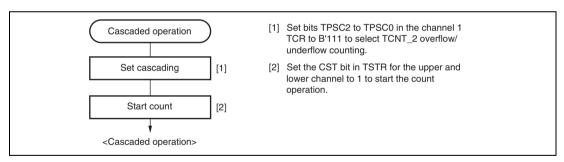

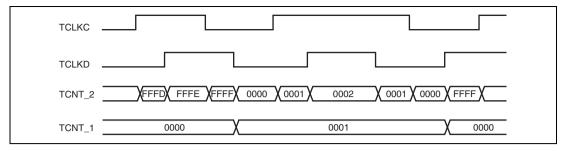

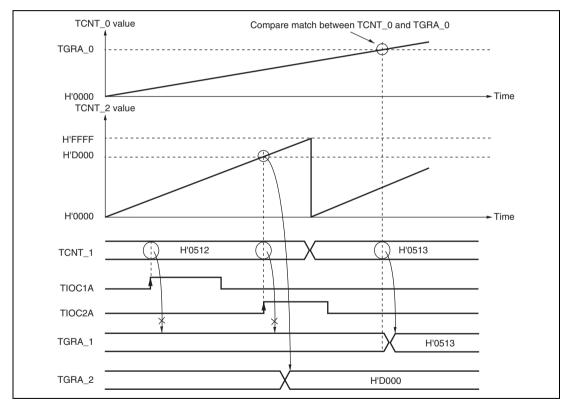

|      | 12.4.4      | Cascaded Operation                                          | 494 |

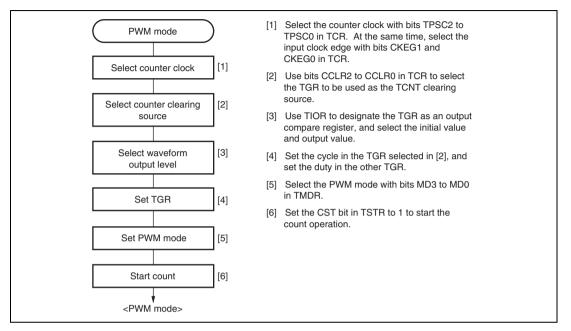

|      | 12.4.5      | PWM Modes                                                   | 499 |

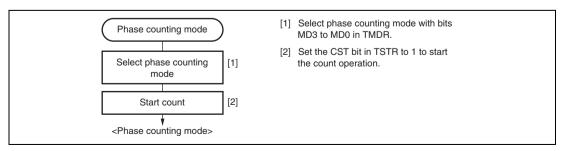

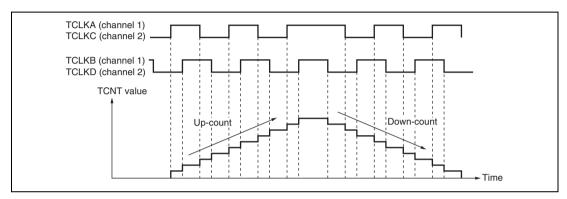

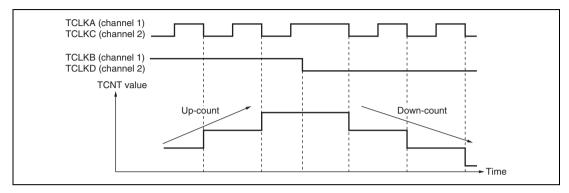

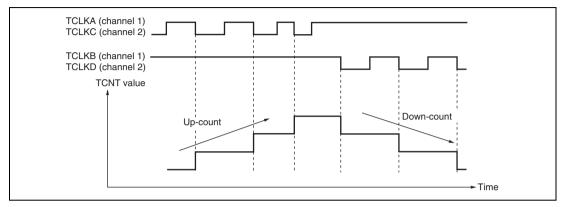

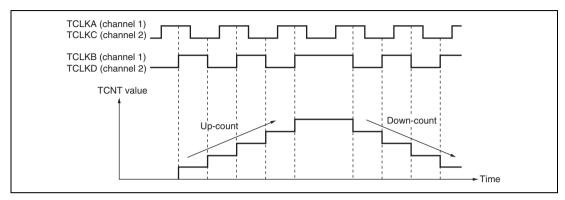

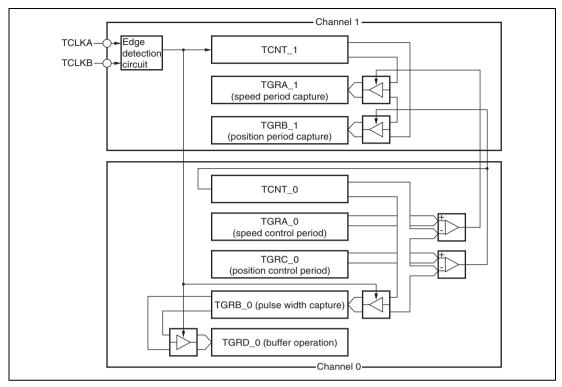

|      | 12.4.6      | Phase Counting Mode                                         | 504 |

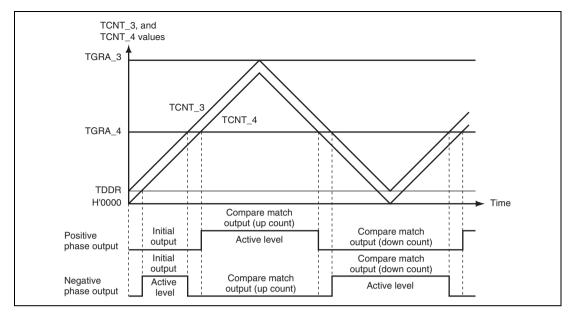

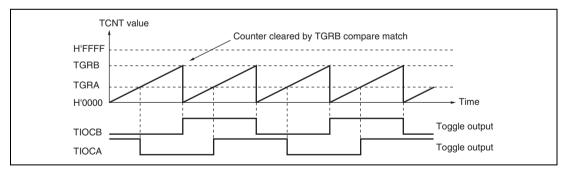

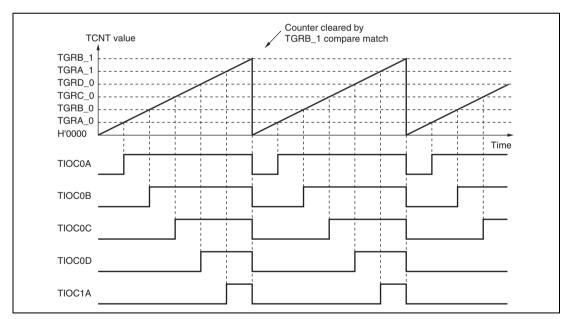

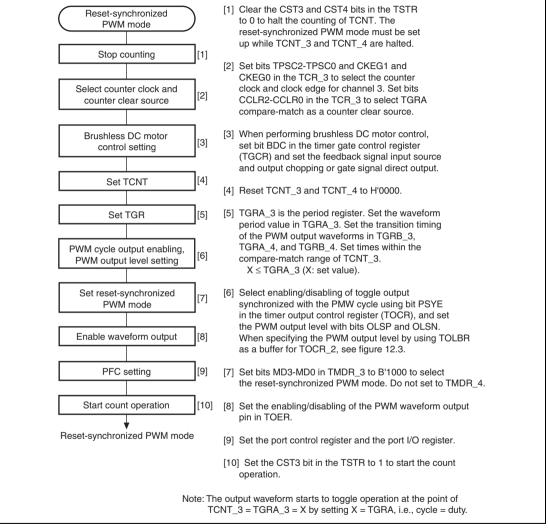

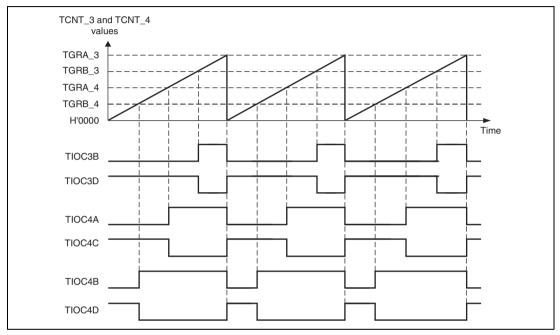

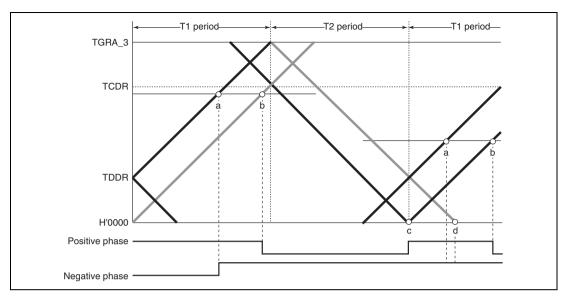

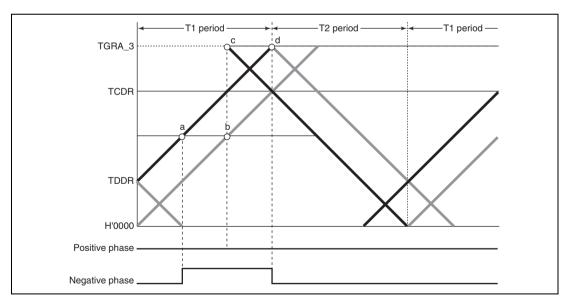

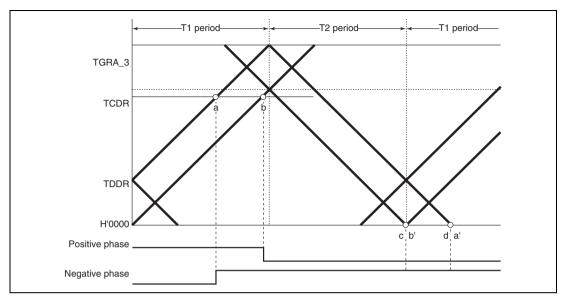

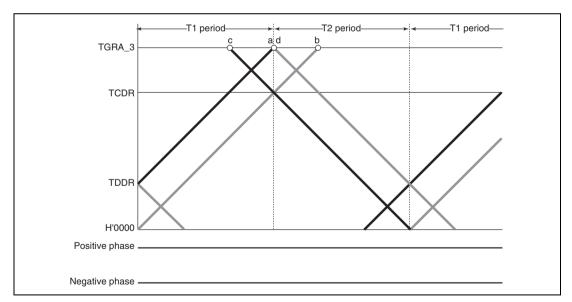

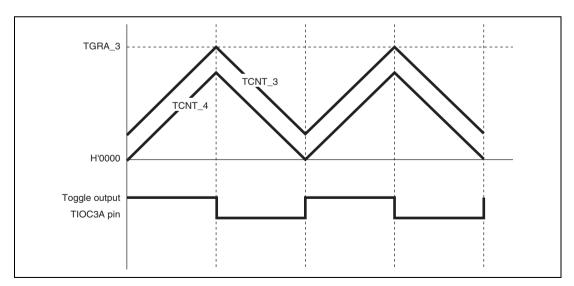

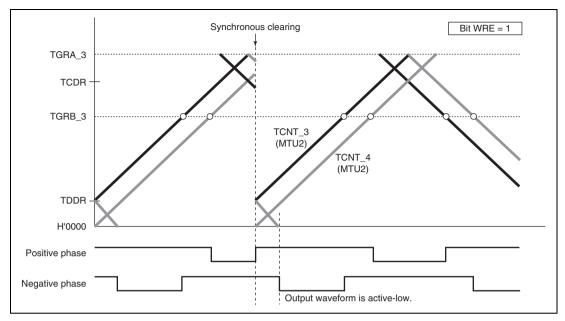

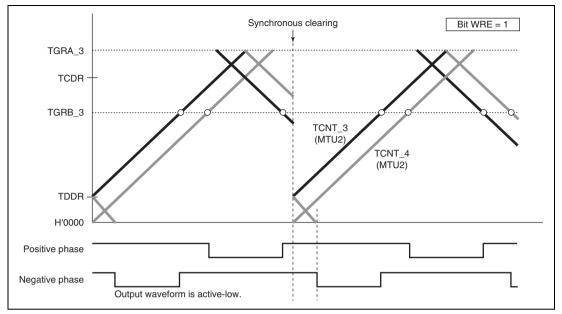

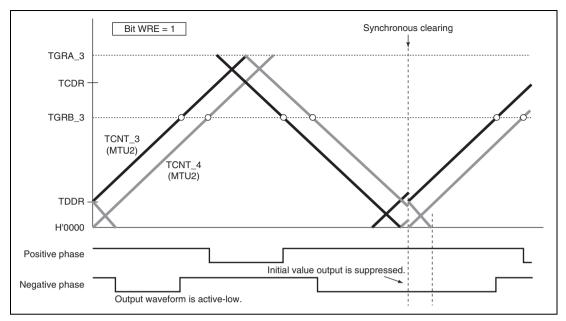

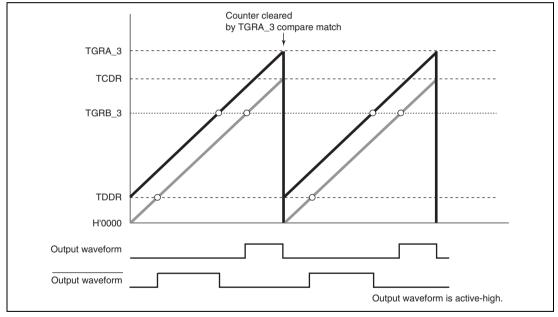

|      | 12.4.7      | Reset-Synchronized PWM Mode                                 | 511 |

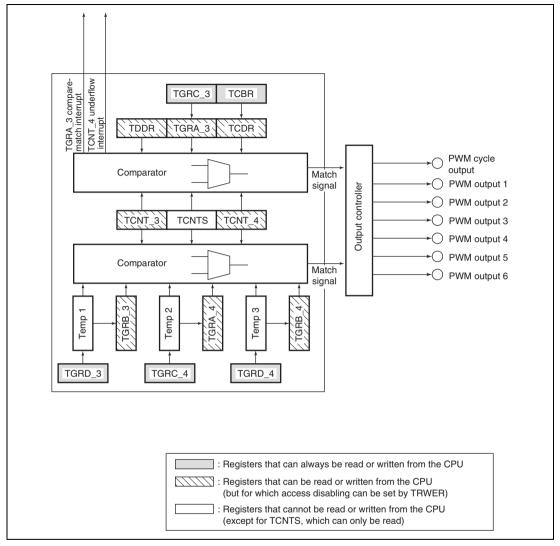

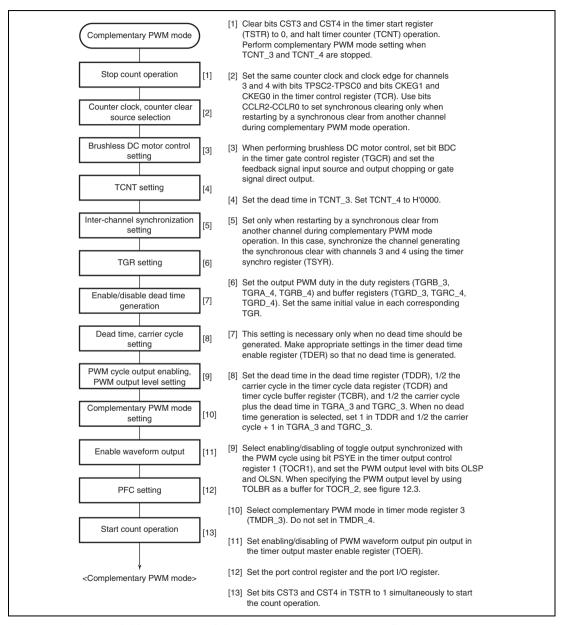

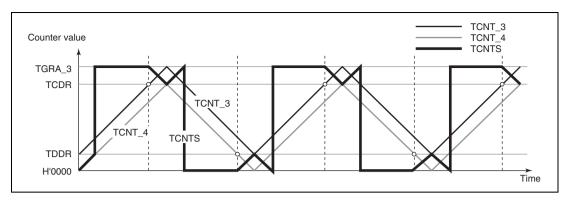

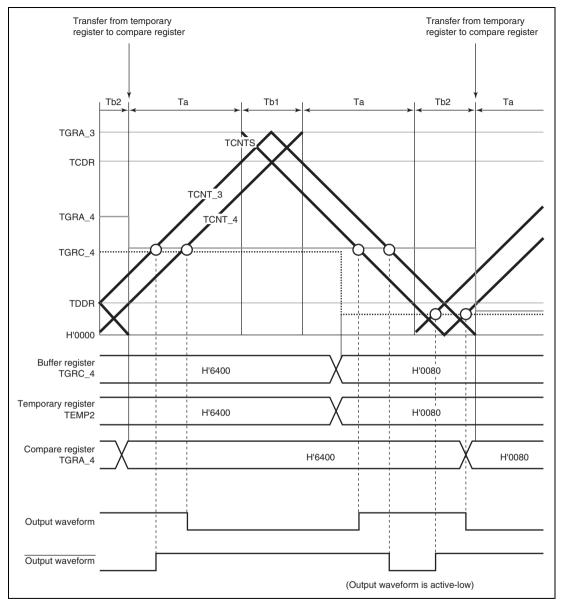

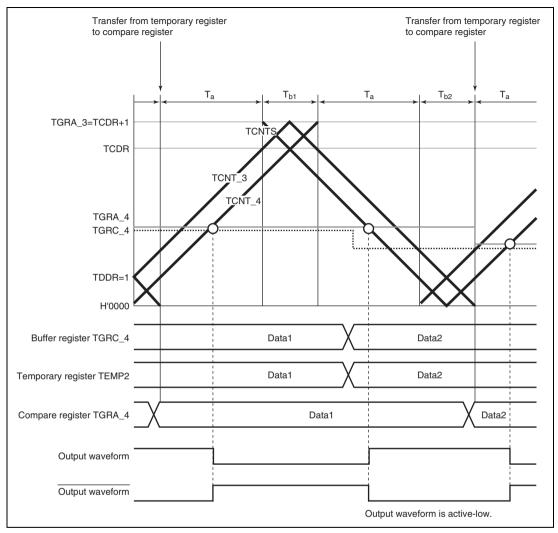

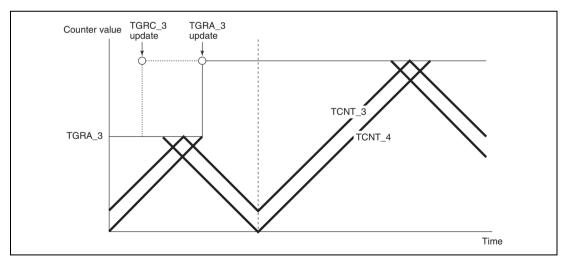

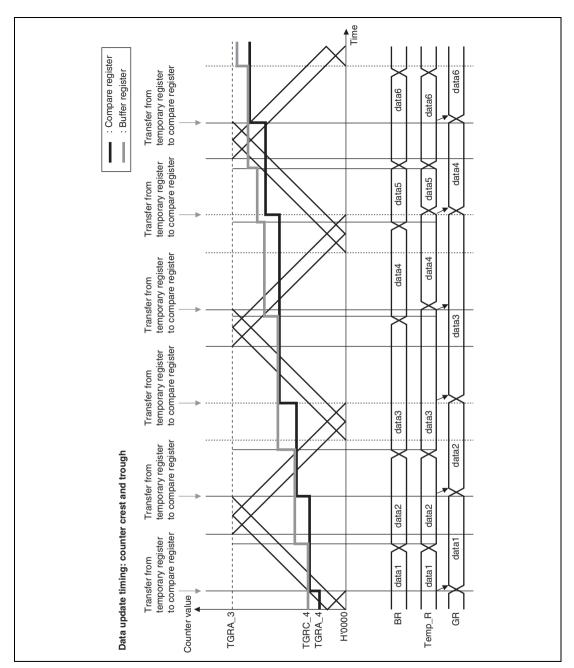

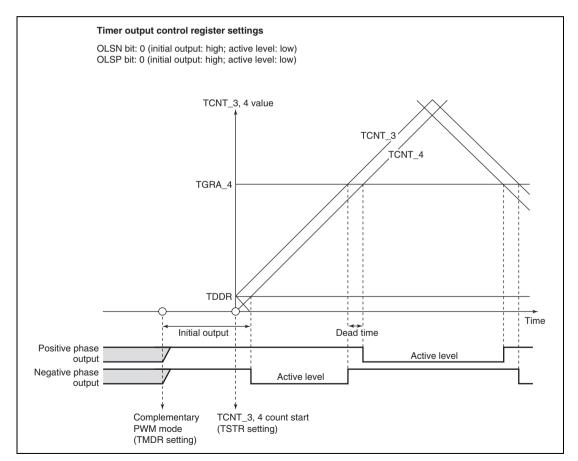

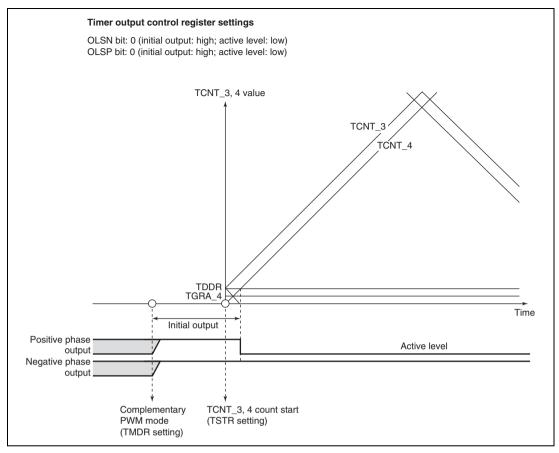

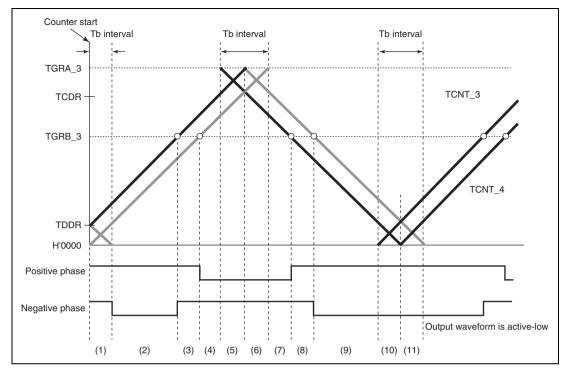

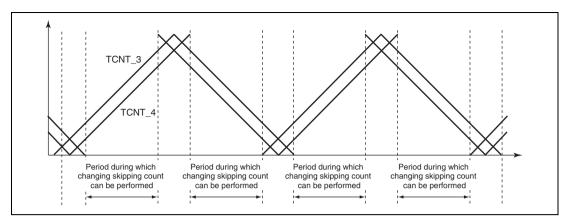

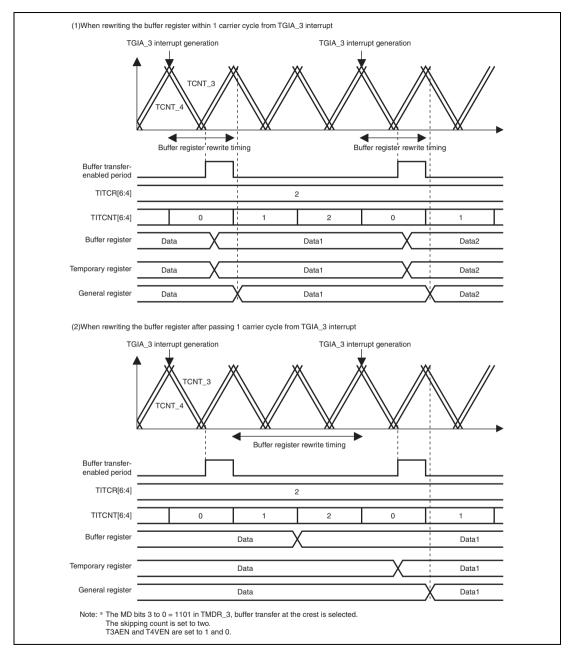

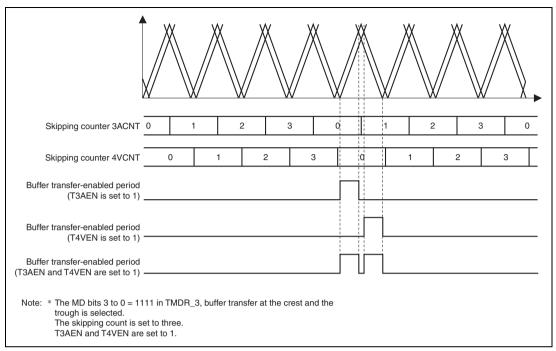

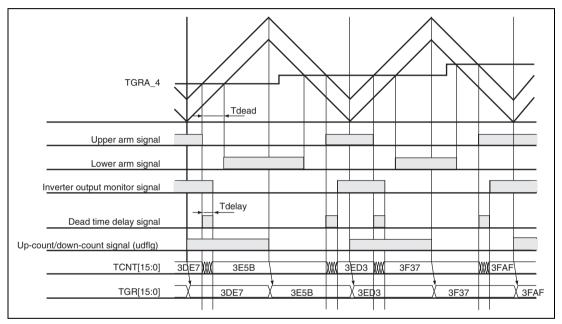

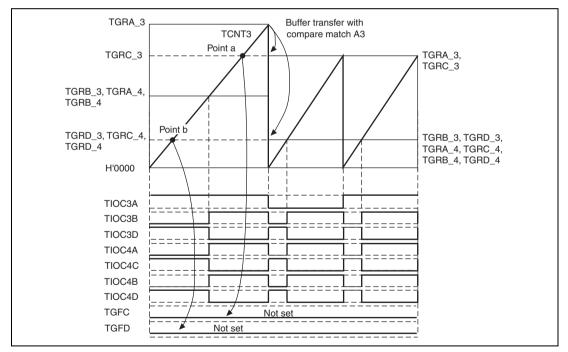

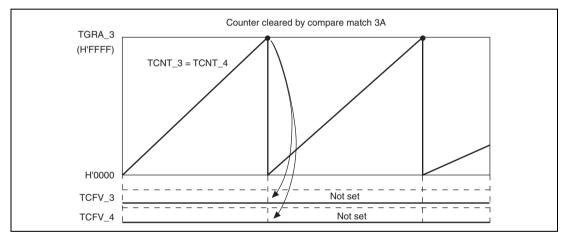

|      | 12.4.8      | Complementary PWM Mode                                      | 514 |

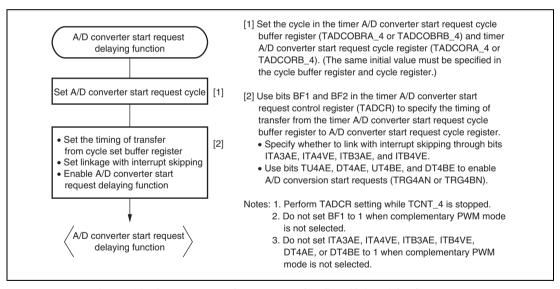

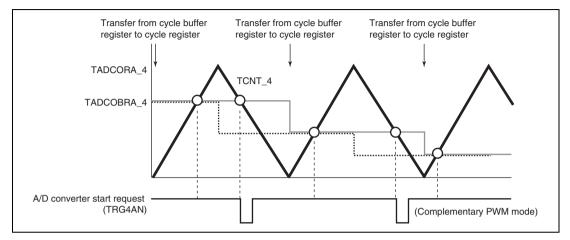

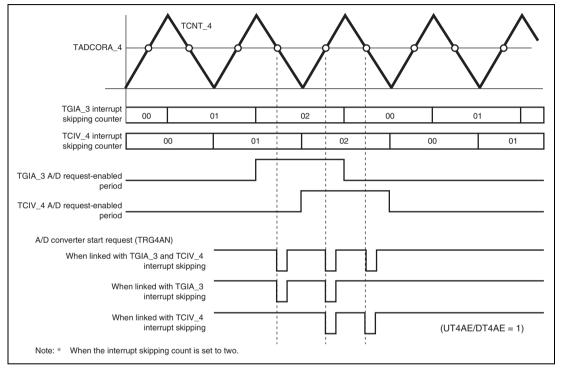

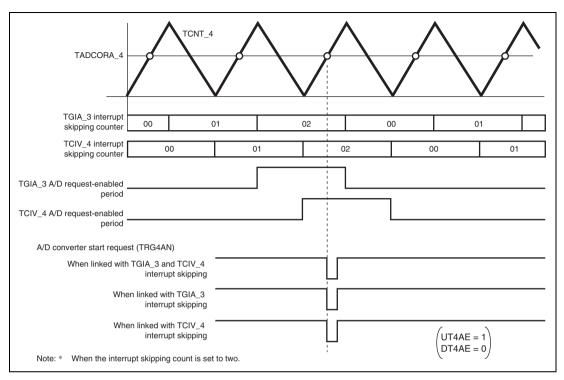

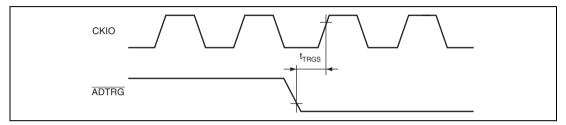

|      | 12.4.9      | A/D Converter Start Request Delaying Function               | 554 |

|      | 12.4.10     | TCNT Capture at Crest and/or Trough in Complementary PWM    |     |

|      |             | Operation                                                   | 558 |

| 12.5 | Interrupt   | Sources                                                     | 559 |

|      | 12.5.1      | Interrupt Sources and Priorities                            | 559 |

|      | 12.5.2      | Activation of Direct Memory Access Controller               | 561 |

|      | 12.5.3      | A/D Converter Activation                                    | 561 |

| 12.6 | Operatio    | n Timing                                                    | 563 |

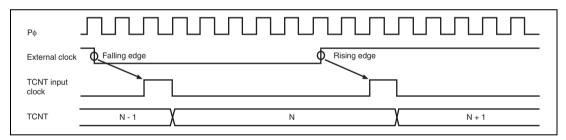

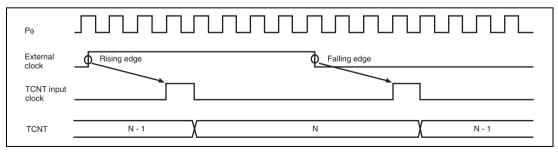

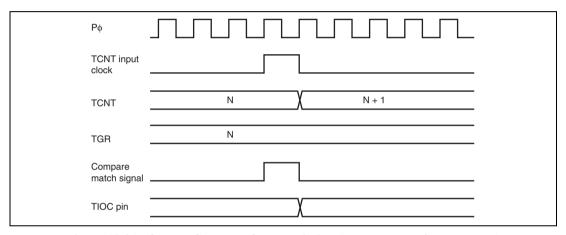

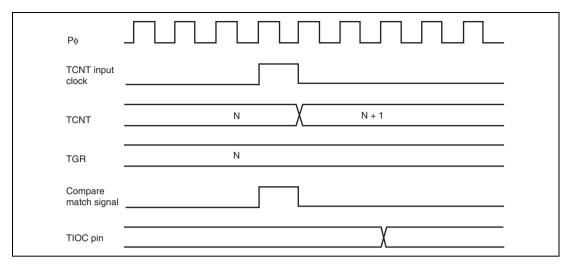

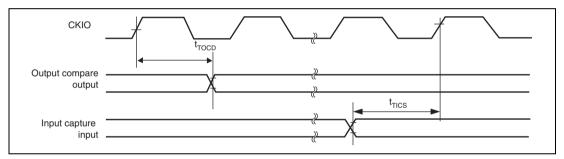

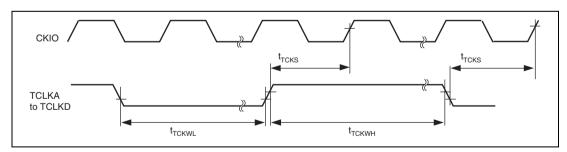

|      | 12.6.1      | Input/Output Timing                                         | 563 |

|      | 12.6.2      | Interrupt Signal Timing                                     | 570 |

| 12.7 | Usage Notes |                                                             |     |

|      | 12.7.1      | Module Standby Mode Setting                                 | 574 |

|      | 12.7.2      | Input Clock Restrictions                                    | 574 |

|      | 12.7.3      | Caution on Period Setting                                   | 575 |

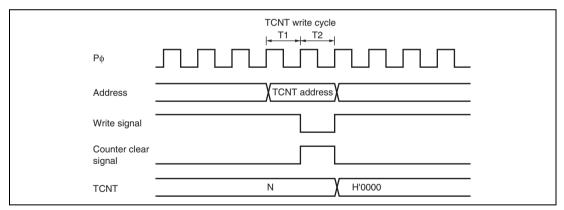

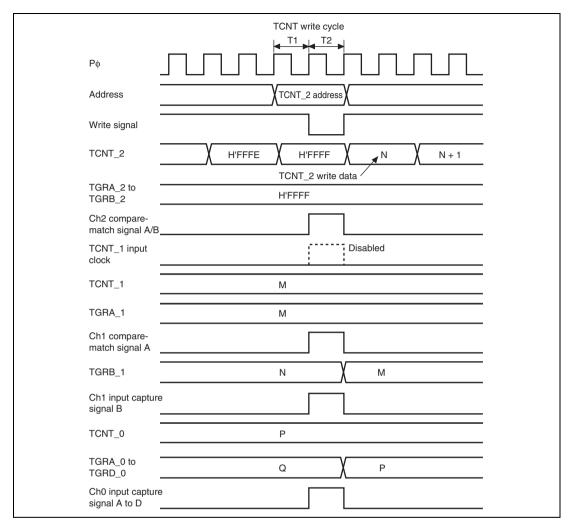

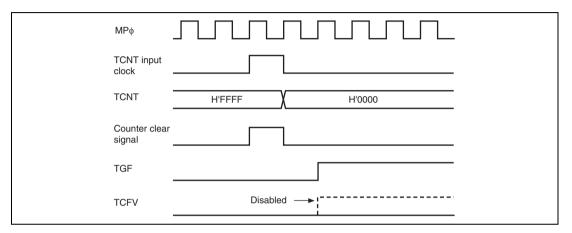

|      | 12.7.4      | Contention between TCNT Write and Clear Operations          | 575 |

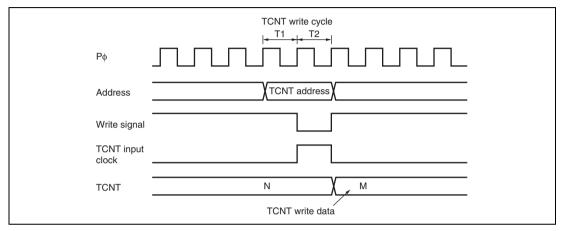

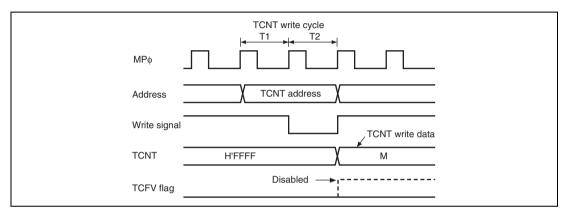

|      | 12.7.5      | Contention between TCNT Write and Increment Operations      | 576 |

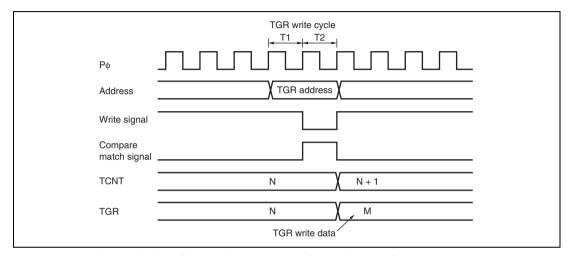

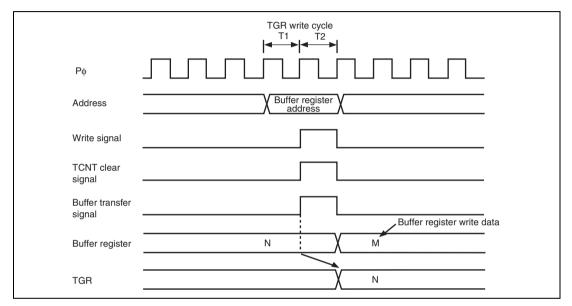

|      | 12.7.6      | Contention between TGR Write and Compare Match              | 577 |

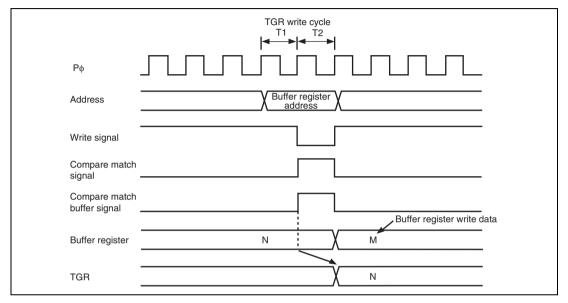

|      | 12.7.7      | Contention between Buffer Register Write and Compare Match  | 578 |

|      | 12.7.8      | Contention between Buffer Register Write and TCNT Clear     | 579 |

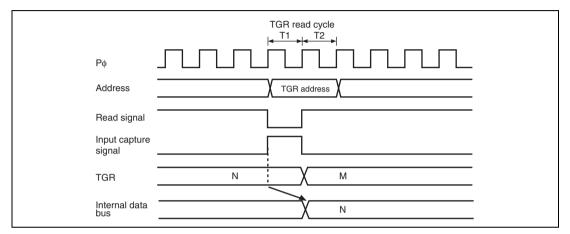

|      | 12.7.9      | Contention between TGR Read and Input Capture               | 580 |

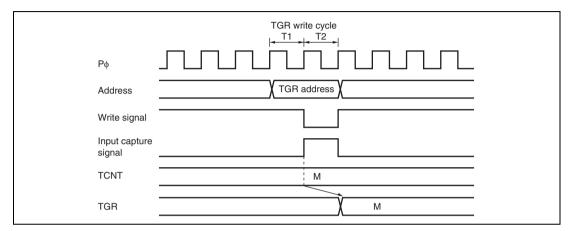

|      | 12.7.10     | Contention between TGR Write and Input Capture              |     |

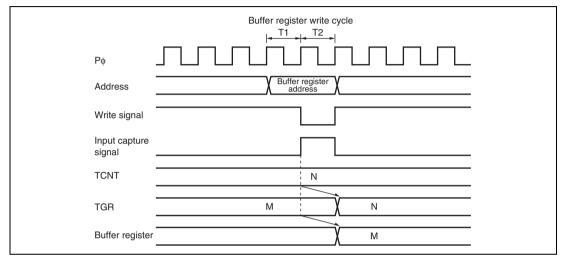

|      | 12.7.11     | Contention between Buffer Register Write and Input Capture  | 582 |

|      | 12.7.12     | TCNT2 Write and Overflow/Underflow Contention in Cascade    |     |

|      |             | Connection                                                  | 582 |

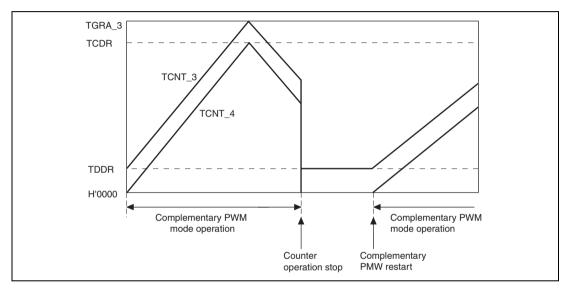

|      | 12.7.13     | Counter Value during Complementary PWM Mode Stop            | 584 |

|      | 12.7.14     | Buffer Operation Setting in Complementary PWM Mode          |     |

|      | 12.7.15     | Reset Sync PWM Mode Buffer Operation and Compare Match Flag |     |

|      | 12.7.16     | Overflow Flags in Reset Synchronous PWM Mode                |     |

|      | 12.7.17     | Contention between Overflow/Underflow and Counter Clearing  |     |

|      | 12.7.18     | Contention between TCNT Write and Overflow/Underflow        |     |

|      |             |                                                             |     |

|       | 12.7.19  | Cautions on Transition from Normal Operation or PWM Mode 1 to         |     |

|-------|----------|-----------------------------------------------------------------------|-----|

|       |          | Reset-Synchronized PWM Mode                                           | 588 |

|       | 12.7.20  | Output Level in Complementary PWM Mode and Reset-Synchronized         |     |

|       |          | PWM Mode                                                              | 589 |

|       | 12.7.21  | Interrupts in Module Standby Mode                                     | 589 |

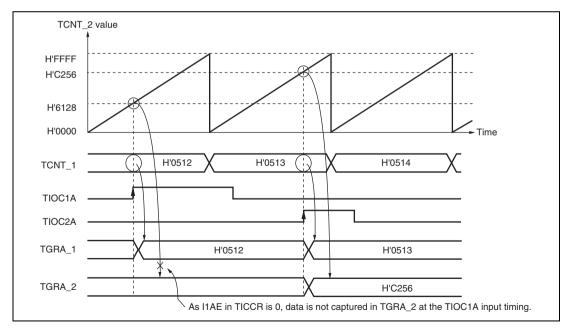

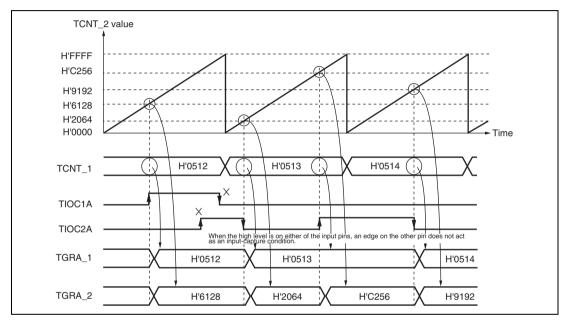

|       | 12.7.22  | Simultaneous Capture of TCNT_1 and TCNT_2 in Cascade Connection       | 589 |

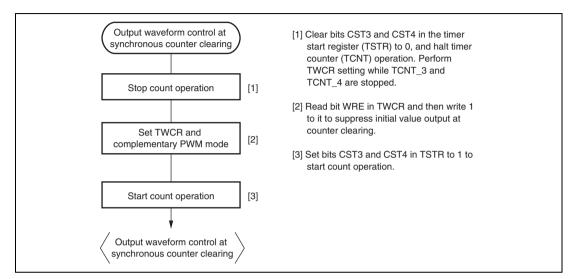

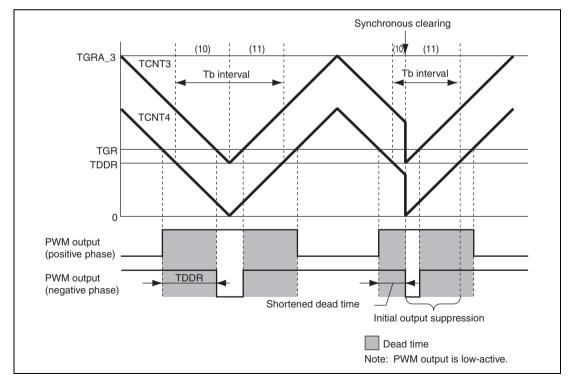

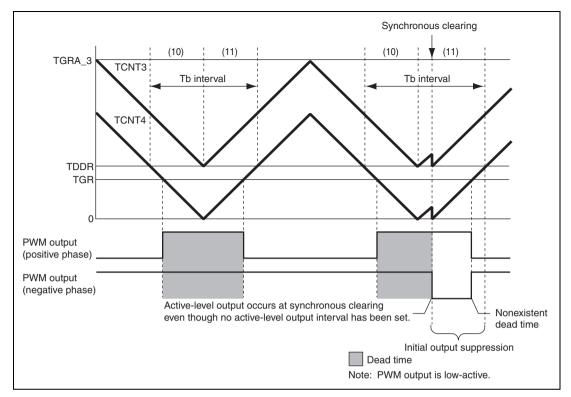

|       | 12.7.23  | Notes on Output Waveform Control During Synchronous Counter Clearing  |     |

|       |          | in Complementary PWM Mode                                             |     |

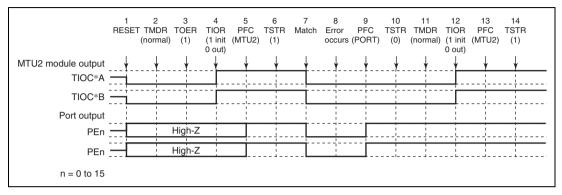

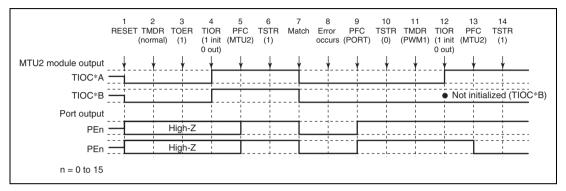

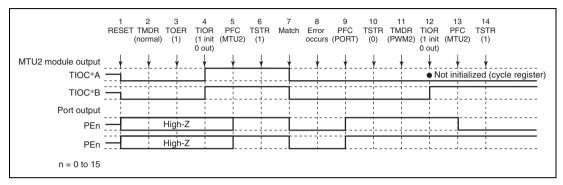

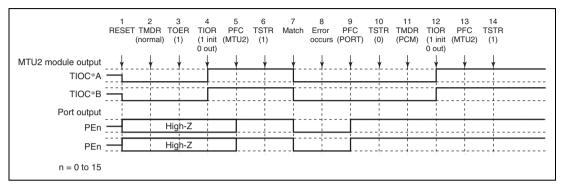

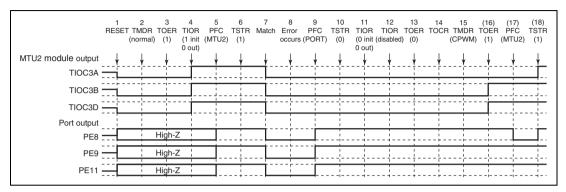

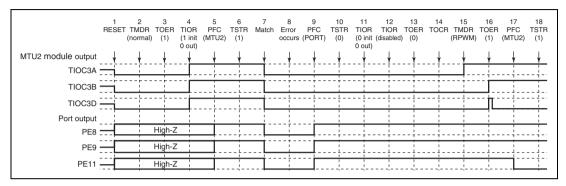

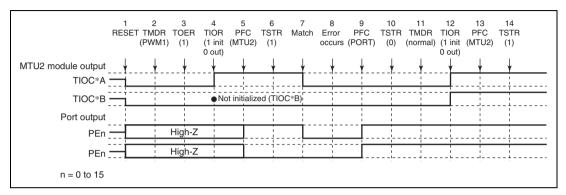

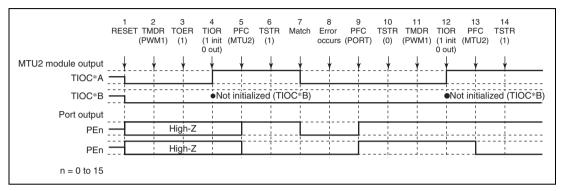

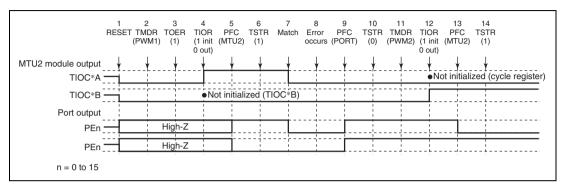

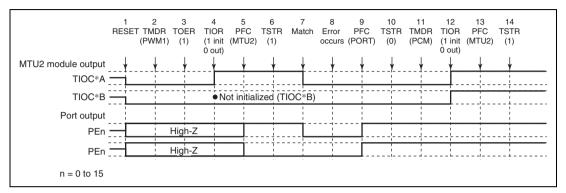

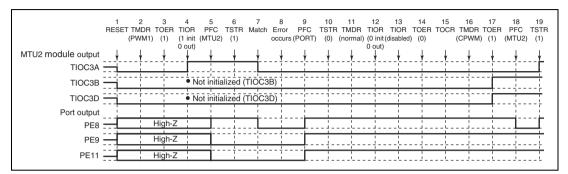

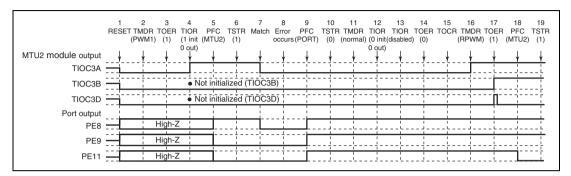

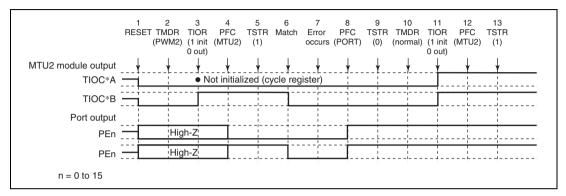

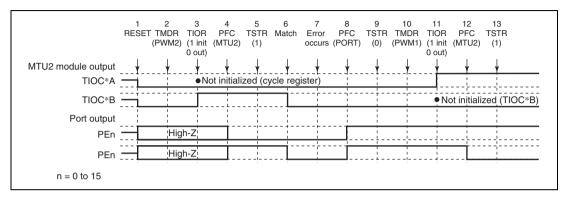

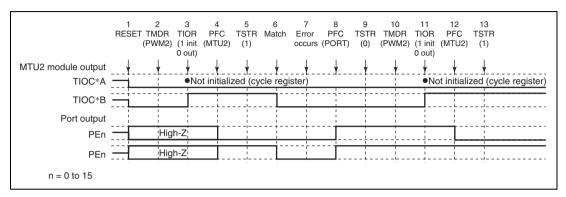

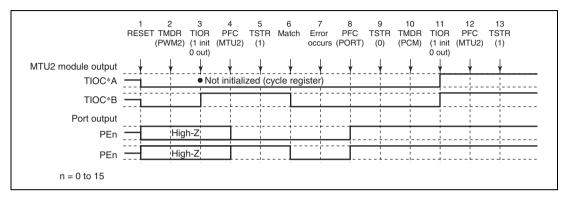

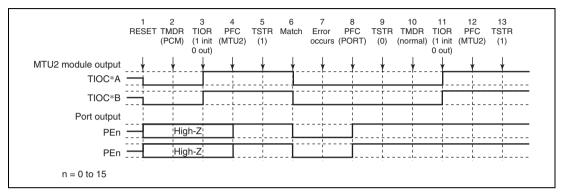

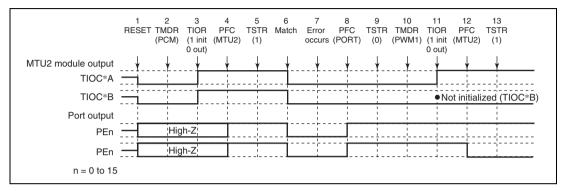

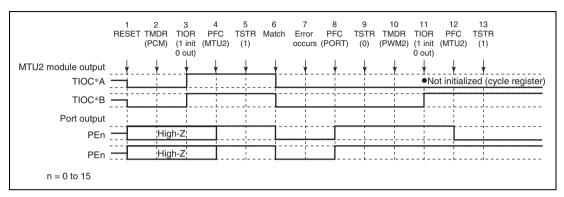

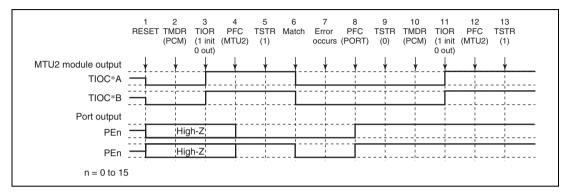

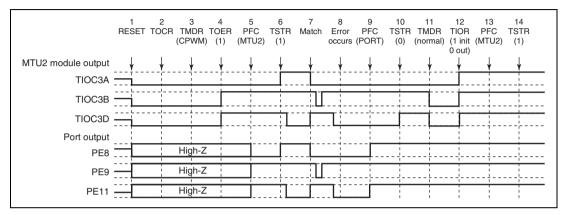

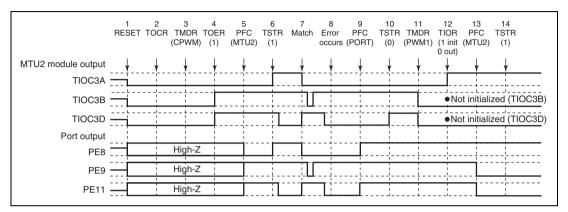

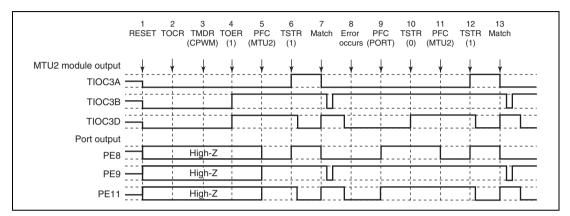

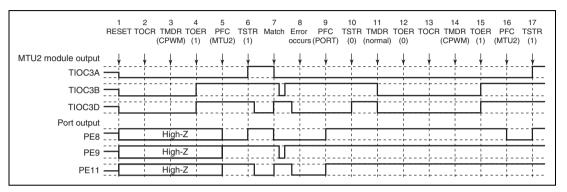

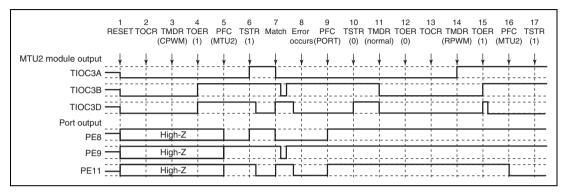

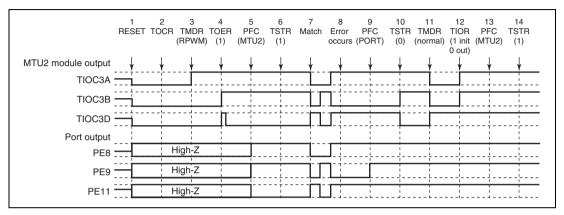

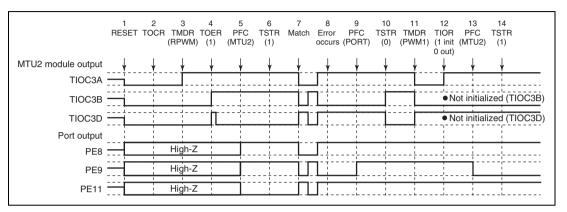

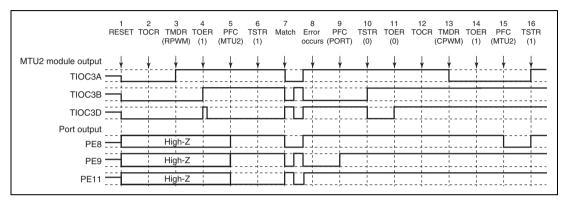

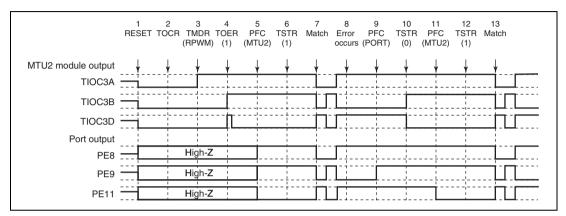

| 12.8  | Output l | Pin Initialization for Multi-Function Timer Pulse Unit 2              | 592 |

|       | 12.8.1   | Operating Modes                                                       | 592 |

|       | 12.8.2   | Reset Start Operation                                                 | 592 |

|       | 12.8.3   | Operation in Case of Re-Setting Due to Error during Operation, etc    | 593 |

|       | 12.8.4   | Overview of Initialization Procedures and Mode Transitions in Case of |     |

|       |          | Error during Operation, etc.                                          | 594 |

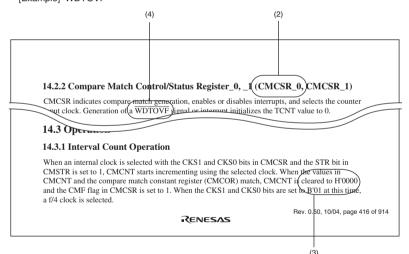

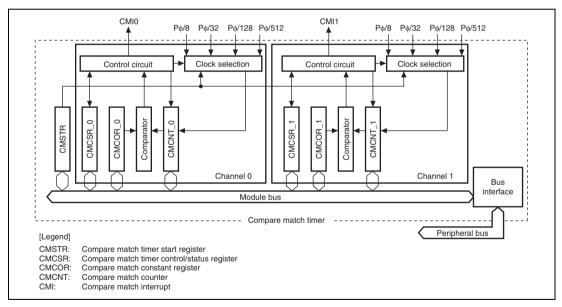

| Secti | on 13 C  | ompare Match Timer                                                    | 625 |

| 13.1  |          |                                                                       |     |

| 13.2  |          | Descriptions                                                          |     |

| 10.2  | 13.2.1   | Compare Match Timer Start Register (CMSTR)                            |     |

|       | 13.2.2   | Compare Match Timer Control/Status Register (CMCSR)                   |     |

|       | 13.2.3   | Compare Match Counter (CMCNT)                                         |     |

|       | 13.2.4   | Compare Match Constant Register (CMCOR)                               |     |

| 13.3  |          | on                                                                    |     |

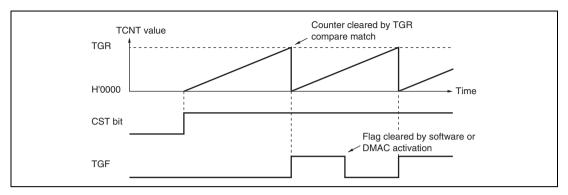

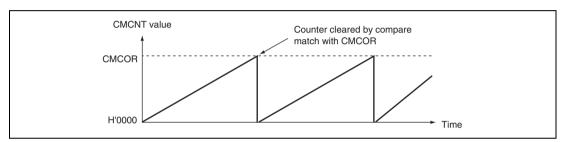

|       | 13.3.1   | Interval Count Operation                                              |     |

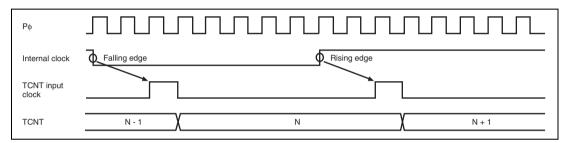

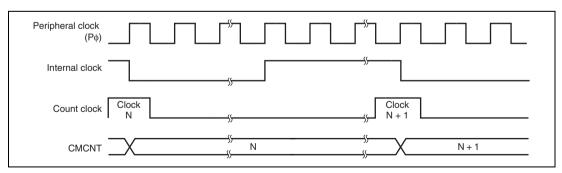

|       | 13.3.2   | CMCNT Count Timing                                                    |     |

| 13.4  |          | ts                                                                    |     |

|       | 13.4.1   | Interrupt Sources and DMA Transfer Requests                           |     |

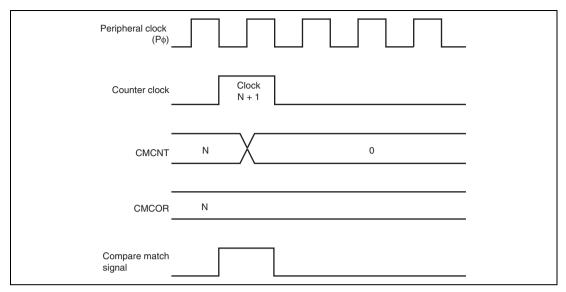

|       | 13.4.2   | Timing of Compare Match Flag Setting                                  |     |

|       | 13.4.3   | Timing of Compare Match Flag Clearing                                 |     |

| 13.5  | Usage N  | Jotes                                                                 |     |

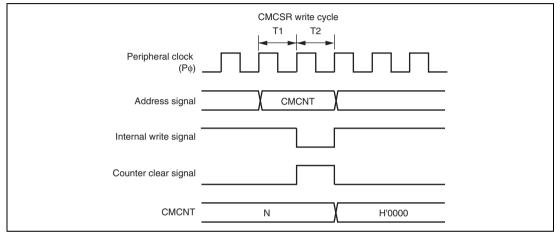

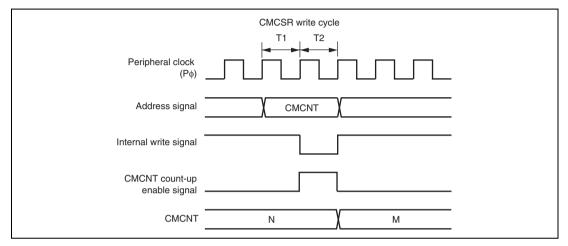

|       | 13.5.1   | Conflict between Write and Compare-Match Processes of CMCNT           |     |

|       | 13.5.2   | Conflict between Word-Write and Count-Up Processes of CMCNT           |     |

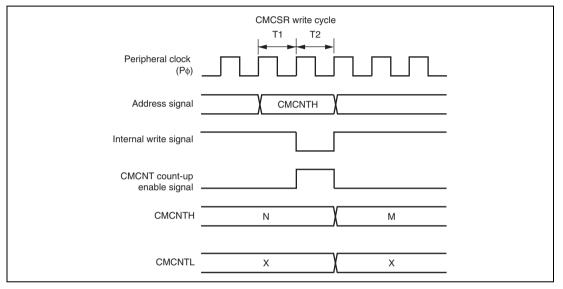

|       | 13.5.3   | Conflict between Byte-Write and Count-Up Processes of CMCNT           |     |

|       | 13.5.4   | Compare Match between CMCNT and CMCOR                                 |     |

| Secti | on 14 W  | Vatchdog Timer                                                        | 637 |

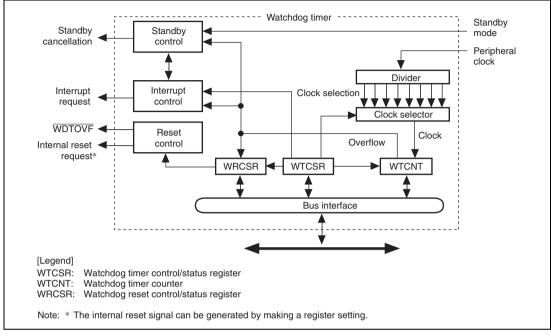

| 14.1  |          | arena og Timer                                                        |     |

| 14.2  |          | utput Pin                                                             |     |

| 14.3  |          | Descriptions                                                          |     |

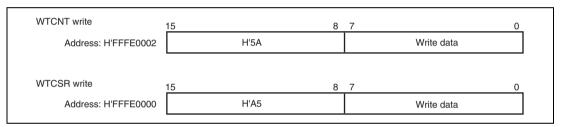

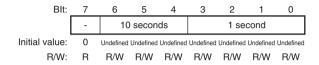

|       | _        | Watchdog Timer Counter (WTCNT)                                        |     |

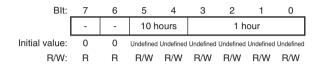

|       | 14.3.2                | Watchdog Timer Control/Status Register (WTCSR) | 640 |  |

|-------|-----------------------|------------------------------------------------|-----|--|

|       | 14.3.3                | Watchdog Reset Control/Status Register (WRCSR) | 643 |  |

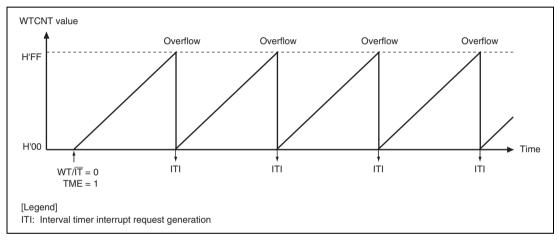

|       | 14.3.4                | Notes on Register Access                       | 644 |  |

| 14.4  | Usage                 |                                                | 646 |  |

|       | 14.4.1                | Canceling Software Standby Mode                | 646 |  |

|       | 14.4.2                | Using Watchdog Timer Mode                      | 646 |  |

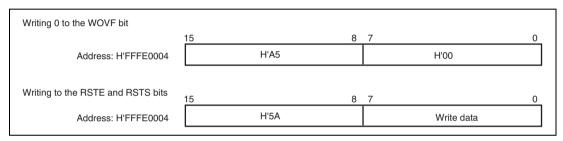

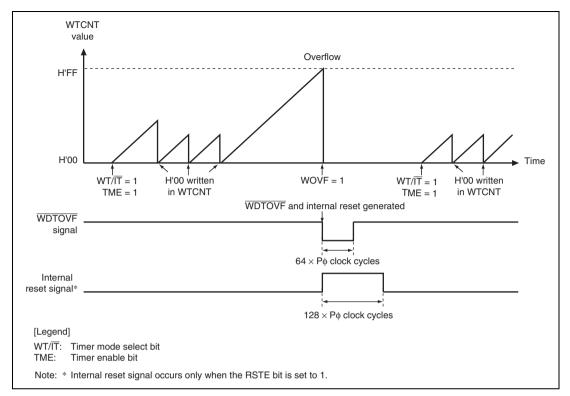

|       | 14.4.3                | Using Interval Timer Mode                      | 648 |  |

| 14.5  | Usage N               | Notes                                          | 649 |  |

|       | 14.5.1                | Timer Variation                                | 649 |  |

|       | 14.5.2                | Prohibition against Setting H'FF to WTCNT      | 649 |  |

|       | 14.5.3                | Interval Timer Overflow Flag                   |     |  |

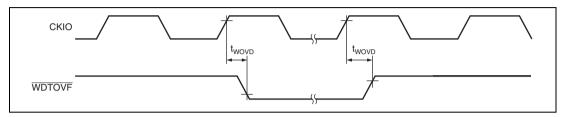

|       | 14.5.4                | System Reset by WDTOVF Signal                  | 650 |  |

|       | 14.5.5                | Manual Reset in Watchdog Timer Mode            | 650 |  |

|       | 14.5.6                | Internal Reset in Watchdog Timer Mode          | 650 |  |

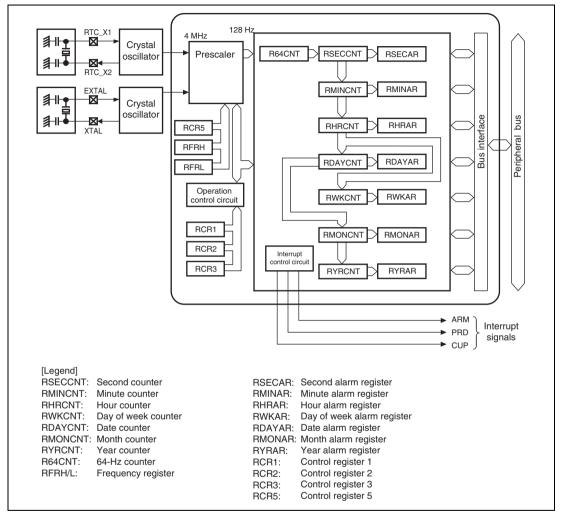

| Secti | ion 15 R              | ealtime Clock                                  | 651 |  |

| 15.1  |                       | 3                                              |     |  |

| 15.2  | Input/Output Pin      |                                                |     |  |

| 15.3  | Register Descriptions |                                                |     |  |

|       | 15.3.1                | 64-Hz Counter (R64CNT)                         |     |  |

|       | 15.3.2                | Second Counter (RSECCNT)                       |     |  |

|       | 15.3.3                | Minute Counter (RMINCNT)                       |     |  |

|       | 15.3.4                | Hour Counter (RHRCNT)                          |     |  |

|       | 15.3.5                | Day of Week Counter (RWKCNT)                   |     |  |

|       | 15.3.6                | Date Counter (RDAYCNT)                         |     |  |

|       | 15.3.7                | Month Counter (RMONCNT)                        |     |  |

|       | 15.3.8                | Year Counter (RYRCNT)                          |     |  |

|       | 15.3.9                | Second Alarm Register (RSECAR)                 |     |  |

|       | 15.3.10               | Minute Alarm Register (RMINAR)                 |     |  |

|       | 15.3.11               | Hour Alarm Register (RHRAR)                    |     |  |

|       | 15.3.12               | Day of Week Alarm Register (RWKAR)             |     |  |

|       | 15.3.13               | Date Alarm Register (RDAYAR)                   |     |  |

|       | 15.3.14               | Month Alarm Register (RMONAR)                  |     |  |

|       | 15.3.15               | Year Alarm Register (RYRAR)                    | 669 |  |

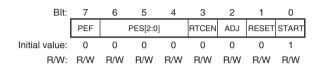

|       | 15.3.16               | Control Register 1 (RCR1)                      | 670 |  |

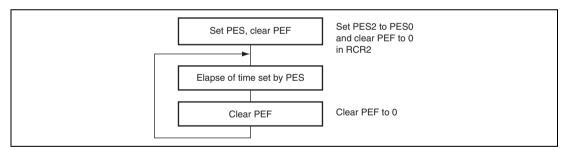

|       | 15.3.17               | Control Register 2 (RCR2)                      |     |  |

|       | 15.3.18               | Control Register 3 (RCR3)                      |     |  |

|       | 15.3.19               | Control Register 5 (RCR5)                      |     |  |

|       | 15.3.20               | Frequency Register H/L (RFRH/L)                |     |  |

| 15.4  | Operation 679         |                                                |     |  |

|       | 15.4.1    | Initial Settings of Registers after Power-On and Oscillation Settling Time | 679 |

|-------|-----------|----------------------------------------------------------------------------|-----|

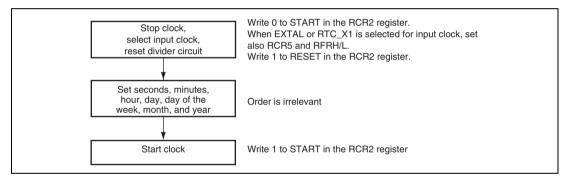

|       | 15.4.2    | Setting Time                                                               | 679 |

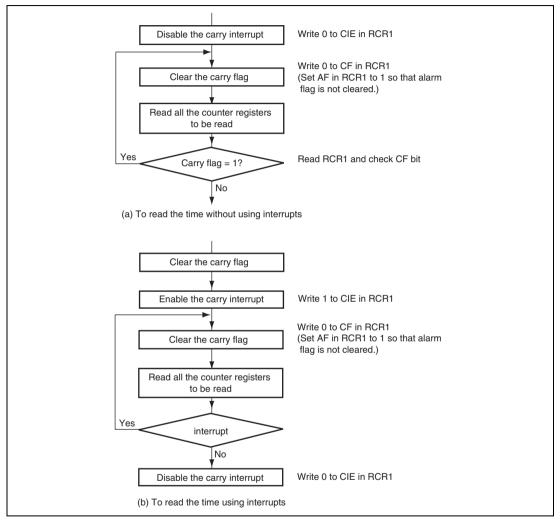

|       | 15.4.3    | Reading Time                                                               | 680 |

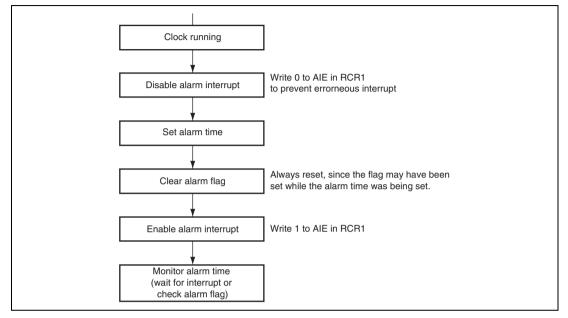

|       | 15.4.4    | Alarm Function                                                             | 681 |

| 15.5  | Usage N   | otes                                                                       | 682 |

|       | 15.5.1    | Register Writing during Count                                              | 682 |

|       | 15.5.2    | Use of Realtime Clock Periodic Interrupts                                  | 682 |

|       | 15.5.3    | Transition to Standby Mode after Setting Register                          | 682 |

|       | 15.5.4    | Usage Notes when Writing to and Reading the Register                       | 683 |

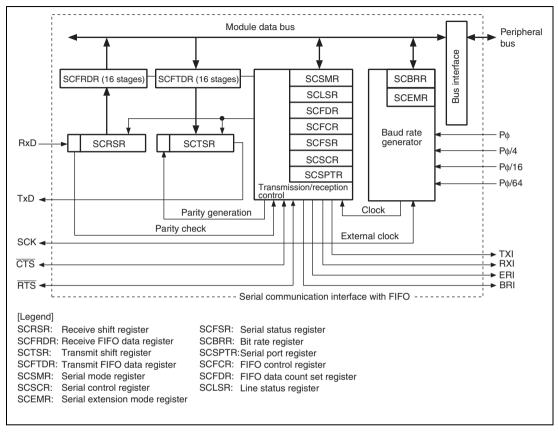

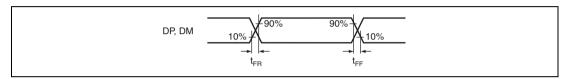

| Secti | on 16 Se  | erial Communication Interface with FIFO                                    | 685 |

| 16.1  | Features  |                                                                            | 685 |

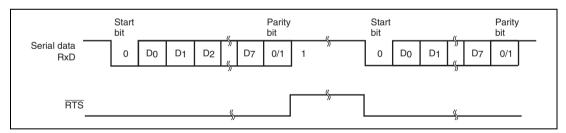

| 16.2  | Input/Ou  | ıtput Pins                                                                 | 688 |

| 16.3  | Register  | Descriptions                                                               | 689 |

|       | 16.3.1    | Receive Shift Register (SCRSR)                                             | 692 |

|       | 16.3.2    | Receive FIFO Data Register (SCFRDR)                                        | 692 |

|       | 16.3.3    | Transmit Shift Register (SCTSR)                                            | 693 |

|       | 16.3.4    | Transmit FIFO Data Register (SCFTDR)                                       | 693 |

|       | 16.3.5    | Serial Mode Register (SCSMR)                                               | 694 |

|       | 16.3.6    | Serial Control Register (SCSCR)                                            | 697 |

|       | 16.3.7    | Serial Status Register (SCFSR)                                             | 701 |

|       | 16.3.8    | Bit Rate Register (SCBRR)                                                  | 709 |

|       | 16.3.9    | FIFO Control Register (SCFCR)                                              | 715 |

|       | 16.3.10   | FIFO Data Count Set Register (SCFDR)                                       | 718 |

|       | 16.3.11   | Serial Port Register (SCSPTR)                                              | 719 |

|       | 16.3.12   | Line Status Register (SCLSR)                                               | 722 |

|       | 16.3.13   | Serial Extension Mode Register (SCEMR)                                     | 723 |

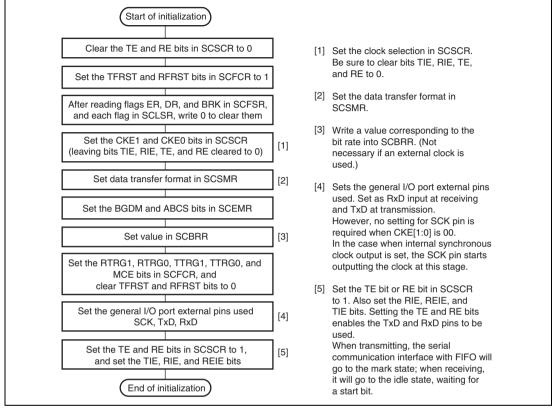

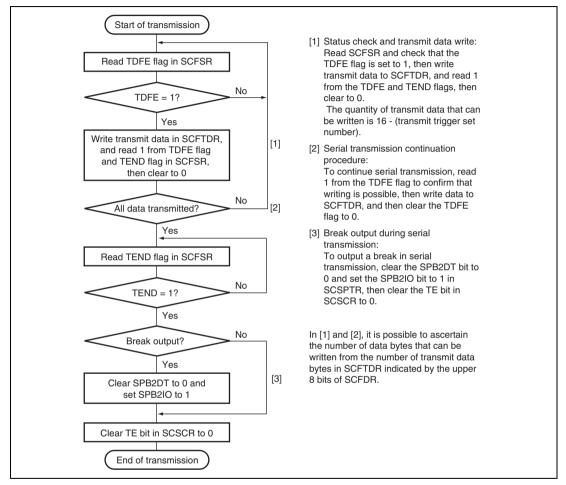

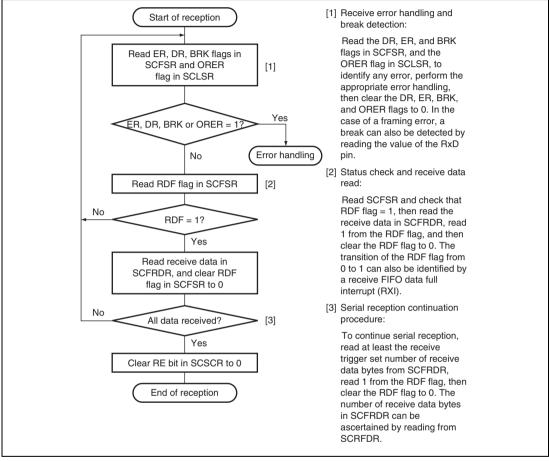

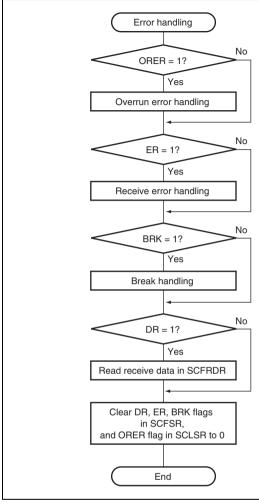

| 16.4  | Operation | on                                                                         | 724 |

|       | 16.4.1    | Overview                                                                   | 724 |

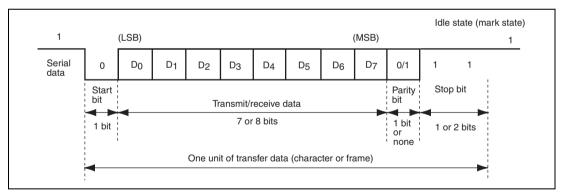

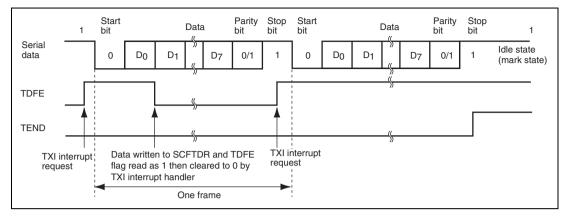

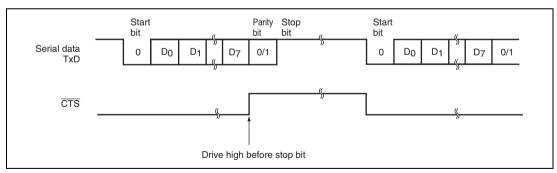

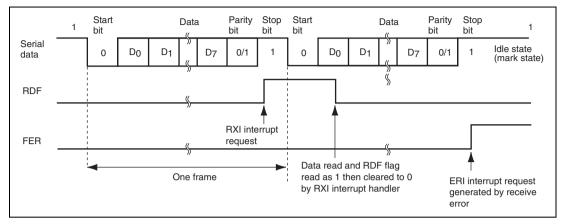

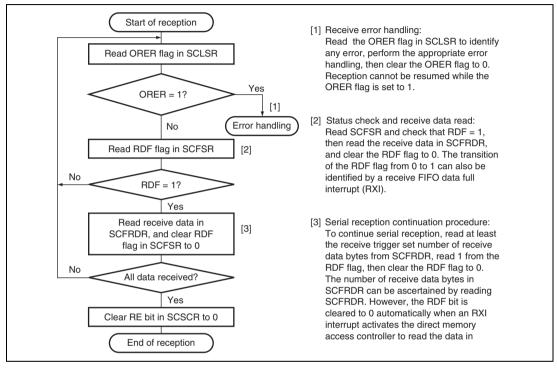

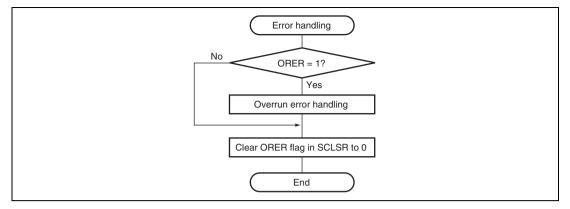

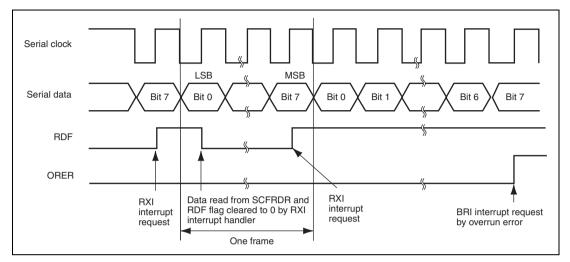

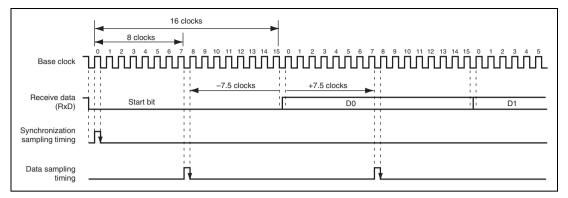

|       | 16.4.2    | Operation in Asynchronous Mode                                             | 727 |

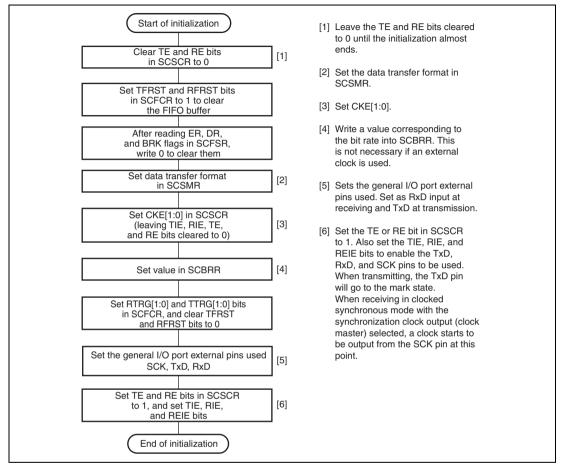

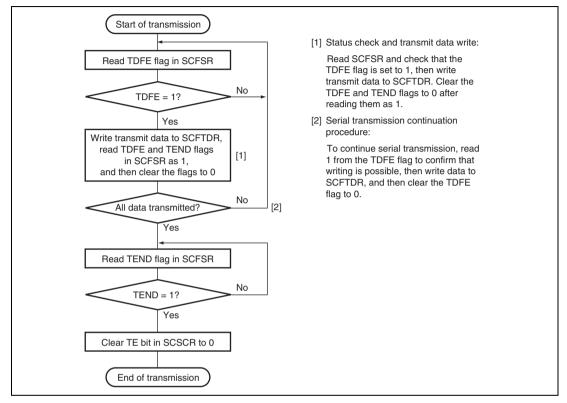

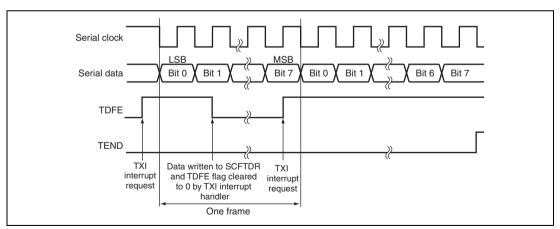

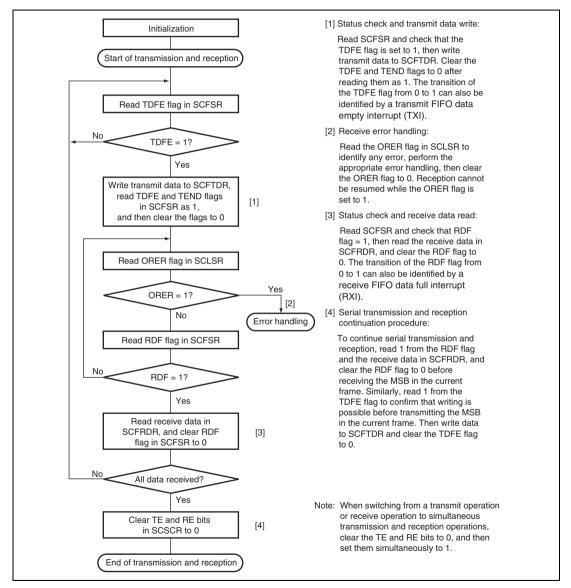

|       | 16.4.3    | Operation in Clock Synchronous Mode                                        | 738 |

| 16.5  | Interrupt | ts                                                                         | 747 |

| 16.6  | Usage N   | otes                                                                       | 748 |

|       | 16.6.1    | SCFTDR Writing and TDFE Flag                                               | 748 |

|       | 16.6.2    | SCFRDR Reading and RDF Flag                                                | 748 |

|       | 16.6.3    | Restriction on Direct Memory Controller Usage                              |     |

|       | 16.6.4    | Break Detection and Processing                                             | 749 |

|       | 16.6.5    | Sending a Break Signal                                                     | 749 |

|       | 16.6.6    | Receive Data Sampling Timing and Receive Margin                            |     |

|       |           | (Asynchronous Mode)                                                        | 749 |

|       | 16.6.7    | Selection of Base Clock in Asynchronous Mode | 751 |

|-------|-----------|----------------------------------------------|-----|

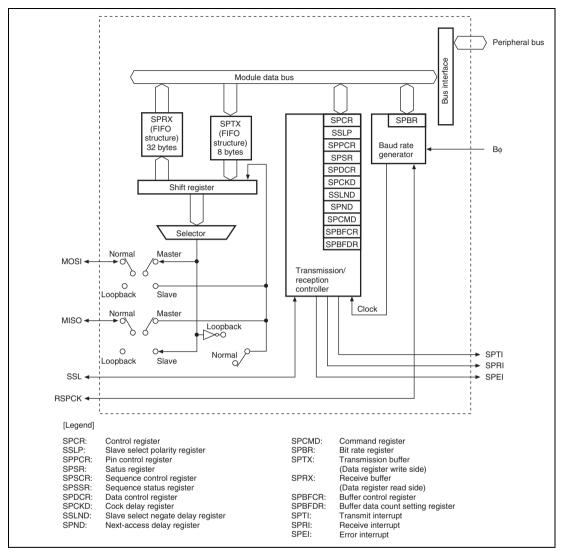

| Secti | ion 17 Re | enesas Serial Peripheral Interface           | 753 |

| 17.1  | Features  | S                                            | 753 |

| 17.2  | Input/Ou  | utput Pins                                   | 756 |

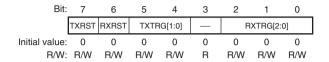

| 17.3  | Register  | Descriptions                                 | 757 |

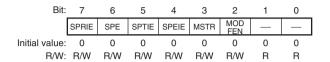

|       | 17.3.1    | Control Register (SPCR)                      | 760 |

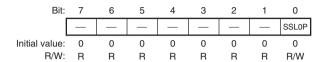

|       | 17.3.2    | Slave Select Polarity Register (SSLP)        | 762 |

|       | 17.3.3    | Pin Control Register (SPPCR)                 | 763 |

|       | 17.3.4    | Status Register (SPSR)                       | 765 |

|       | 17.3.5    | Data Register (SPDR)                         | 768 |

|       | 17.3.6    | Sequence Control Register (SPSCR)            | 769 |

|       | 17.3.7    | Sequence Status Register (SPSSR)             | 771 |

|       | 17.3.8    | Bit Rate Register (SPBR)                     | 772 |

|       | 17.3.9    | Data Control Register (SPDCR)                | 774 |

|       | 17.3.10   | Clock Delay Register (SPCKD)                 | 776 |

|       | 17.3.11   | Slave Select Negation Delay Register (SSLND) | 777 |

|       | 17.3.12   | Next-Access Delay Register (SPND)            | 778 |

|       | 17.3.13   | Command Register (SPCMD)                     | 779 |

|       | 17.3.14   | Buffer Control Register (SPBFCR)             | 784 |

|       | 17.3.15   | Buffer Data Count Setting Register (SPBFDR)  | 786 |

| 17.4  | Operation | on                                           | 787 |

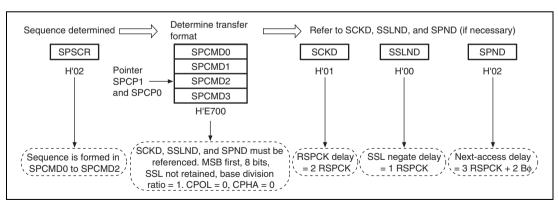

|       | 17.4.1    | Overview of Operations                       | 787 |

|       | 17.4.2    | Pin Control                                  | 788 |

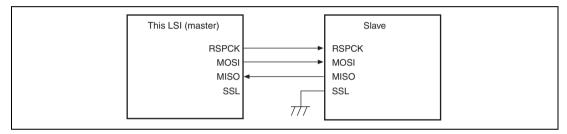

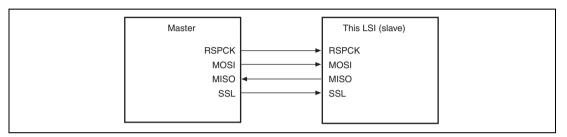

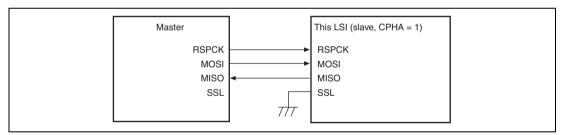

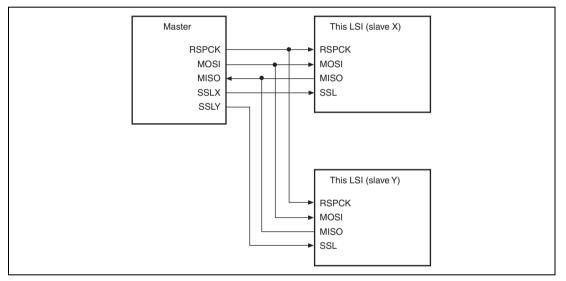

|       | 17.4.3    | System Configuration Example                 | 789 |

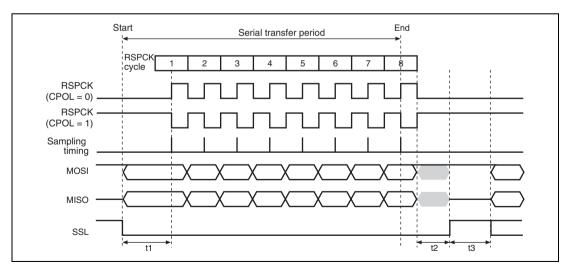

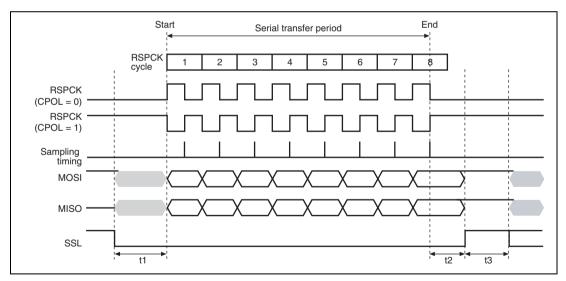

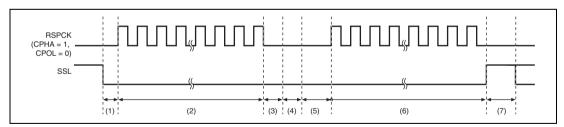

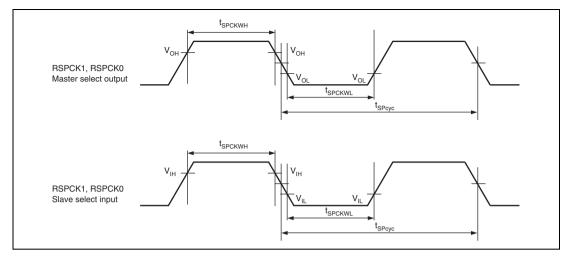

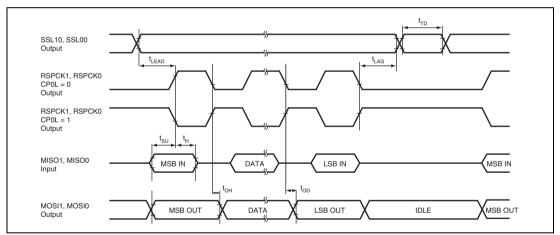

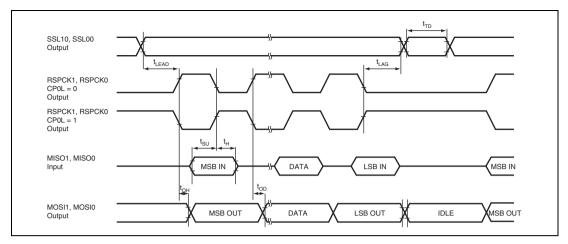

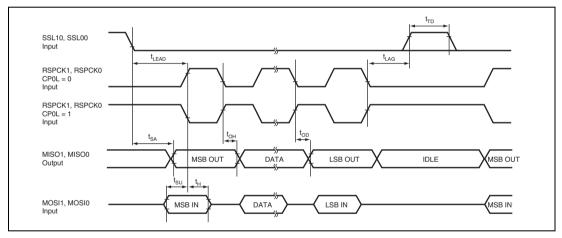

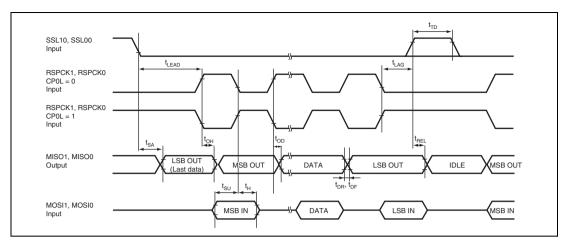

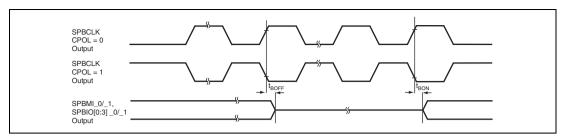

|       | 17.4.4    | Transfer Format                              | 792 |

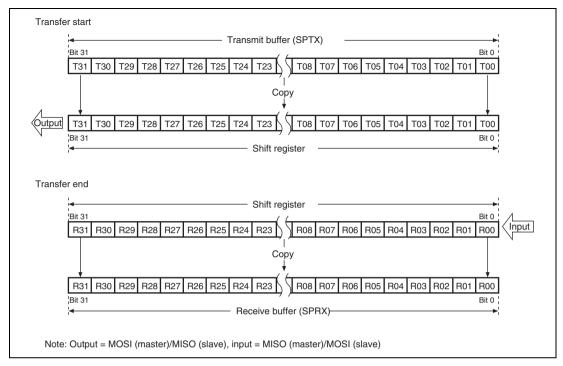

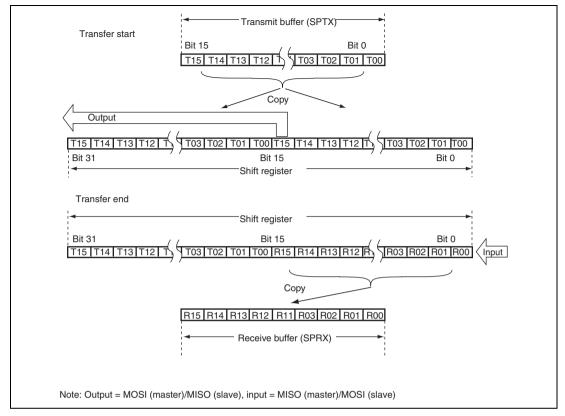

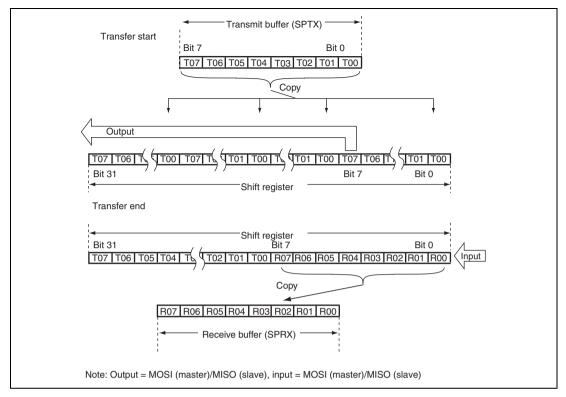

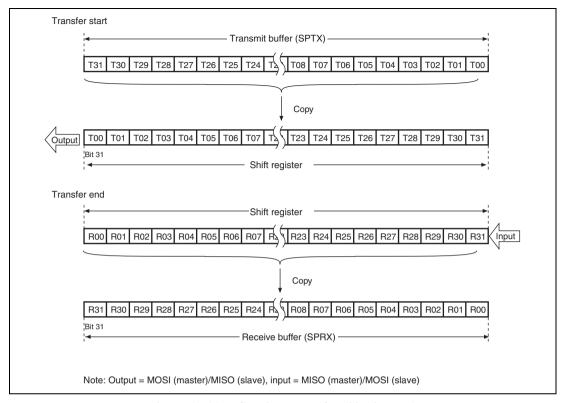

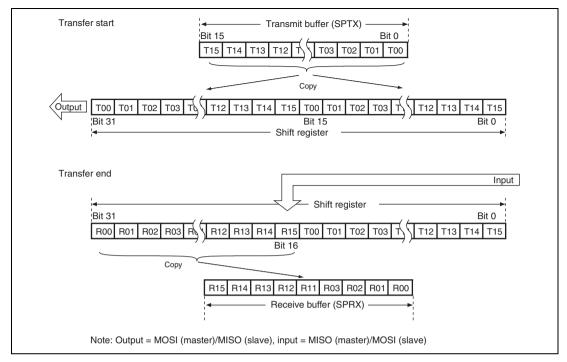

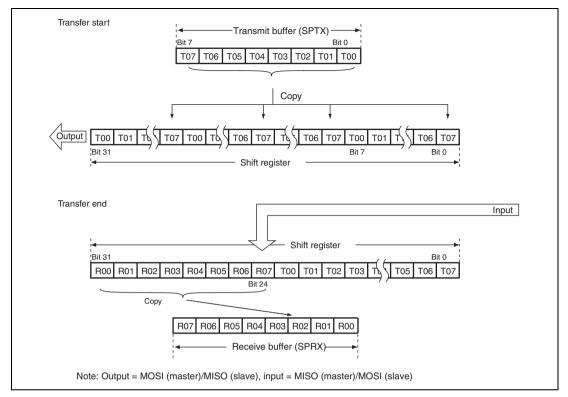

|       | 17.4.5    | Data Format                                  | 794 |

|       | 17.4.6    | Error Detection                              | 806 |

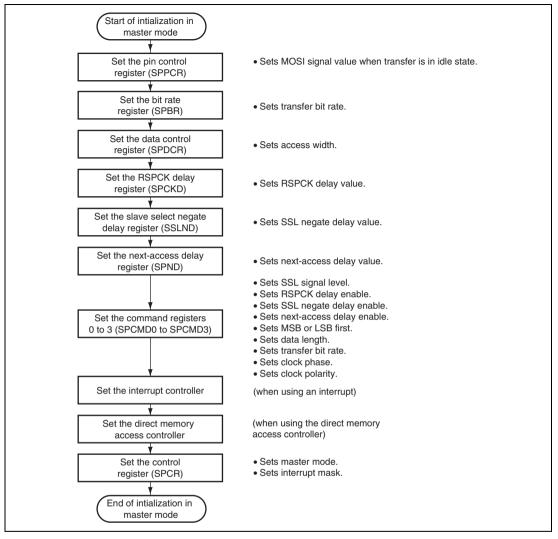

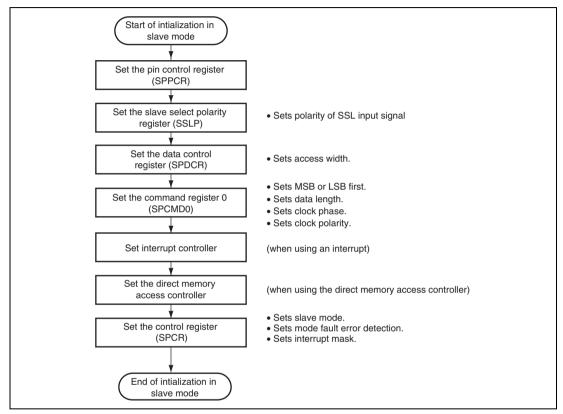

|       | 17.4.7    | Initialization                               | 811 |

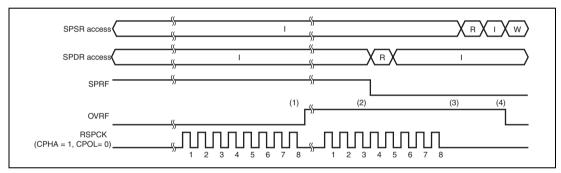

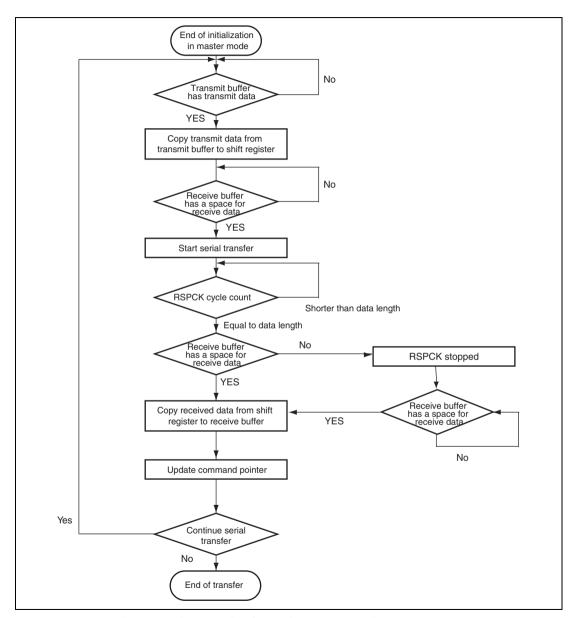

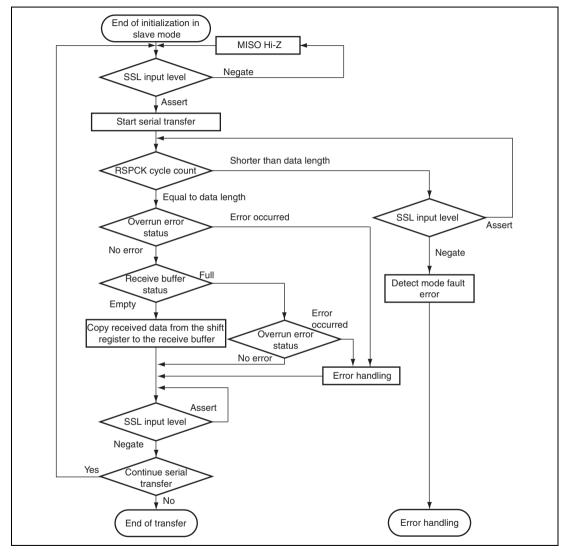

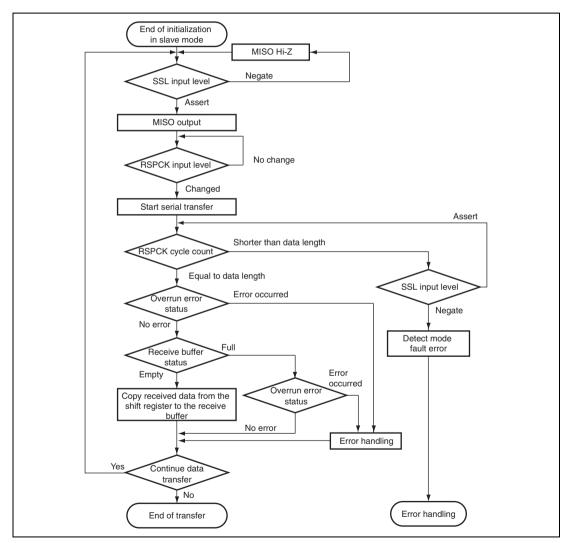

|       | 17.4.8    | SPI Operation                                | 812 |

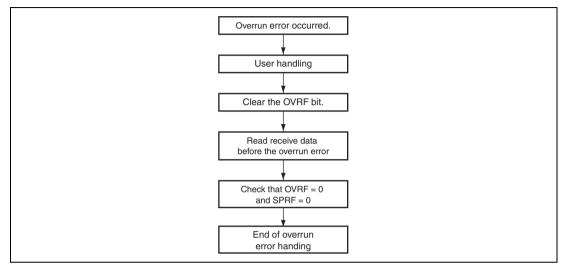

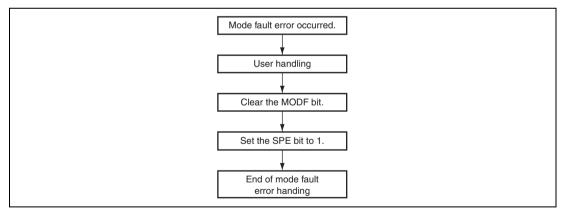

|       | 17.4.9    | Error Handling                               | 825 |

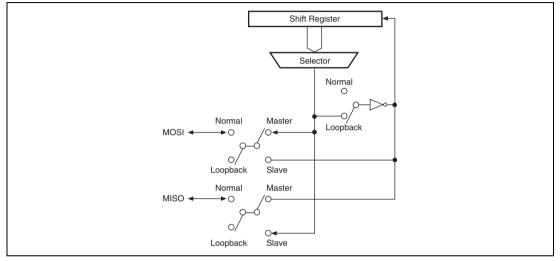

|       | 17.4.10   | Loopback Mode                                | 826 |

|       | 17.4.11   | Interrupt Sources                            | 827 |

| Secti | ion 18 SI | PI Multi I/O Bus Controller                  | 829 |

| 18.1  | Features  | 5                                            | 829 |

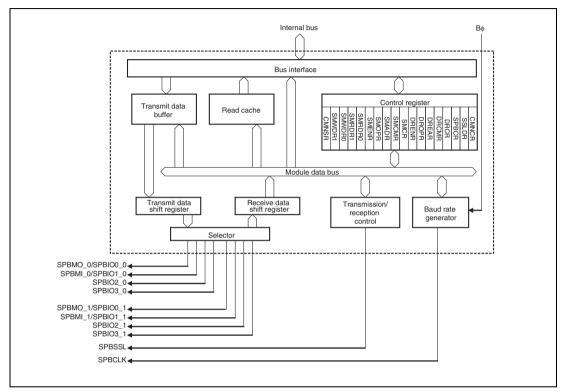

| 18.2  | Block D   | viagram                                      | 830 |

| 18.3  | Input/Ou  | utput Pins                                   | 831 |

| 18.4  | Register  | · Descriptions                               | 832 |

|       | 18.4.1    | Common Control Register (CMNCR)              | 833 |

|      | 18.4.2    | SSL Delay Register (SSLDR)                                       | 838 |

|------|-----------|------------------------------------------------------------------|-----|

|      | 18.4.3    | Bit Rate Register (SPBCR)                                        | 840 |

|      | 18.4.4    | Data Read Control Register (DRCR)                                | 842 |

|      | 18.4.5    | Data Read Command Setting Register (DRCMR)                       | 845 |

|      | 18.4.6    | Data Read Extended Address Setting Register (DREAR)              | 846 |

|      | 18.4.7    | Data Read Option Setting Register (DROPR)                        | 848 |

|      | 18.4.8    | Data Read Enable Setting Register (DRENR)                        | 849 |

|      | 18.4.9    | SPI Mode Control Register (SMCR)                                 | 853 |

|      | 18.4.10   | SPI Mode Command Setting Register (SMCMR)                        |     |

|      | 18.4.11   | SPI Mode Address Setting Register (SMADR)                        | 856 |

|      | 18.4.12   | SPI Mode Option Setting Register (SMOPR)                         |     |

|      | 18.4.13   | SPI Mode Enable Setting Register (SMENR)                         | 858 |

|      | 18.4.14   | SPI Mode Read Data Register 0 (SMRDR0)                           |     |

|      | 18.4.15   | SPI Mode Read Data Register 1 (SMRDR1)                           | 863 |

|      | 18.4.16   | SPI Mode Write Data Register 0 (SMWDR0)                          |     |

|      | 18.4.17   | SPI Mode Write Data Register 1 (SMWDR1)                          | 865 |

|      | 18.4.18   | Common Status Register (CMNSR)                                   |     |

|      | 18.4.19   | AC Characteristics Adjustment Register (SPBACR)                  |     |

| 18.5 | Operation |                                                                  | 868 |

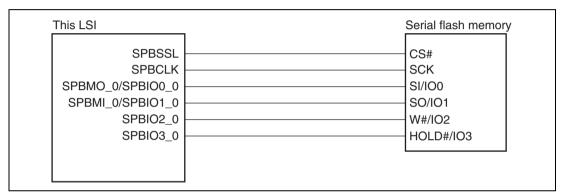

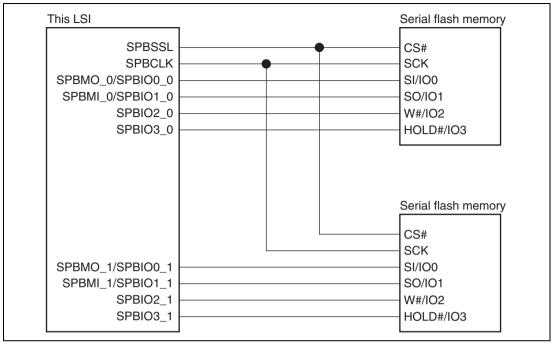

|      | 18.5.1    | System Configuration                                             | 868 |

|      | 18.5.2    | Address Map                                                      | 869 |

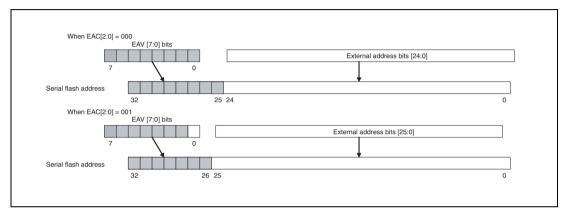

|      | 18.5.3    | 32-bit Serial Flash Addresses                                    | 870 |

|      | 18.5.4    | Data Alignment                                                   | 871 |

|      | 18.5.5    | Operating Modes                                                  | 871 |

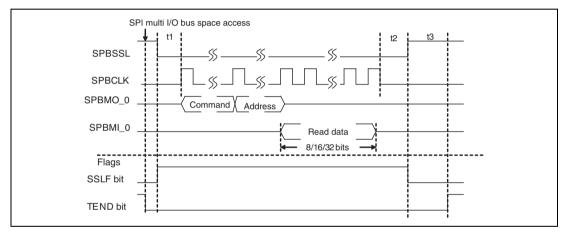

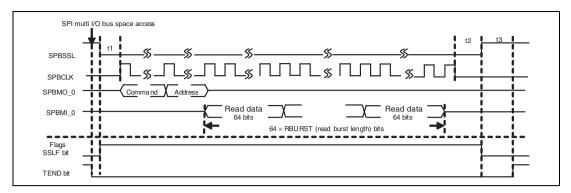

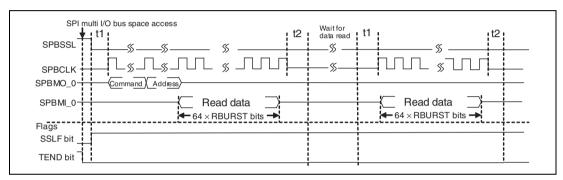

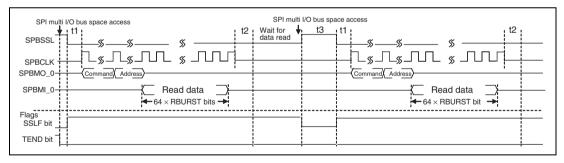

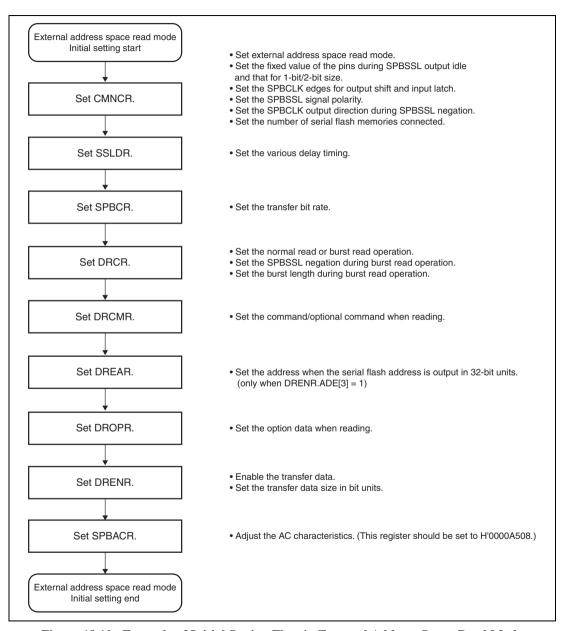

|      | 18.5.6    | External Address Space Read Mode                                 | 871 |

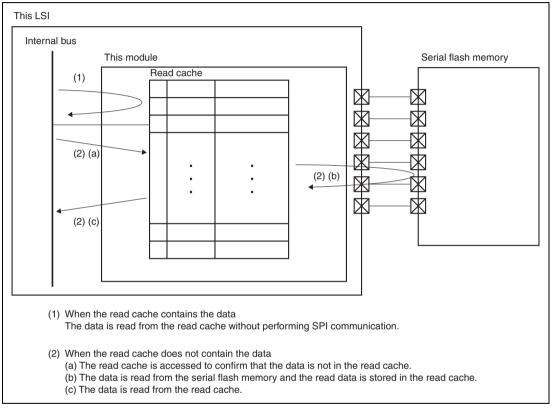

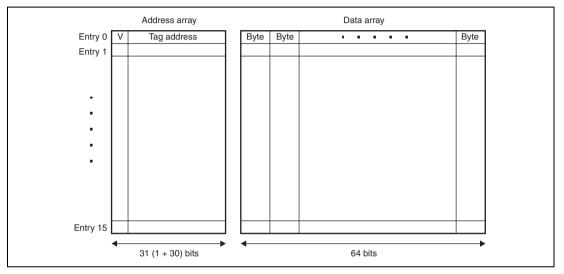

|      | 18.5.7    | Read Cache                                                       | 877 |

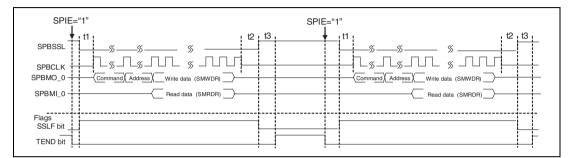

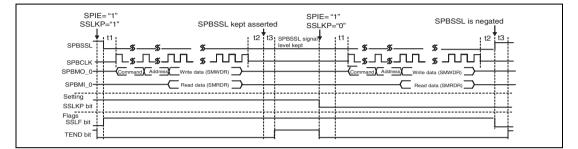

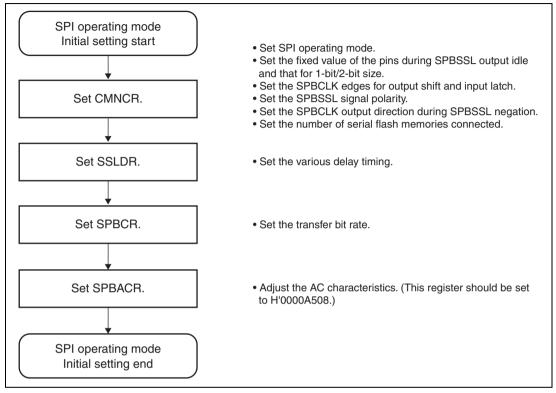

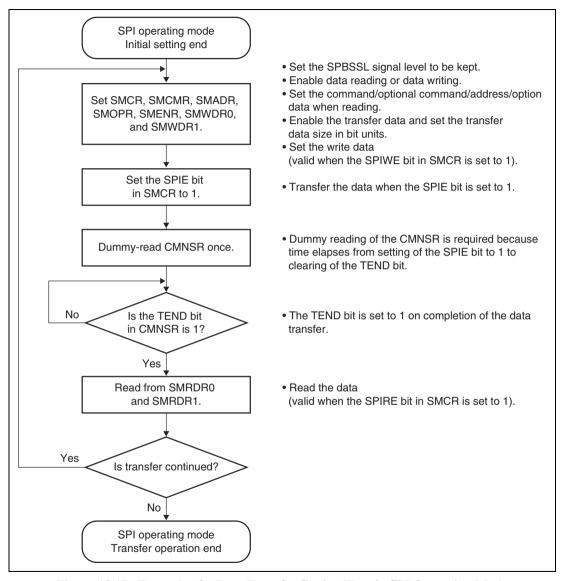

|      | 18.5.8    | SPI Operating Mode                                               | 878 |

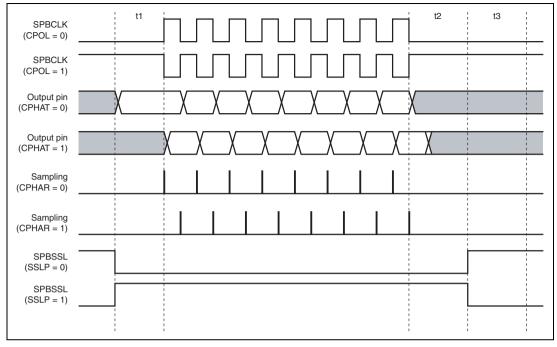

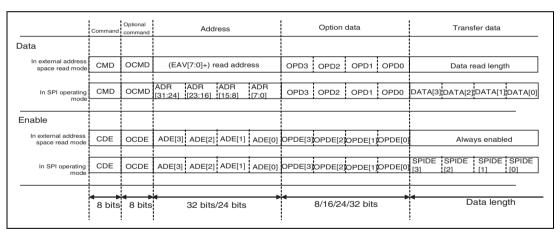

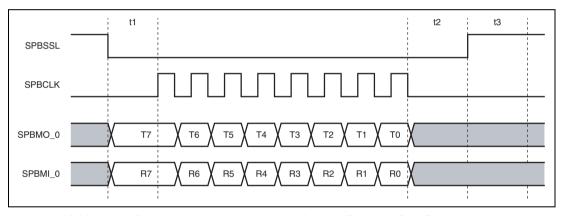

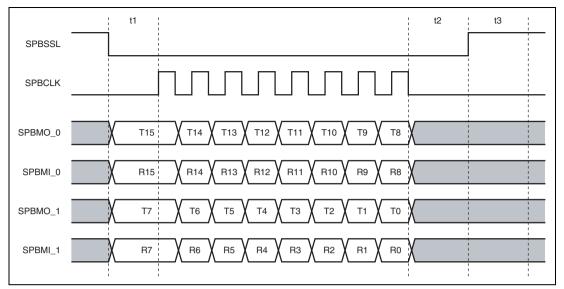

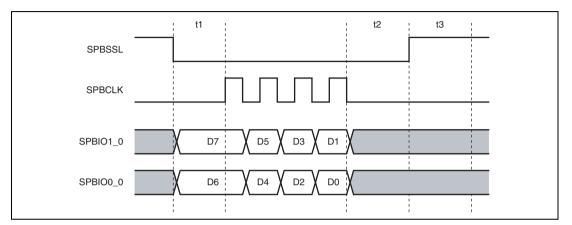

|      | 18.5.9    | Transfer Format                                                  | 883 |

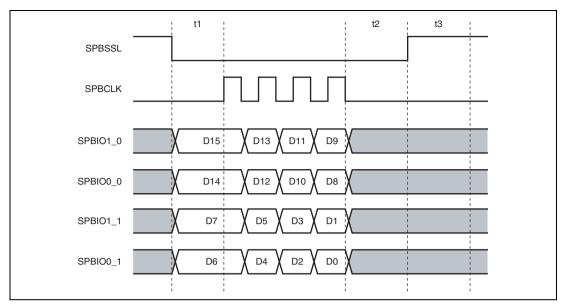

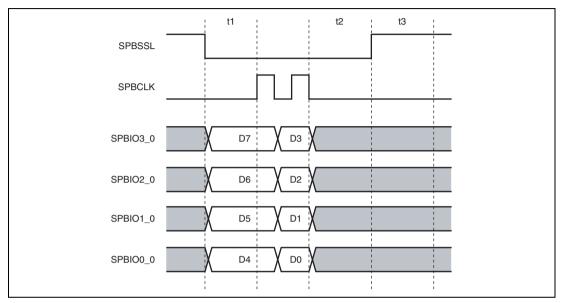

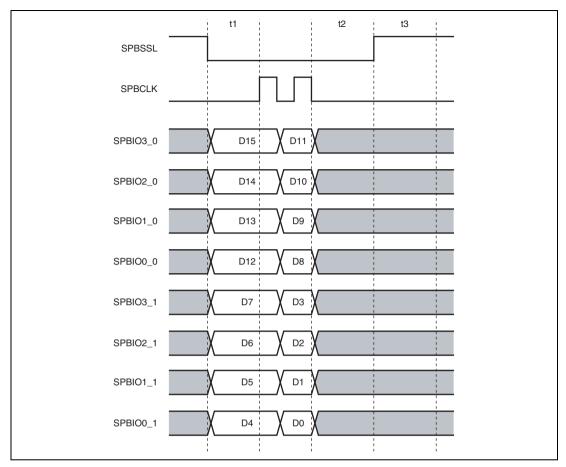

|      | 18.5.10   | Data Format                                                      | 885 |

|      | 18.5.11   | Data Pin Control                                                 | 893 |

|      | 18.5.12   | SPBSSL Pin Control                                               | 895 |

|      | 18.5.13   | Flags                                                            | 896 |

| 18.6 | Usage N   | otes                                                             | 897 |

|      | 18.6.1    | Notes on Transfer to Read Data in SPI Operating Mode             | 897 |

|      | 18.6.2    | Notes on Starting Transfer from the SPBSSL Retained State in SPI |     |

|      |           | Operating Mode                                                   | 897 |

|      | 18.6.3    | Note on Initialization                                           | 897 |

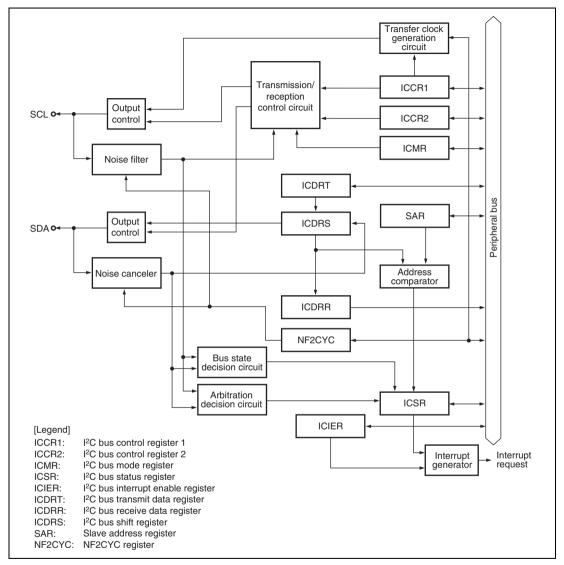

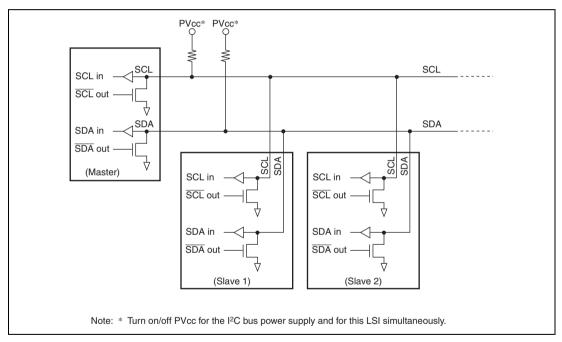

| Secti | ection 19 I <sup>2</sup> C Bus Interface 3 |                                                                   |       |

|-------|--------------------------------------------|-------------------------------------------------------------------|-------|

| 19.1  | Features                                   | S                                                                 | 899   |

| 19.2  | Input/Output Pins                          |                                                                   | 901   |

| 19.3  | Register Descriptions                      |                                                                   | 902   |

|       | 19.3.1                                     | I <sup>2</sup> C Bus Control Register 1 (ICCR1)                   | 903   |

|       | 19.3.2                                     | I <sup>2</sup> C Bus Control Register 2 (ICCR2)                   | 906   |

|       | 19.3.3                                     | I <sup>2</sup> C Bus Mode Register (ICMR)                         | 908   |

|       | 19.3.4                                     | I <sup>2</sup> C Bus Interrupt Enable Register (ICIER)            | 910   |

|       | 19.3.5                                     | I <sup>2</sup> C Bus Status Register (ICSR)                       | 912   |

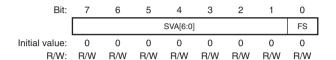

|       | 19.3.6                                     | Slave Address Register (SAR)                                      |       |

|       | 19.3.7                                     | I <sup>2</sup> C Bus Transmit Data Register (ICDRT)               | 915   |

|       | 19.3.8                                     | I <sup>2</sup> C Bus Receive Data Register (ICDRR)                | 916   |

|       | 19.3.9                                     | I <sup>2</sup> C Bus Shift Register (ICDRS)                       |       |

|       | 19.3.10                                    | NF2CYC Register (NF2CYC)                                          | 917   |

| 19.4  | Operation                                  | on                                                                | 918   |

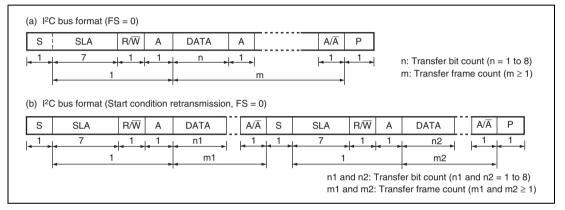

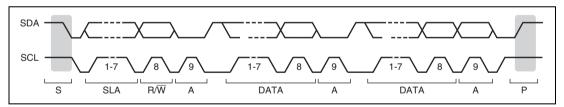

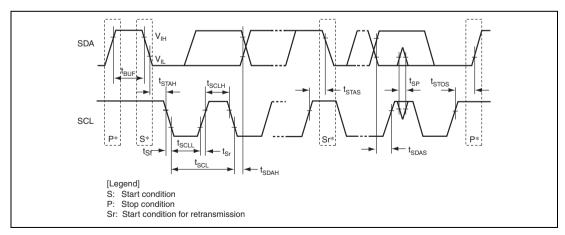

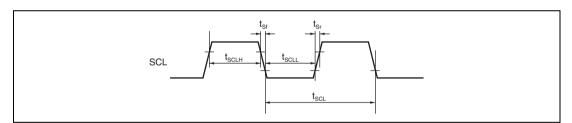

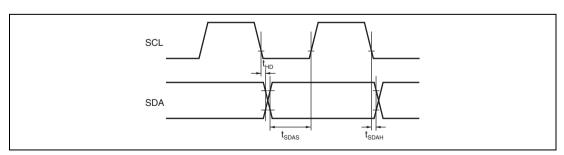

|       | 19.4.1                                     | I <sup>2</sup> C Bus Format                                       | 918   |

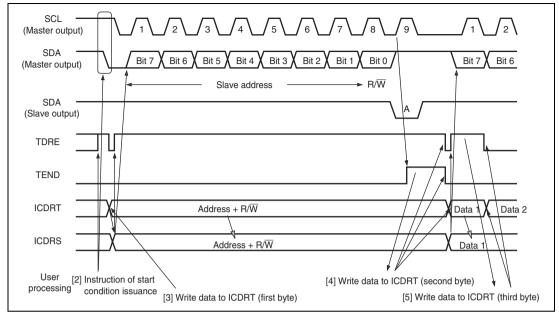

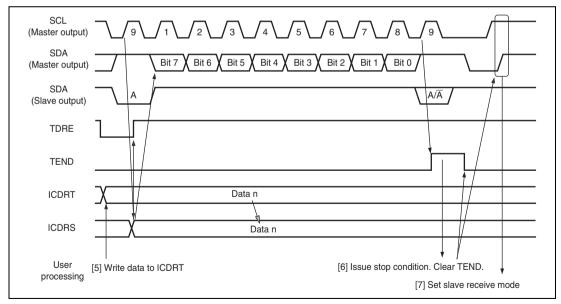

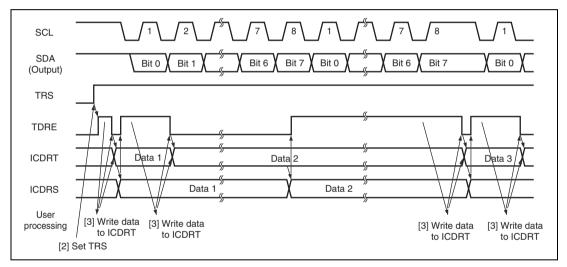

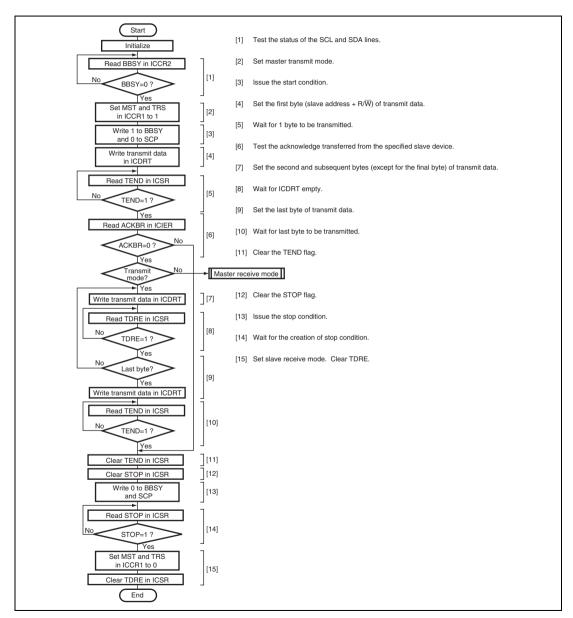

|       | 19.4.2                                     | Master Transmit Operation                                         | 919   |

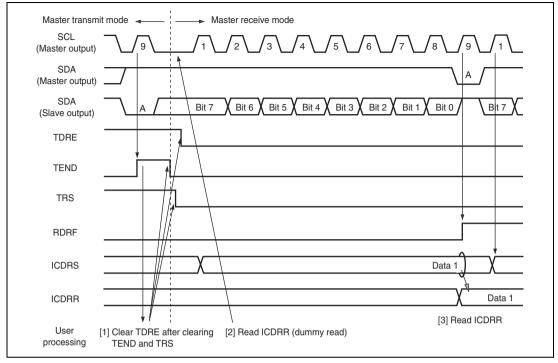

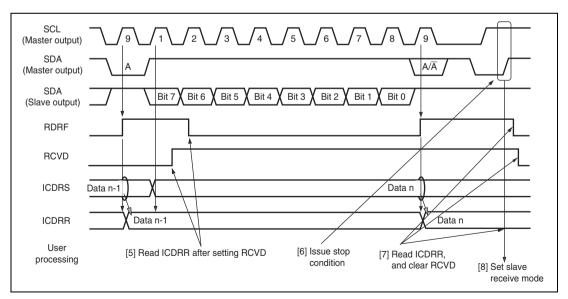

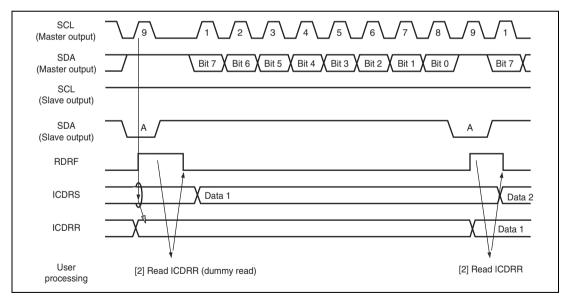

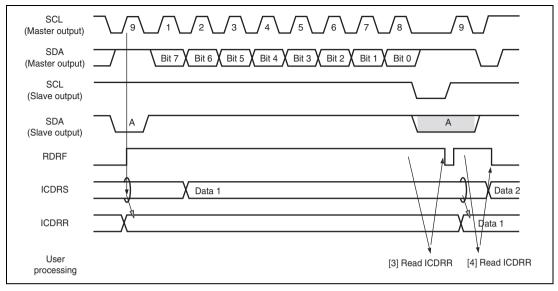

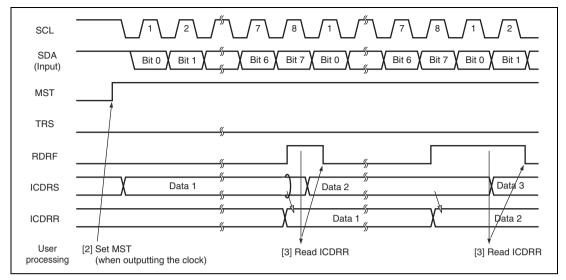

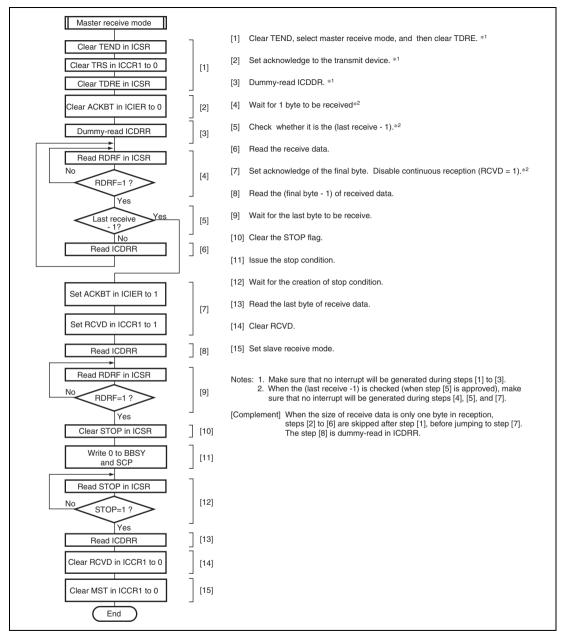

|       | 19.4.3                                     | Master Receive Operation                                          |       |

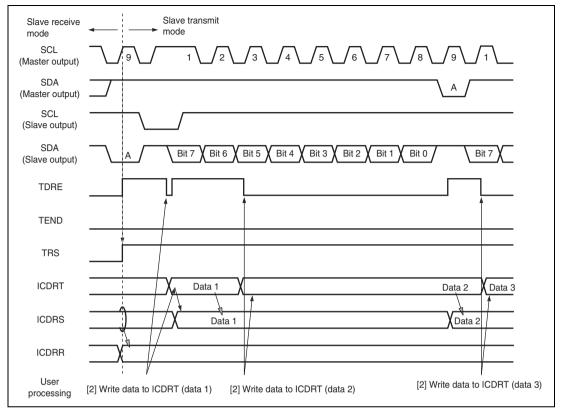

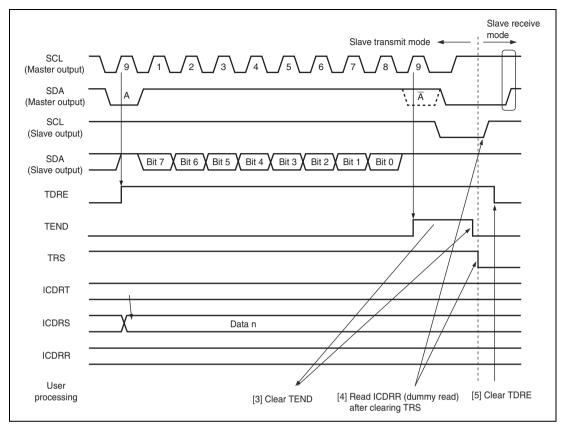

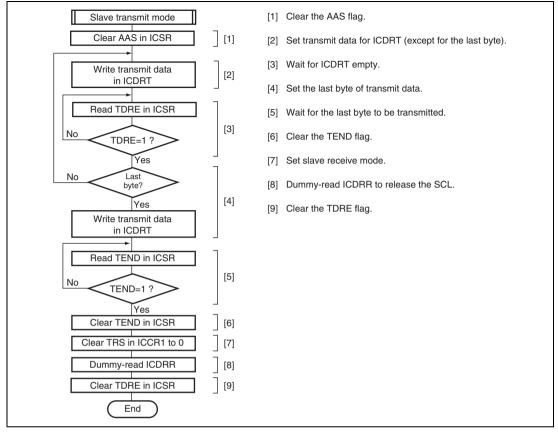

|       | 19.4.4                                     | Slave Transmit Operation                                          |       |

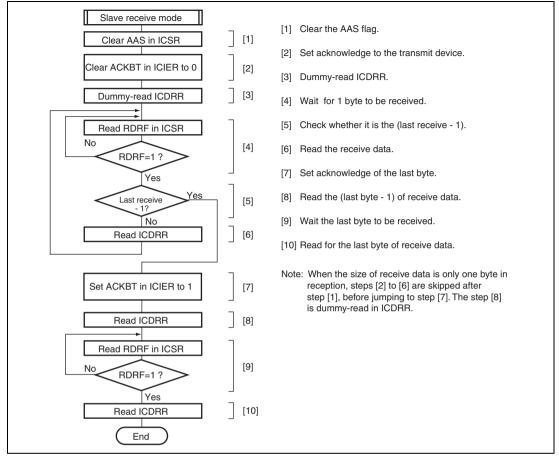

|       | 19.4.5                                     | Slave Receive Operation                                           |       |

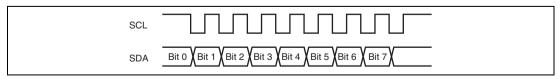

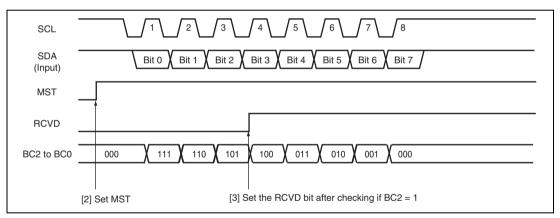

|       | 19.4.6                                     | Clocked Synchronous Serial Format                                 |       |

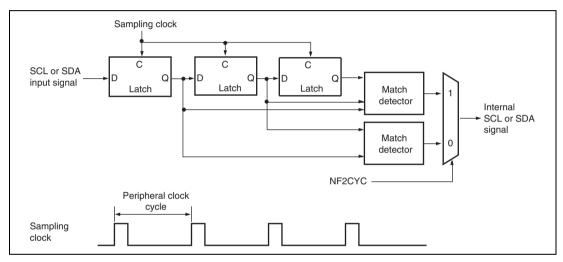

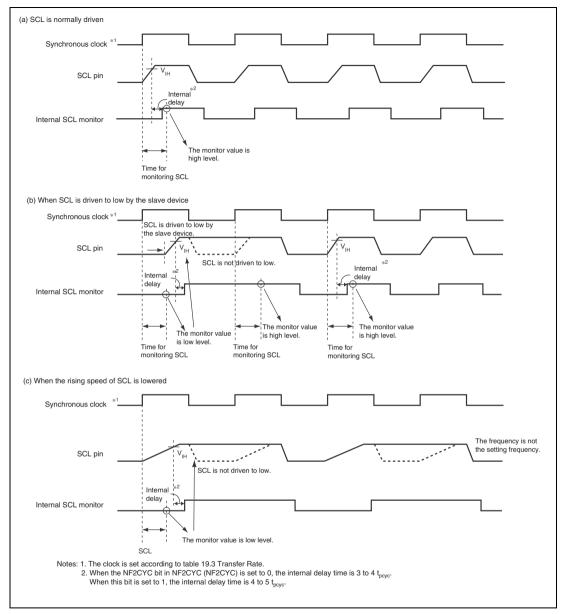

|       | 19.4.7                                     | Noise Filter                                                      | 931   |

|       | 19.4.8                                     | Example of Use                                                    | 932   |

| 19.5  | Interrup                                   | t Requests                                                        | 936   |

| 19.6  | Bit Syno                                   | chronous Circuit                                                  | 937   |

| 19.7  | Usage N                                    | Notes                                                             | 939   |

|       | 19.7.1                                     | Note on Setting for Multi-Master Operation                        |       |

|       | 19.7.2                                     | Note on Master Receive Mode                                       |       |

|       | 19.7.3                                     | Note on Setting ACKBT in Master Receive Mode                      |       |

|       | 19.7.4                                     | Note on the States of Bits MST and TRN when Arbitration is Lost   | 940   |

|       | 19.7.5                                     | Note on I <sup>2</sup> C-bus Interface Master Receive Mode        | 940   |

|       | 19.7.6                                     | Note on IICRST and BBSY bits                                      |       |

|       | 19.7.7                                     | Note on Issuance of Stop Conditions in Master Transmit Mode while |       |

|       |                                            | ACKE = 1                                                          | 940   |

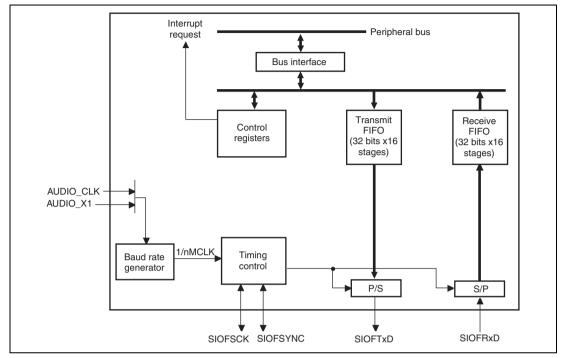

| Secti | on 20 S                                    | erial Sound Interface                                             | 941   |

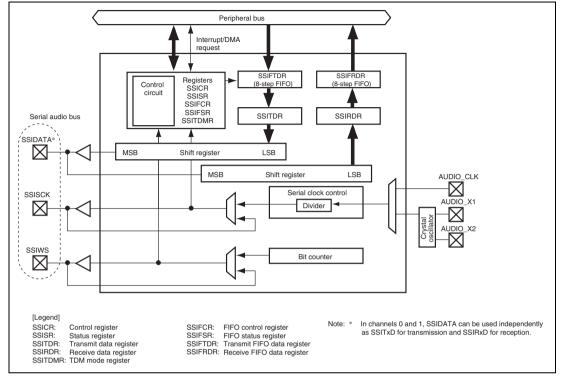

| 20.1  |                                            | 3                                                                 |       |

| 20.2  |                                            | utput Pins                                                        |       |

| 20.3  | • •                                        |                                                                   | 0.4.4 |

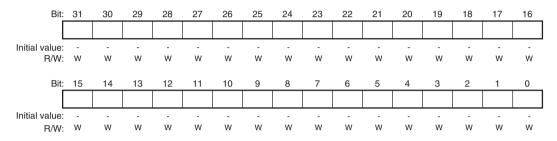

|       | 20.3.1      | Control Register (SSICR)                                         | 946  |

|-------|-------------|------------------------------------------------------------------|------|

|       | 20.3.2      | Status Register (SSISR)                                          | 953  |

|       | 20.3.3      | Transmit Data Register (SSITDR)                                  | 957  |

|       | 20.3.4      | Receive Data Register (SSIRDR)                                   | 957  |

|       | 20.3.5      | FIFO Control Register (SSIFCR)                                   | 958  |

|       | 20.3.6      | FIFO Status Register (SSIFSR)                                    | 961  |

|       | 20.3.7      | Transmit FIFO Data Register (SSIFTDR)                            | 964  |

|       | 20.3.8      | Receive FIFO Data Register (SSIFRDR)                             | 965  |

|       | 20.3.9      | TDM Mode Register (SSITDMR)                                      | 966  |

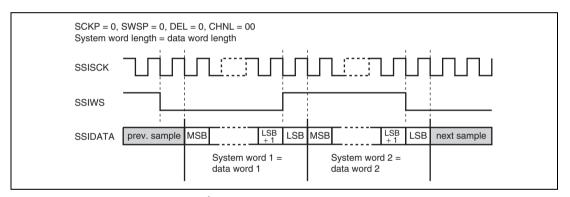

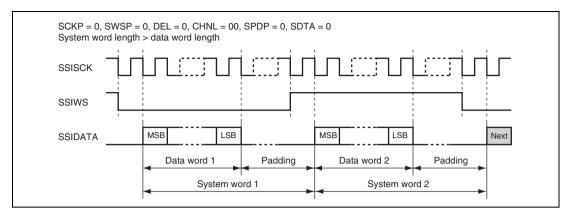

| 20.4  | Operation   | on Description                                                   | 967  |

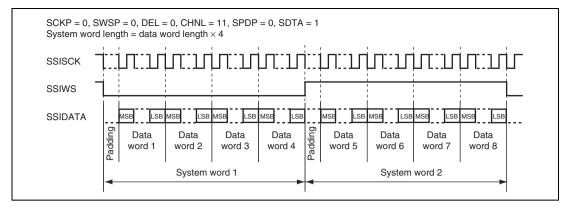

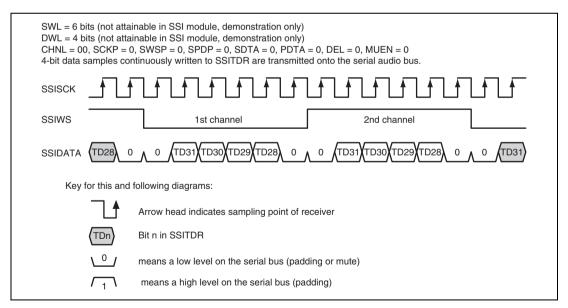

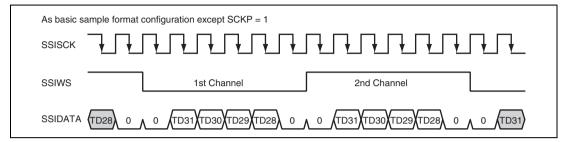

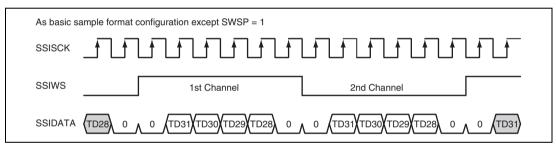

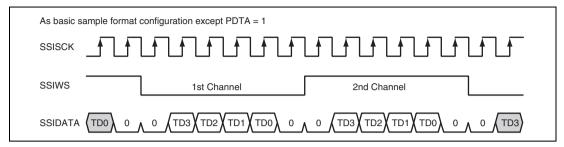

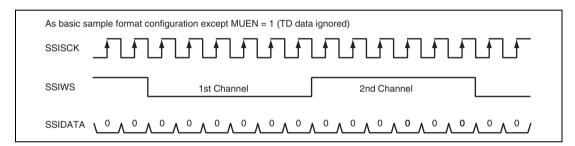

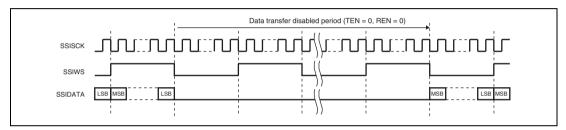

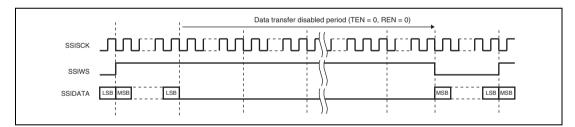

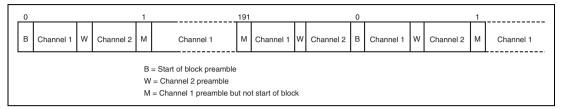

|       | 20.4.1      | Bus Format                                                       | 967  |

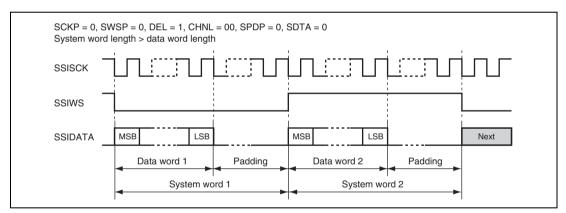

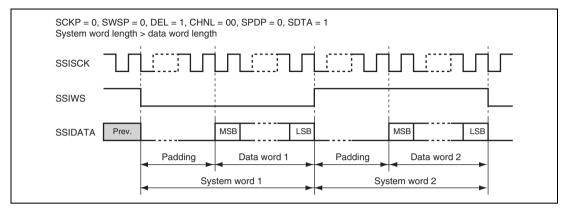

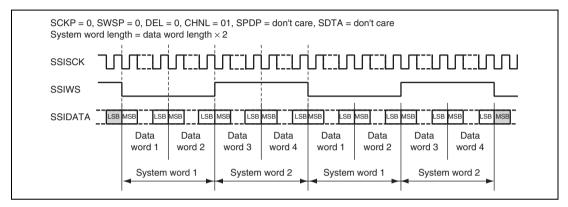

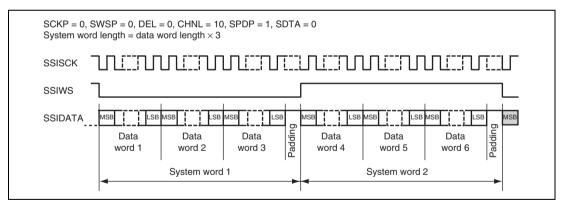

|       | 20.4.2      | Non-Compressed Modes                                             | 969  |

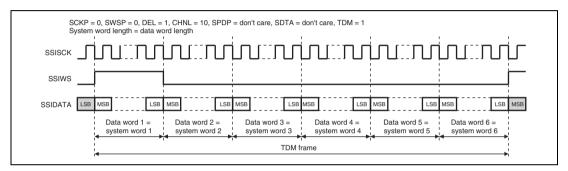

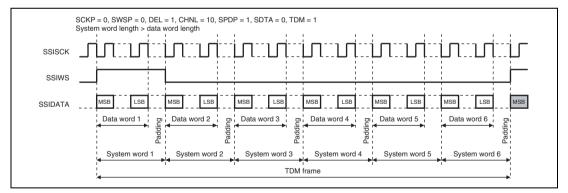

|       | 20.4.3      | TDM Mode                                                         | 980  |

|       | 20.4.4      | WS Continue Mode                                                 | 981  |

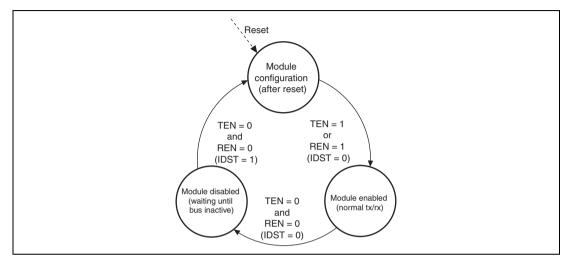

|       | 20.4.5      | Operation Modes                                                  | 982  |

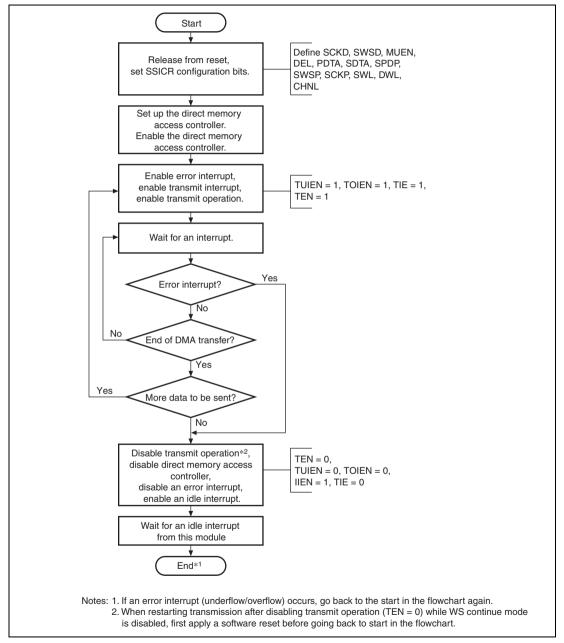

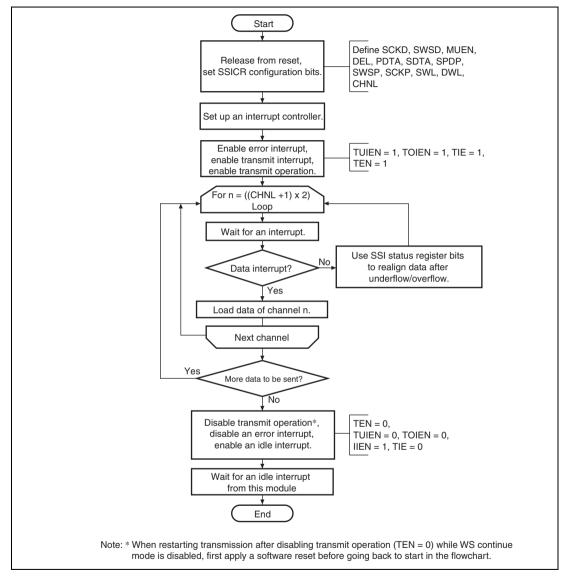

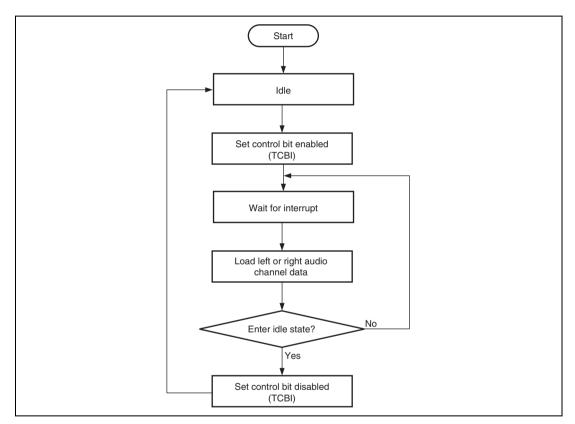

|       | 20.4.6      | Transmit Operation                                               | 983  |

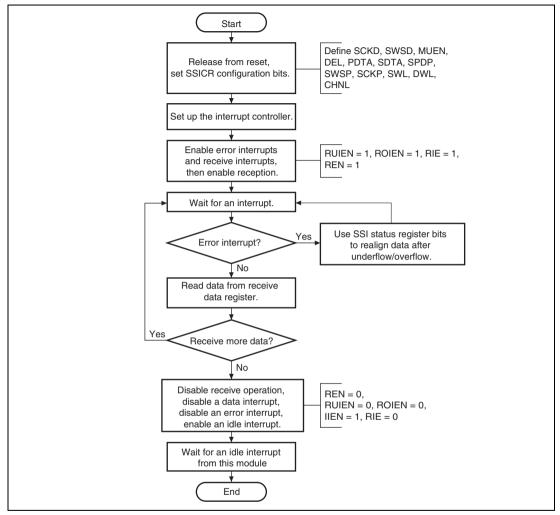

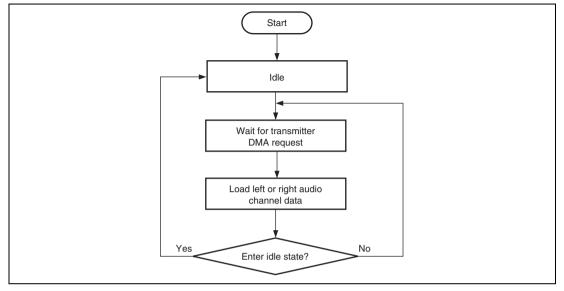

|       | 20.4.7      | Receive Operation                                                | 986  |

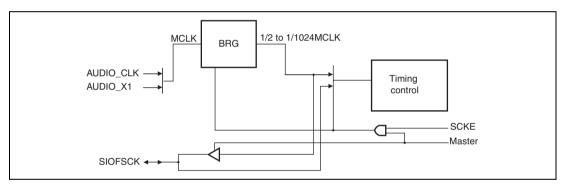

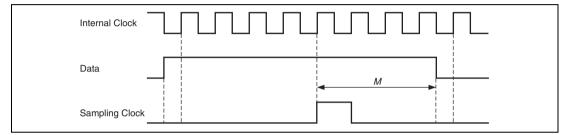

|       | 20.4.8      | Serial Bit Clock Control                                         | 989  |

| 20.5  | Usage Notes |                                                                  | 990  |

|       | 20.5.1      | Limitations from Underflow or Overflow during DMA Operation      | 990  |

|       | 20.5.2      | Note on Changing Mode from Master Transceiver to Master Receiver | 990  |

|       | 20.5.3      | Limits on TDM mode and WS Continue Mode                          | 990  |

| Secti | on 21 Se    | erial I/O with FIFO                                              | 993  |

| 21.1  |             |                                                                  |      |

| 21.2  |             | ıtput Pins                                                       |      |

| 21.3  |             | Descriptions                                                     |      |

|       | 21.3.1      | Mode Register (SIMDR)                                            |      |

|       | 21.3.2      | Control Register (SICTR)                                         |      |

|       | 21.3.3      | Transmit Data Register (SITDR)                                   |      |

|       | 21.3.4      | Receive Data Register (SIRDR)                                    |      |

|       | 21.3.5      | Status Register (SISTR)                                          |      |

|       | 21.3.6      | Interrupt Enable Register (SIIER)                                |      |

|       | 21.3.7      | FIFO Control Register (SIFCTR)                                   |      |

|       | 21.3.8      | Clock Select Register (SISCR)                                    |      |

|       | 21.3.9      | Transmit Data Assign Register (SITDAR)                           |      |

|       | 21.3.10     | Receive Data Assign Register (SIRDAR)                            |      |

| 21.4  | Operation   | on                                                               |      |

|       | 21.4.1      | Serial Clocks                                                    |      |

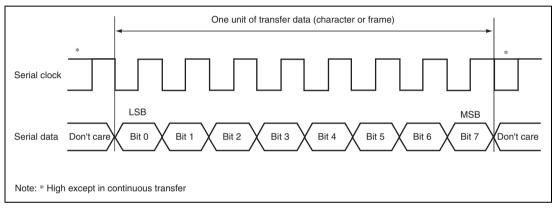

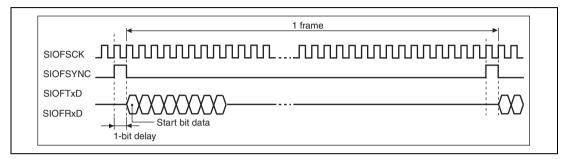

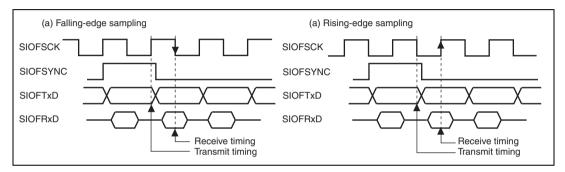

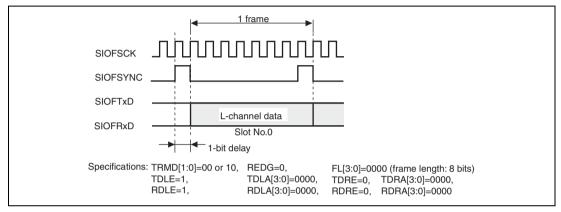

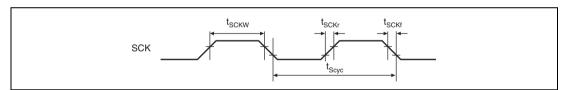

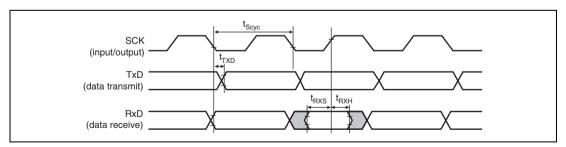

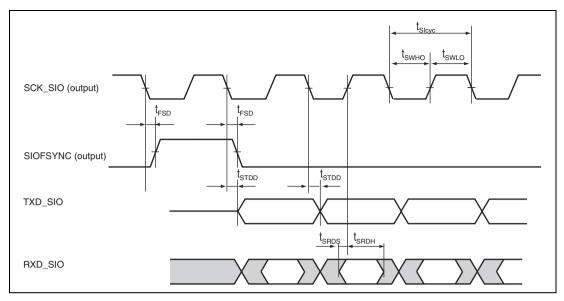

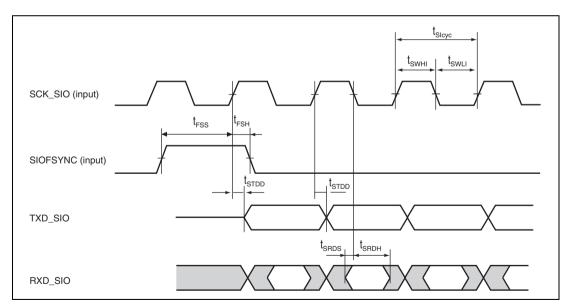

|       | 21.4.2      | Serial Timing                                                    | 1018 |

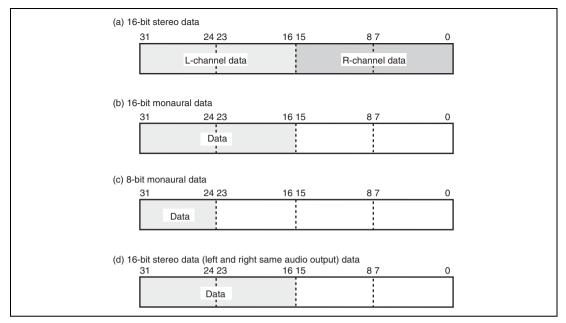

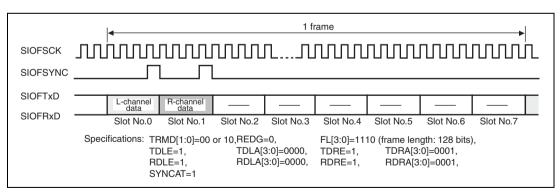

|       | 21.4.3    | Transfer Data Format                                               | 1019 |

|-------|-----------|--------------------------------------------------------------------|------|

|       | 21.4.4    | Register Allocation of Transfer Data                               | 1020 |

|       | 21.4.5    | FIFO                                                               | 1022 |

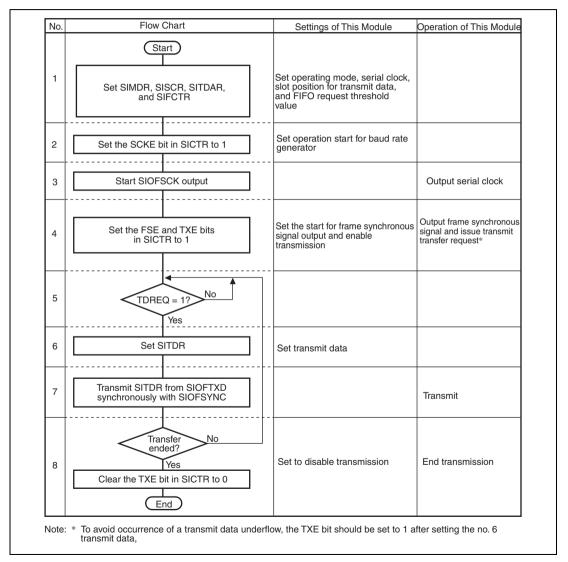

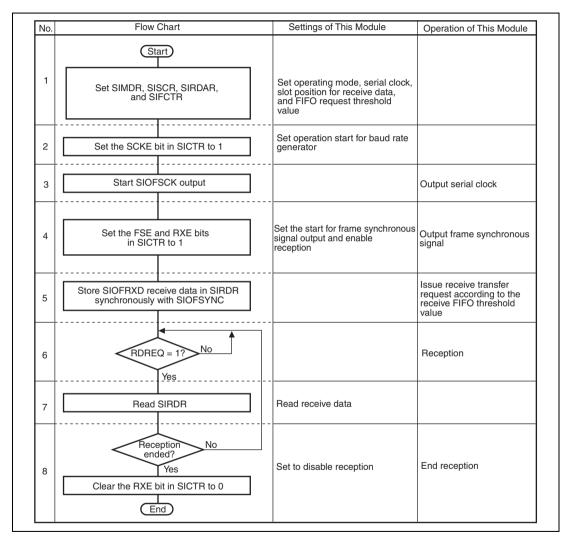

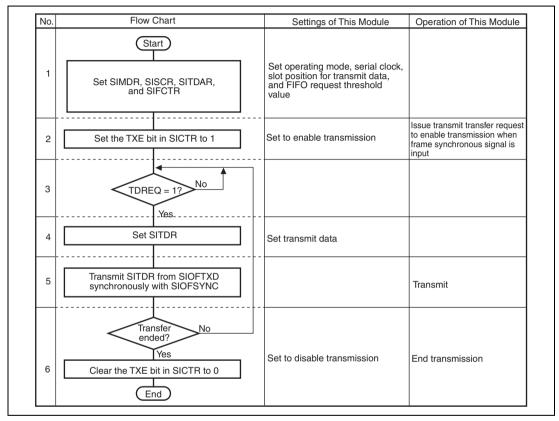

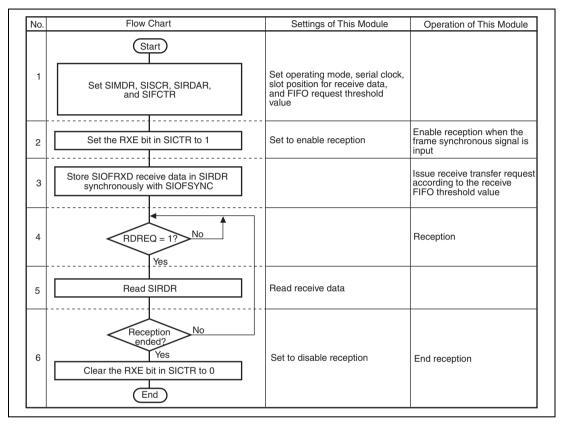

|       | 21.4.6    | Transmit and Receive Procedures                                    | 1024 |

|       | 21.4.7    | Interrupts                                                         | 1029 |

|       | 21.4.8    | Transmit and Receive Timing                                        | 1031 |

| Secti | ion 22 C  | ontroller Area Network                                             | 1035 |

| 22.1  | Summa     | ry                                                                 | 1035 |

|       | 22.1.1    | Overview                                                           | 1035 |

|       | 22.1.2    | Scope                                                              | 1035 |

|       | 22.1.3    | Audience                                                           | 1035 |

|       | 22.1.4    | References                                                         | 1036 |

|       | 22.1.5    | Features                                                           | 1036 |

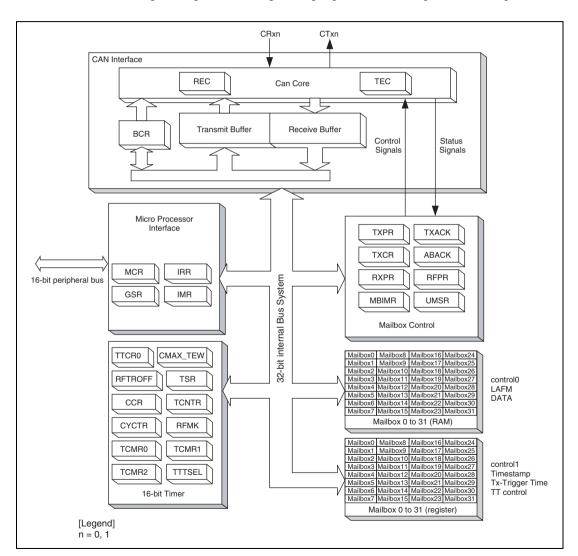

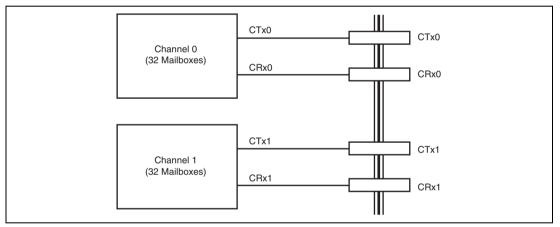

| 22.2  | Archite   | cture                                                              | 1037 |

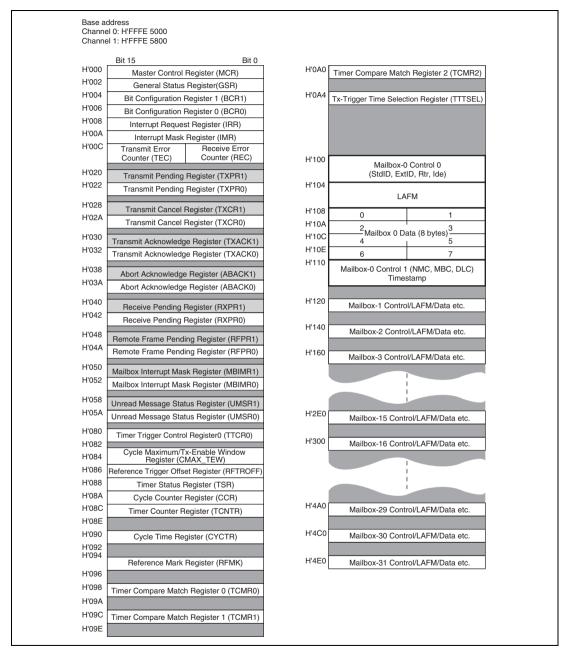

| 22.3  | Progran   | nming Model - Overview                                             | 1040 |

|       | 22.3.1    | Memory Map                                                         | 1040 |

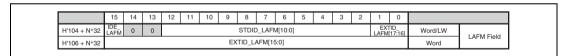

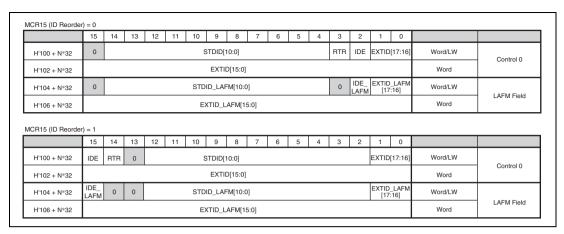

|       | 22.3.2    | Mailbox Structure                                                  | 1042 |

|       | 22.3.3    | Control Registers                                                  | 1058 |

|       | 22.3.4    | Mailbox Registers                                                  | 1079 |

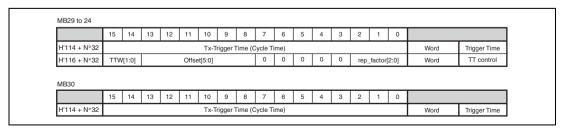

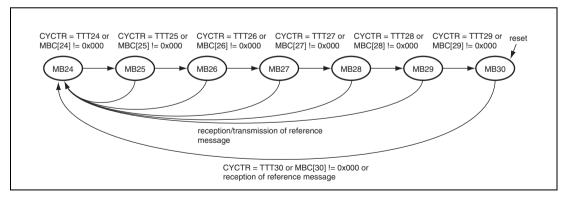

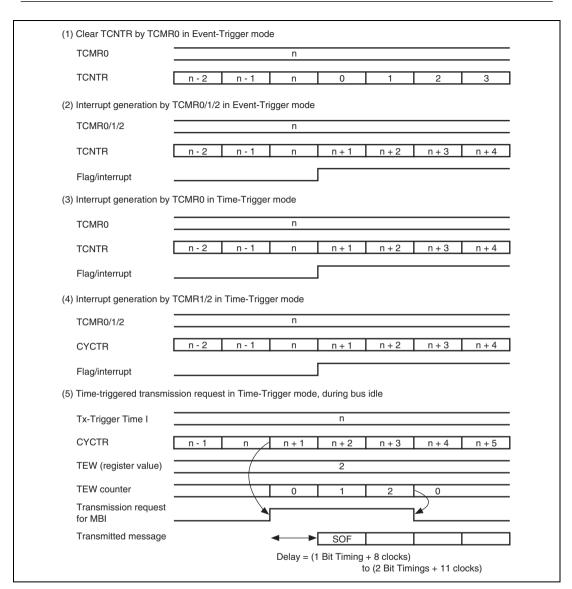

|       | 22.3.5    | Timer Registers                                                    | 1093 |

| 22.4  | Applica   | tion Note                                                          | 1106 |

|       | 22.4.1    | Test Mode Settings                                                 | 1106 |

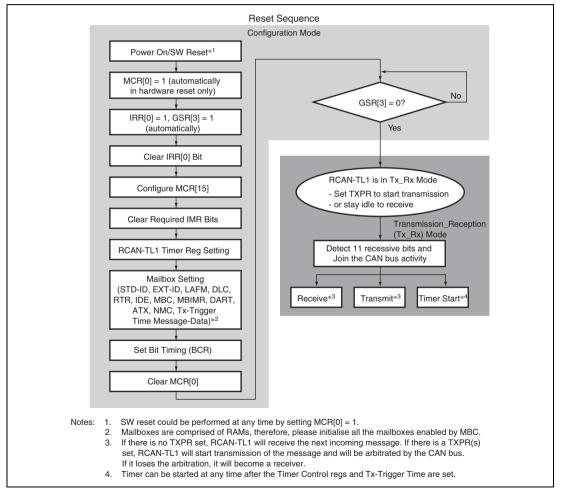

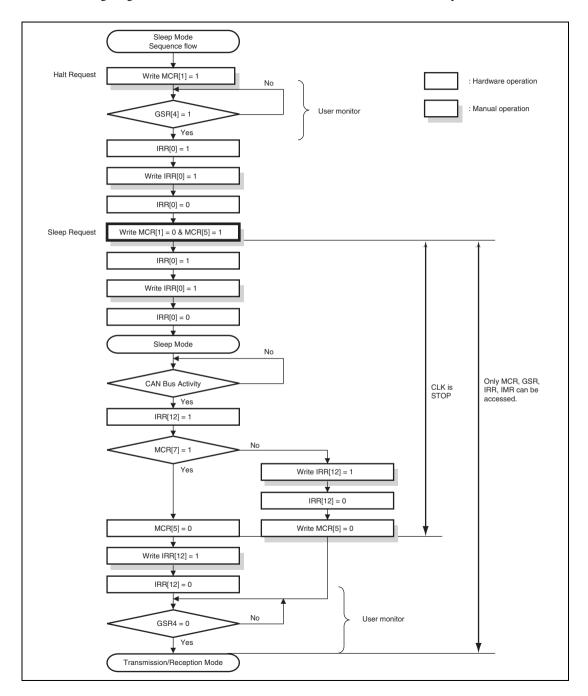

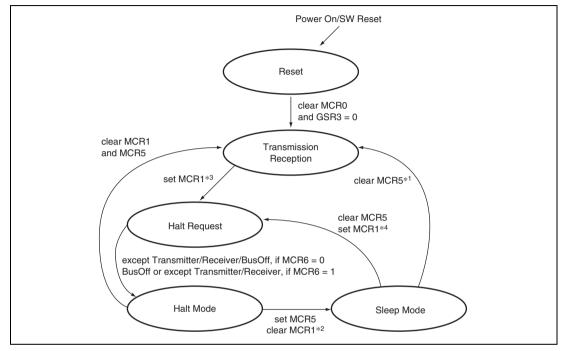

|       | 22.4.2    | Configuration of This Module                                       | 1108 |

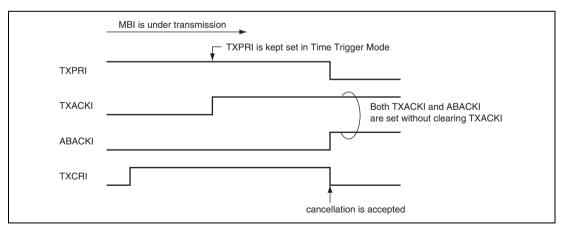

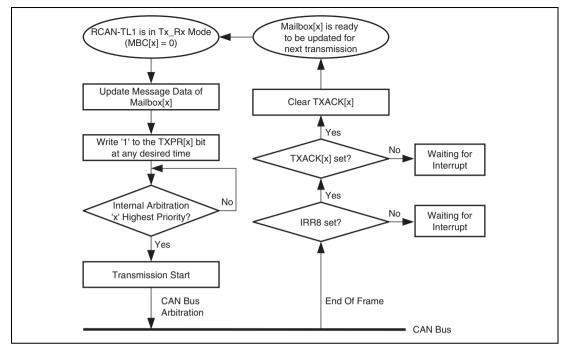

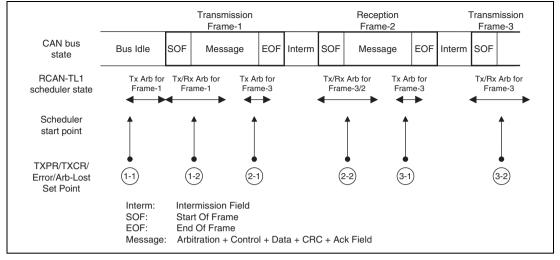

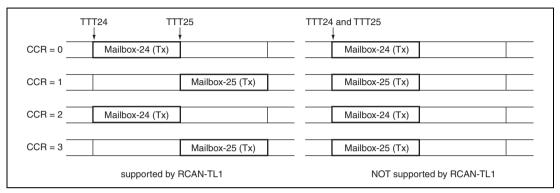

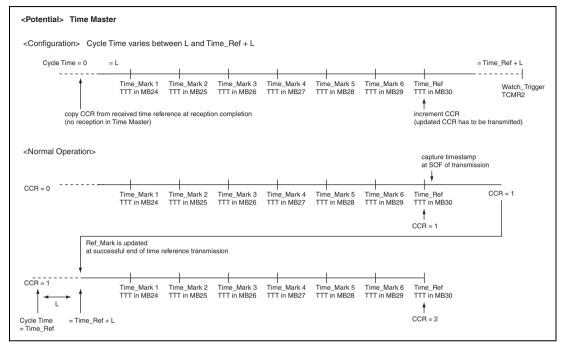

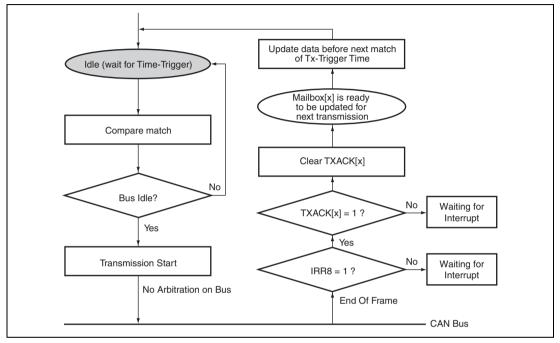

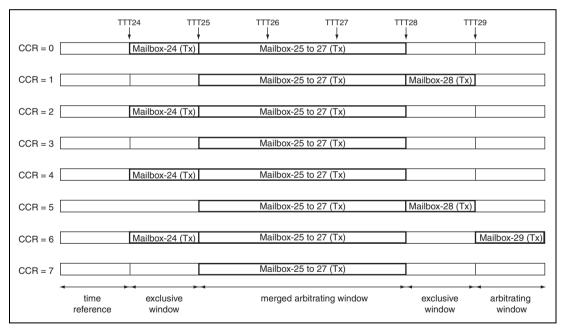

|       | 22.4.3    | Message Transmission Sequence                                      | 1112 |

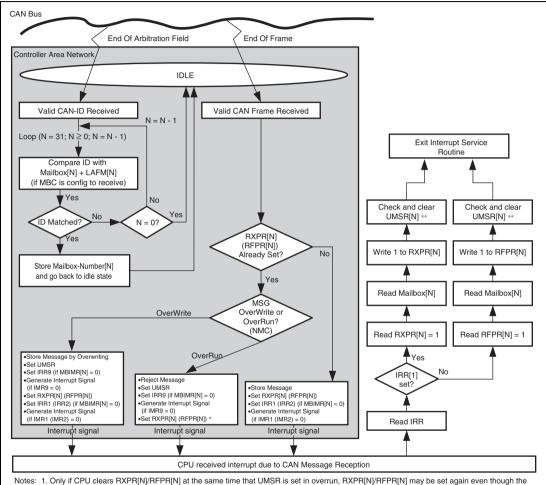

|       | 22.4.4    | Message Receive Sequence                                           |      |

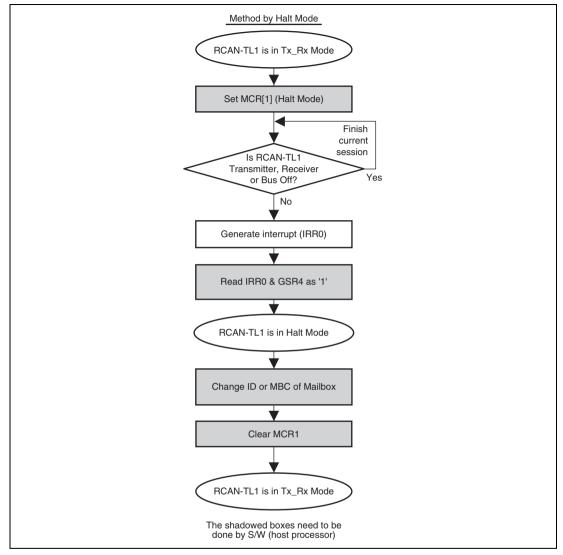

|       | 22.4.5    | Reconfiguration of Mailbox                                         | 1129 |

| 22.5  | Interrup  | t Sources                                                          | 1131 |

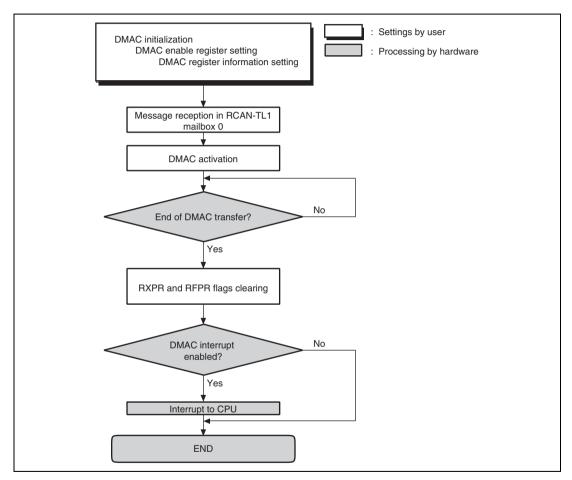

| 22.6  | DMAC      | Interface                                                          | 1132 |

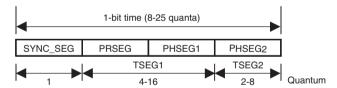

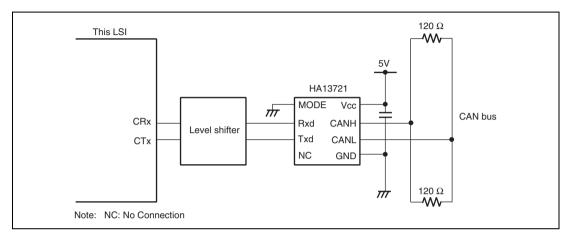

| 22.7  | CAN B     | us Interface                                                       | 1133 |

| 22.8  | Setting   | I/O Ports                                                          | 1134 |

| 22.9  | Usage N   | Notes                                                              | 1136 |

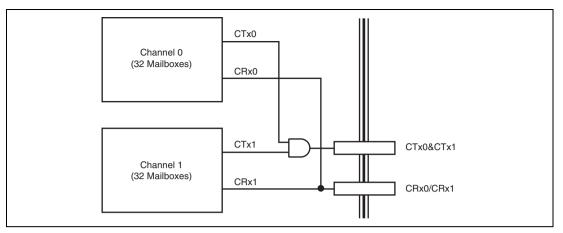

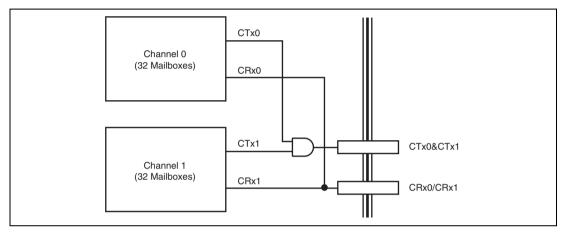

|       | 22.9.1    | Notes on Port Setting for Multiple Channels Used as Single Channel | 1136 |

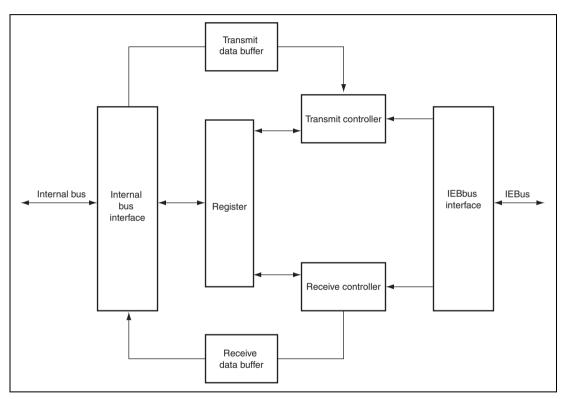

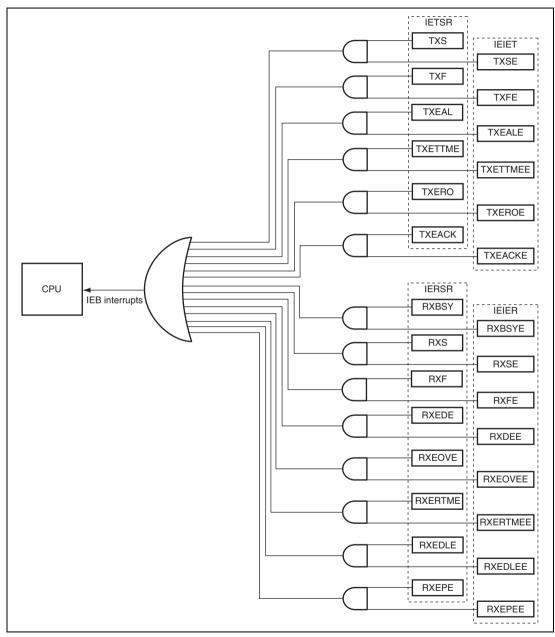

| Secti | ion 23 II | EBus <sup>™</sup> Controller                                       | 1137 |

| 23.1  | Features  | S                                                                  | 1137 |

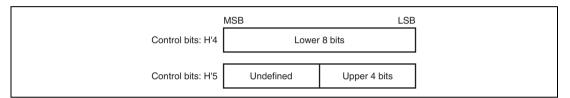

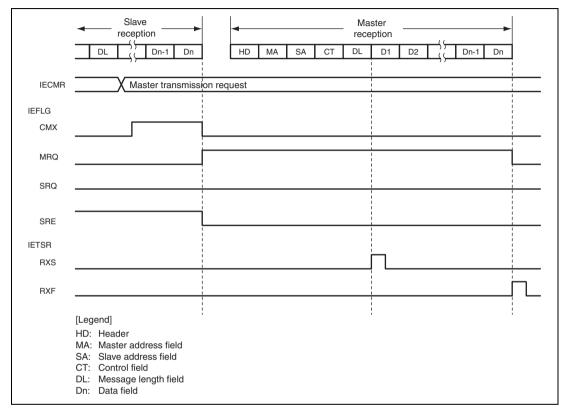

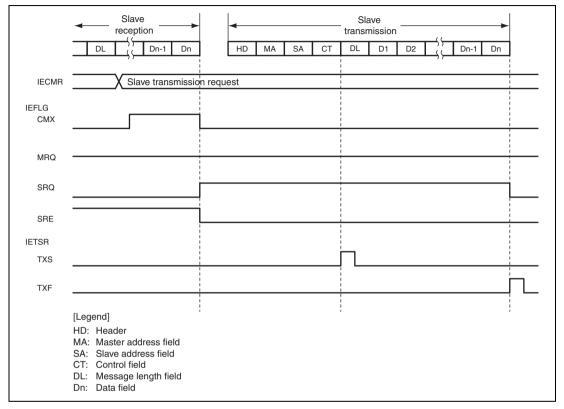

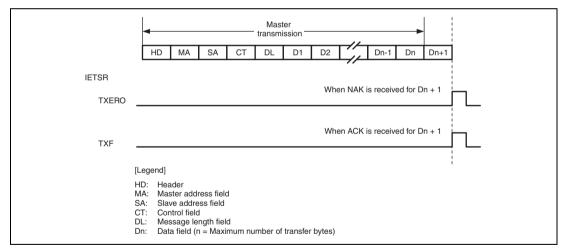

|       | 23.1.1    | IEBus Communications Protocol                                      | 1138 |

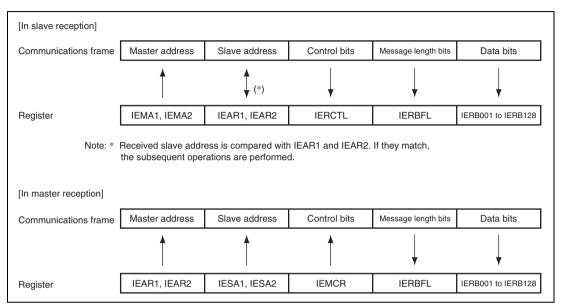

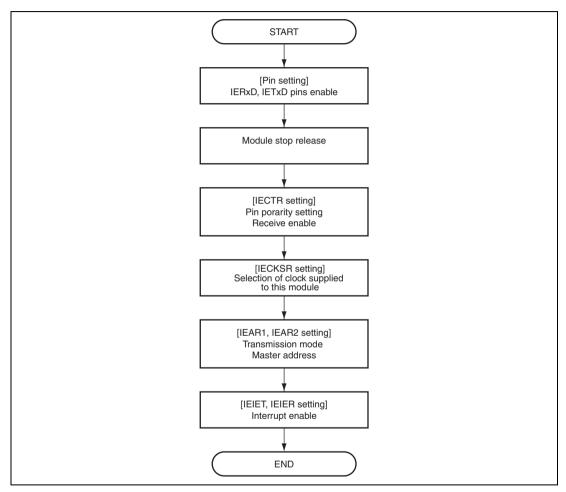

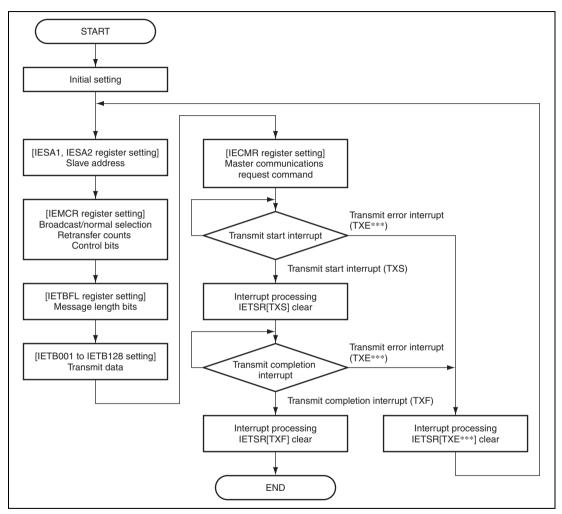

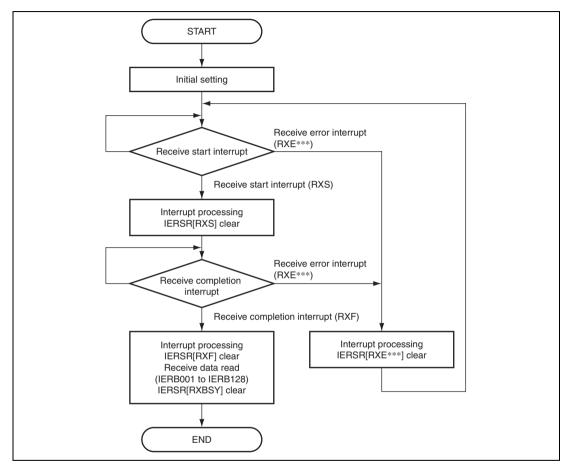

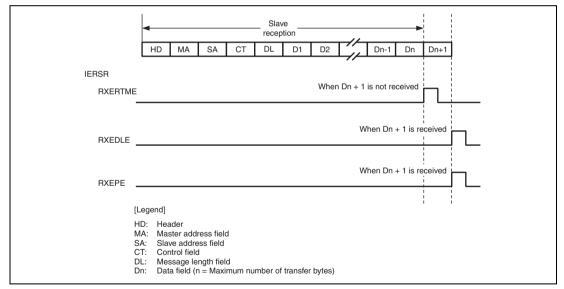

|       | 23.1.2    | Communications Protocol                                            | 1142 |

|       | 23.1.3    | Transfer Data (Data Field Contents)                                | 1150 |

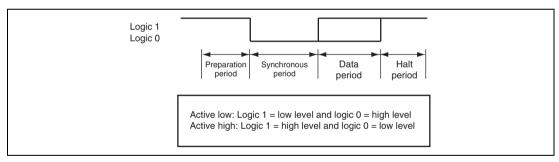

|       | 23.1.4    | Bit Format                                                         | 1153 |

|      | 23.1.5    | Configuration                                              | 1154 |

|------|-----------|------------------------------------------------------------|------|

| 23.2 | Input/Ou  | atput Pins                                                 | 1155 |