# **MPQ4473-AEC1**

High-Efficiency, Fast-Transient, 3.5A, 36V Synchronous, Step-Down Converter with AEC-Q100 Qualified

The Future of Analog IC Technology

## DESCRIPTION

The MPQ4473 is a fully integrated, highfrequency, synchronous, rectified, step-down, switch-mode converter. It offers a compact solution to achieve a 3.5A, continuous-output current over a wide input-supply range with excellent load and line regulation. It provides fast, transient response and good stability for wide input-supply and load range. The MPQ4473 operates at high efficiency over a wide-output-current load range.

MPQ4473 has full protection features including, short-circuit protection (SCP), over-current protection (OCP), under-voltage protection (UVP), and thermal shutdown (TSD).

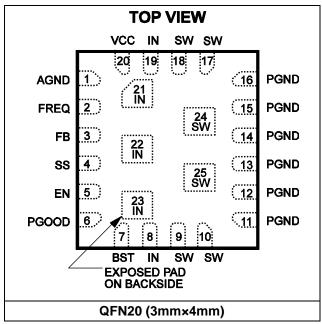

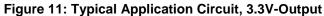

The MPQ4473 requires minimal, readily available, standard, external components, and is available in a compact 3mmx4mm, 20-pin, QFN package.

## FEATURES

- Wide 4.5V-to-36V Operating Input Range

- Guaranteed 3.5A, Continuous Output Current

- Internal 40m $\Omega$  High-Side, 20m $\Omega$  Low-Side Power MOSFETs

- Proprietary Switching-Loss-Reduction Technology

- 1% Reference Voltage

- Programmable Soft-Start Time

- Low Drop-Out Mode

- 200kHz-to-1MHz Switching Frequency

- SCP, OCP, UVP, and Thermal Shutdown

- Output Adjustable from 0.8V to 0.9×V<sub>IN</sub>

- Available in a 3mmx4mm, 20-pin, QFN Package

- Available in AEC-Q100 Grade 1

## APPLICATIONS

- Notebook Systems and I/O Power

- Automotive Systems

- Networking Systems

- Industrial Supplies

- Optical Communications Systems

- Distributed Power and POL Systems

All MPS parts are lead-free, halogen free, and adhere to the RoHS directive. For MPS green status, please visit MPS website under Quality Assurance. "MPS" and "The Future of Analog IC Technology" are Registered Trademarks of Monolithic Power Systems, Inc.

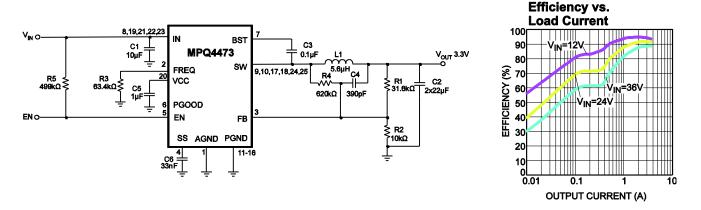

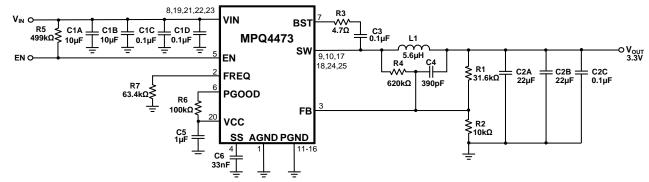

## TYPICAL APPLICATION

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2016 MPS. All Rights Reserved.

# Part Number\*PackageTop MarkingMPQ4473GLQFN-20 (3mmx4mm)See Below

#### **ORDERING INFORMATION**

\* For Tape & Reel, add suffix -Z (e.g. MPQ4473GL-Z);

## **TOP MARKING**

MPYW 4473 LLL

MP: MPS prefix: Y: year code; W: week code: 4473: first four digits of the part number; LLL: lot number;

### **PACKAGE REFERENCE**

## ABSOLUTE MAXIMUM RATINGS (1)

| Supply Voltage V <sub>IN</sub> 40V                        |

|-----------------------------------------------------------|

| $V_{SW}$ 0.3V to $V_{IN}$ + 0.3V                          |

| V <sub>BST</sub> V <sub>SW</sub> + 6V                     |

| $V_{PGOOD}$ 0.3V to $V_{CC}$ +0.6V                        |

| All Other Pins                                            |

| Continuous Power Dissipation $(T_A = +25^{\circ}C)^{(2)}$ |

| 2.6W                                                      |

| Operating Junction Temperature                            |

| Lead Temperature                                          |

| Storage Temperature65°C to +150°C                         |

| (3)                                                       |

#### Recommended Operating Conditions<sup>(3)</sup>

| Supply Voltage V <sub>IN</sub> | 4.5V to 36V                    |

|--------------------------------|--------------------------------|

| Output Voltage Vout            | 0.8V to 0.9×V <sub>IN</sub>    |

| Operating Junction Temp. (     | T <sub>J</sub> )40°C to +125°C |

## Thermal Resistance (4) $\theta_{JA}$ $\theta_{JC}$

QFN-20 (3mm×4mm) ......48 ......10 ...°C/W

#### Notes:

- Absolute maximum ratings are rated under room temperature unless otherwise noted. Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature  $T_J(MAX)$ , the junction-toambient thermal resistance  $\theta_{JA}$ , and the ambient temperature  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D(MAX)=(T_J(MAX)-T_A)/\theta_{JA}$ . Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- 3) The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB.

## **ELECTRICAL CHARACTERISTICS**

$V_{IN} = 24V$ ,  $V_{EN} = 2V$ ,  $T_J = -40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted. Typical values are at  $T_J = 25^{\circ}C$ .

| Parameters                                                    | Symbol                                | Condition                                            | Min  | Тур  | Max  | Units           |

|---------------------------------------------------------------|---------------------------------------|------------------------------------------------------|------|------|------|-----------------|

| Supply Current (Shutdown)                                     | I <sub>IN</sub>                       | $V_{EN} = 0V$                                        |      | 10   | 300  | nA              |

| Supply Current (Quiescent)                                    | I <sub>IN</sub>                       | V <sub>FB</sub> = 0.95V                              |      | 500  | 600  | μA              |

| HS Switch On Resistance                                       | HS <sub>RDS-ON</sub>                  |                                                      |      | 40   | 65   | mΩ              |

| LS Switch On Resistance <sup>(5)</sup>                        | LS <sub>RDS-ON</sub>                  |                                                      |      | 20   |      | mΩ              |

| Switch Leakage                                                | SW <sub>LKG</sub>                     | $V_{EN} = 0V$<br>$V_{SW} = 0V$ or 36V                |      | 10   | 400  | nA              |

| Current Limit                                                 | I <sub>LIMIT</sub>                    |                                                      | 4.2  | 6.6  | 9    | Α               |

| One-Shot On Time                                              | t <sub>ON</sub>                       | $V_{IN}$ =12V, $R_{FREQ}$ =30k $\Omega$              | 230  | 280  | 330  | ns              |

| Minimum Off Time <sup>(5)</sup>                               | t <sub>OFF</sub>                      |                                                      |      | 100  |      | ns              |

| Fold-Back Off Time <sup>(5)</sup>                             | t <sub>FB</sub>                       | I <sub>LIM</sub> =1(HIGH),<br>FB>50%V <sub>REF</sub> |      | 4.8  |      | μs              |

| Fold-Back Off Time <sup>(5)</sup>                             | t <sub>FB</sub>                       | I <sub>LIM</sub> =1(HIGH),<br>FB<50%V <sub>REF</sub> |      | 16.8 |      | μs              |

| OCP Hold-Off time <sup>(5)</sup>                              | t <sub>oc</sub>                       | I <sub>LIM</sub> =1(HIGH)                            |      | 100  |      | μs              |

|                                                               | V <sub>FB</sub>                       | T <sub>J</sub> = 25°C                                | 807  | 815  | 823  | mV              |

| Feedback Voltage                                              | V <sub>FB</sub>                       | $T_J = -40^{\circ}C$ to $125^{\circ}C$               | 803  |      | 827  | mV              |

| Feedback Current                                              | I <sub>FB</sub>                       | V <sub>FB</sub> = 815mV                              |      | 10   | 50   | nA              |

| Soft-Start Charging Current                                   | I <sub>SS</sub>                       | V <sub>SS</sub> =0V                                  | 6    | 8.5  | 11   | μA              |

| Power Good Rising Threshold                                   | PGOOD <sub>Vth-Hi</sub>               |                                                      | 0.87 | 0.9  | 0.93 | V <sub>FB</sub> |

| Power Good Falling Threshold                                  | PGOOD <sub>Vth-Lo</sub>               |                                                      | 0.82 | 0.85 | 0.88 | V <sub>FB</sub> |

| Power Good Threshold<br>Hysteresis                            | PGOOD <sub>Vth-Hys</sub>              |                                                      |      | 0.05 |      | V <sub>FB</sub> |

| Power Good Rising Delay                                       | t <sub>PGOOD</sub>                    |                                                      | 500  | 700  | 900  | μs              |

| EN Rising Threshold                                           | EN <sub>Vth-Hi</sub>                  |                                                      | 1.0  | 1.2  | 1.4  | V               |

| EN Falling Threshold                                          | EN <sub>Vth-Lo</sub>                  |                                                      | 0.7  | 0.85 | 0.99 | V               |

| EN Threshold Hysteresis                                       | EN <sub>Vth-Hys</sub>                 |                                                      |      | 390  |      | mV              |

| EN Input Current                                              | I <sub>EN</sub>                       | $V_{EN} = 2V$                                        |      | 1.5  | 2    | μA              |

| V <sub>IN</sub> Under-Voltage Lockout<br>Threshold Rising     | $\text{INUV}_{\text{Vth}_{\text{R}}}$ |                                                      | 3.7  | 4.0  | 4.3  | V               |

| V <sub>IN</sub> Under-Voltage Lockout<br>Threshold Falling    | INUV <sub>Vth_F</sub>                 |                                                      | 2.8  | 3.1  | 3.4  | V               |

| V <sub>IN</sub> Under-Voltage Lockout<br>Threshold Hysteresis | INUV <sub>HYS</sub>                   |                                                      |      | 900  |      | mV              |

| V <sub>CC</sub> Regulator                                     | V <sub>cc</sub>                       | I <sub>CC</sub> =0                                   | 4.5  | 4.85 | 5.2  | V               |

| V <sub>CC</sub> Load Regulation                               |                                       | I <sub>CC</sub> =10mA                                |      | 1    | 2    | %               |

| Thermal Shutdown <sup>(5)</sup>                               | T <sub>SD</sub>                       |                                                      |      | 175  |      | °C              |

| Thermal Shutdown Hysteresis <sup>(5)</sup>                    | T <sub>SD-HYS</sub>                   |                                                      |      | 45   |      | °C              |

Note:

5) Derived from bench characterization, not tested in production.

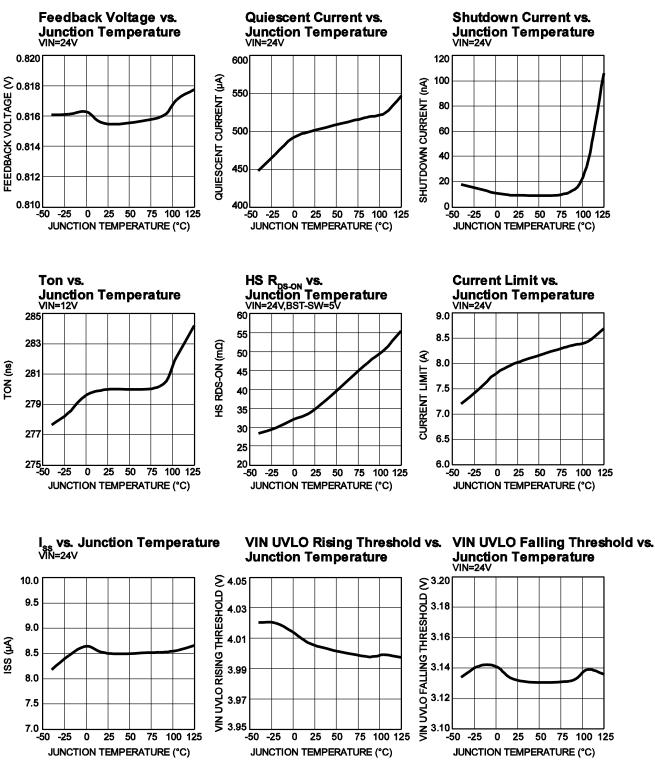

## **TYPICAL CHARACTERISTICS**

## **TYPICAL CHARACTERISTICS**

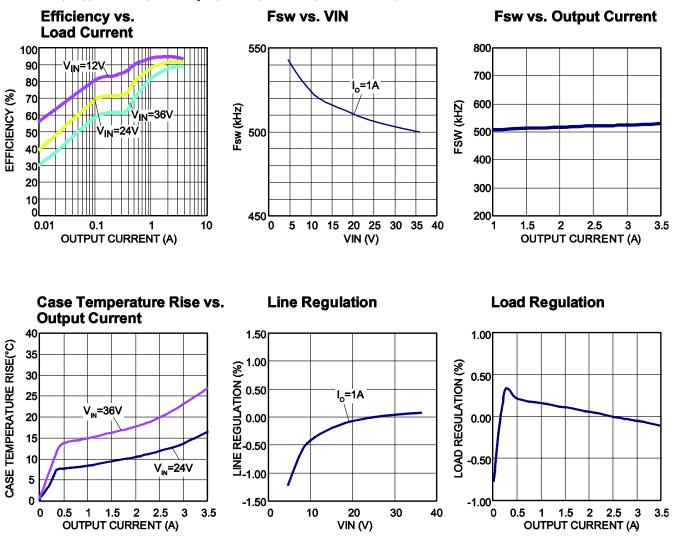

## **TYPICAL PERFORMANCE CHARACTERISTICS**

$V_{IN} = 24V$ ,  $V_{OUT} = 3.3V$ , L = 10µH,  $R_{FREQ} = 63.4k$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.

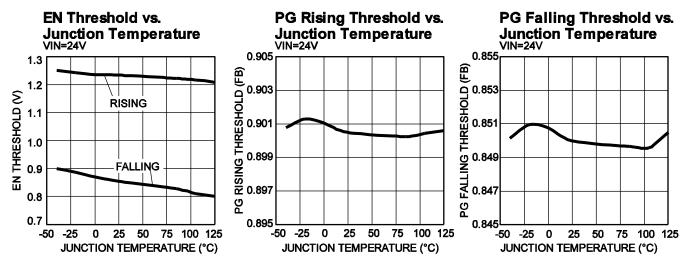

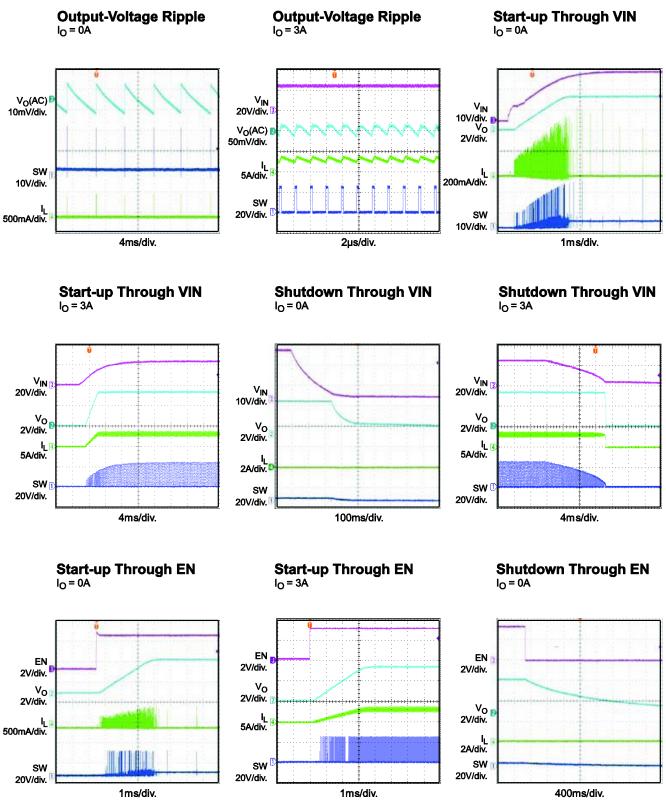

## TYPICAL PERFORMANCE CHARACTERISTICS (CONTINUED)

$V_{IN} = 24V$ ,  $V_{OUT} = 3.3V$ ,  $L = 10\mu$ H,  $R_{FREQ} = 63.4$ k,  $T_A = +25$ °C, unless otherwise noted.

MPQ4473 Rev. 1.01 5/24/2016 M

www.MonolithicPower.com Patent Protected. Unauthorized Photoc

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2016 MPS. All Rights Reserved.

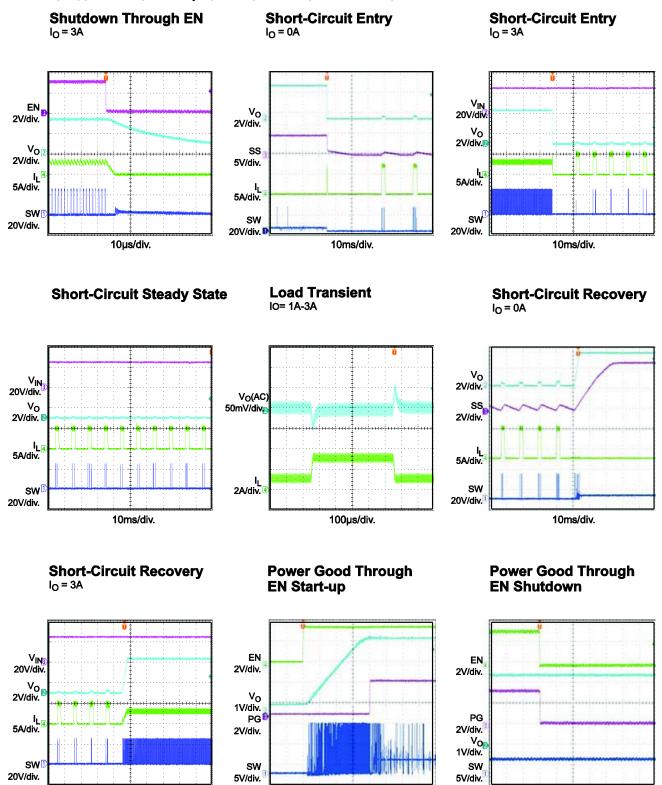

## TYPICAL PERFORMANCE CHARACTERISTICS (CONTINUED)

$V_{IN} = 24V$ ,  $V_{OUT} = 3.3V$ ,  $L = 10\mu$ H,  $R_{FREQ} = 63.4k$ ,  $T_A = +25$ °C, unless otherwise noted.

10ms/div.

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2016 MPS. All Rights Reserved.

1ms/div.

## **PIN FUNCTIONS**

| Pin #                                    | Name  | Description                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------------------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                        | AGND  | Analog Ground.                                                                                                                                                                                                                                                                                                                                                                                       |

| 2                                        | FREQ  | Frequency Set (for CCM). The input voltage and the frequency-set resistor are connected to GND to determine the ON period. Decouple with a 1nF capacitor.                                                                                                                                                                                                                                            |

| 3                                        | FB    | Feedback. The tap of the external resistor divider from the output to GND sets the output voltage.                                                                                                                                                                                                                                                                                                   |

| 4                                        | SS    | Soft-Start. Connect an external capacitor to program the soft-start time for the switch-mode regulator. When the EN pin goes HIGH, an internal-current source (8.5 $\mu$ A) charges the capacitor, and the SS voltage slowly and smoothly ramps up from 0 to V <sub>FB</sub> . When the EN pin goes LOW, the internal-current source discharges the capacitor, and the SS voltage slowly ramps down. |

| 5                                        | EN    | Enable. EN=1 to enable the MPQ4473. For automatic start-up, connect EN pin to IN with a 100k $\Omega$ resistor. It includes an internal 1M $\Omega$ pull-down resistor.                                                                                                                                                                                                                              |

| 6                                        | PGOOD | Power Good Output. The output of this pin is an open drain and goes HIGH if the output voltage exceeds 90% of the nominal voltage. There is delay of ~700 $\mu$ s from FB ≥ 90% to PGOOD HIGH.                                                                                                                                                                                                       |

| 7                                        | BST   | Bootstrap. Requires a $0.1\mu$ F to $1\mu$ F capacitor connected between the SW and BS pins to form a floating supply across the high-side switch driver.                                                                                                                                                                                                                                            |

| 8, 19,<br>Exposed pads<br>21, 22, 23     | IN    | Supply Voltage. The MPQ4473 operates from a 4.5V to 36V input rail. It requires $C_{\rm IN}$ to decouple the input rail. Connect using wide PCB traces and multiple vias.                                                                                                                                                                                                                            |

| 9, 10, 17, 18,<br>Exposed pads<br>24, 25 | SW    | Switch Output. Connect using wide PCB traces and multiple vias.                                                                                                                                                                                                                                                                                                                                      |

| 11-16                                    | PGND  | System Ground. This pin is the reference ground of the regulated output voltage. *Care must be taken in PCB layout.                                                                                                                                                                                                                                                                                  |

| 20                                       | Vcc   | Internal Bias Supply. Decouple with a $1\mu F$ capacitor as close to the pin as possible.                                                                                                                                                                                                                                                                                                            |

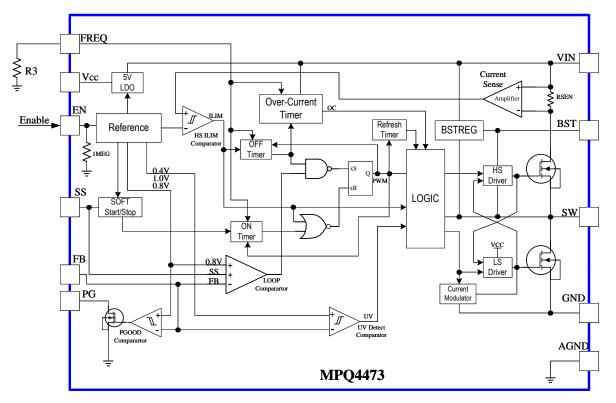

## **BLOCK DIAGRAM**

Figure 1: Functional Block Diagram

## **OPERATION**

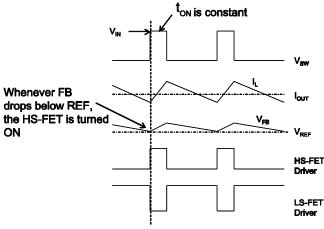

#### **PWM Operation**

The MPQ4473 is a fully integrated, synchronous, rectified, step-down, switch-mode converter. At the beginning of each cycle, the high-side MOSFET (HS-FET) turns ON when the feedback voltage ( $V_{FB}$ ) drops below the reference voltage ( $V_{REF}$ ). This indicates an insufficient output voltage. The ON period is determined by the input voltage and the frequency-set resistor, which can be calculated as follows:

$$t_{\rm ON}(ns) = \frac{96 \times R_{\rm FREQ}(k\Omega)}{V_{\rm IN}} + t_{\rm DELAY}(ns)$$

(1)

After the ON period elapses, the HS-FET turns OFF. It turns ON again when  $V_{FB}$  drops below  $V_{REF}$ . By repeating this operation, the converter regulates the output voltage. To minimize conduction loss, the integrated, low-side MOSFET (LS-FET) turns ON when the HS-FET is OFF. A dead short occurs between the input and GND if both the HS-FET and the LS-FET turn on simultaneously (shoot through). An internal dead-time (DT), generated between HS-FET OFF and LS-FET ON or LS-FET OFF and HS-FET ON, prevents shoot through.

#### **Heavy-Load Operation**

Figure 2: Heavy-Load Operation

In continuous-conduction mode (CCM), when the output current is HIGH, the HS-FET and LS-FET repeatedly turn ON/OFF (see MPS. All Rights Reserved. The inductor current never reaches zero. In CCM, the switching frequency ( $f_{SW}$ ) is fairly constant.

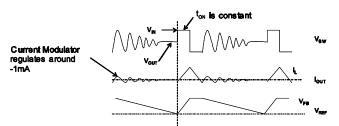

#### Light-Load Operation

At light-load or no-load conditions, the output drops very slowly; the MPQ4473 reduces the switching frequency automatically to maintain high efficiency. Figure 3 shows light-load operation.  $V_{FB}$  does not reach  $V_{REF}$  as the inductor current approaches zero. The LS-FET driver enters a tri-state (high Z) whenever the inductor current reaches zero. A current modulator takes control of the LS-FET and limits the inductor current to less than -1mA. This causes the output capacitors to discharge slowly to GND through the LS-FET to improve light-load efficiency. At light loads, the HS-FET does not turn ON as frequently as with heavy loads. This is called skip mode.

As the output current increases from the lightload conditions, the current modulator's regulatory time period becomes shorter. The HS-FET turns ON more frequently, thus increasing the switching frequency. The output current reaches a critical level when the current modulator time is zero. The critical output-current level can be calculated as follows:

$$I_{OUT} = \frac{(V_{IN} - V_{OUT}) \times V_{OUT}}{2 \times L \times F_{SW} \times V_{IN}}$$

(2)

It enters PWM mode once the output current exceeds the critical level; then the switching frequency stays fairly constant over the outputcurrent range.

#### **Switching Frequency**

The input voltage is feed-forwarded to the ontime one-shot timer through the resistor ( $R_{FREQ}$ ). The duty ratio remains at  $V_{OUT}/V_{IN}$ , allowing the switching frequency to remain fairly constant over the input-voltage range. The switching frequency can be calculated as follows: mps

$$F_{SW}(kHz) = \frac{10^{6}}{\left[\frac{96 \times R_{FREQ}(k\Omega)}{V_{IN}} + t_{DELAY}(ns)\right] \times \frac{V_{IN}}{V_{OUT}}}$$

(3)

where,

t<sub>DELAY</sub>\_The comparator delay (~20ns).

The MPQ4473 is optimized for 200kHz-to-1MHz applications; this enables applications to operate at high-switching frequencies with high efficiency. The high-switching frequency allows for smaller LC-filter components that reduce PCB space requirements.

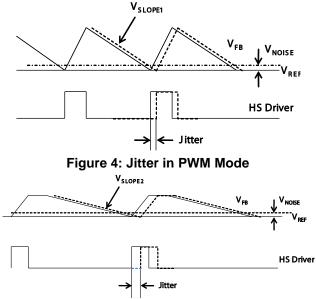

#### **Ramp Compensation**

Figure 4 and Figure 5 show jitter occurring in both PWM mode and skip mode. Noise on  $V_{FB}$ 's downward slope causes the HS-FET ON time to deviate from its intended position and produce jitter. The relationship between system stability and the height of the  $V_{FB}$  ripple is significant: the steep slope of the  $V_{FB}$  ripple dominates noise immunity. The magnitude of the  $V_{FB}$  ripple doesn't affect the noise immunity directly.

Figure 5: Jitter in Skip Mode

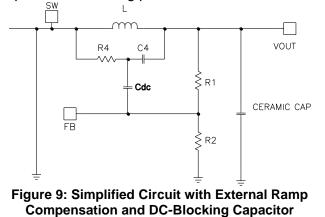

Ceramic output capacitors lack enough ESR ripple to stabilize the system, and require an external compensation ramp.

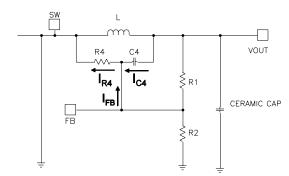

#### Figure 6: Simplified Circuit in PWM Mode with External Ramp Compensation

In PWM mode, MPQ4473 has an equivalent circuit with HS-FET OFF and uses an external ramp compensation circuit ( $R_4$ ,  $C_4$ ), shown as a simplified circuit in Figure 6. Derive the external ramp from the inductor-ripple current. Choose  $C_4$ ,  $R_1$ , and  $R_2$  to meet the following condition:

$$\frac{1}{2\pi \times F_{SW} \times C_4} < \frac{1}{5} \times \left(\frac{R_1 \times R_2}{R_1 + R_2}\right)$$

(4)

then:

$$\mathbf{I}_{\mathsf{R4}} = \mathbf{I}_{\mathsf{C4}} + \mathbf{I}_{\mathsf{FB}} \approx \mathbf{I}_{\mathsf{C4}} \tag{5}$$

The  $V_{\text{FB}}$  downward slope ripple is then calculated as follows:

$$V_{SLOPE1} = \frac{-V_{OUT}}{R_{a} \times C_{a}}$$

(6)

Using equation 6, reduce  $R_4$  or  $C_4$  to decrease instability in PWM mode. If C4 cannot be reduced further (due to the limitations of equation 4), then only reduce  $R_4$ . Based on bench experiments,  $V_{SLOPE1}$  is around 20V/ms-40V/ms.

When using POSCAP or types of capacitors with higher ESR, an external ramp is not necessary.

External Ramp Compensation

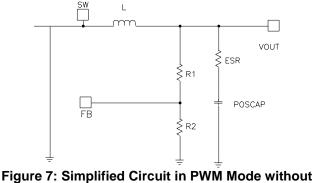

Figure 7 shows an equivalent circuit in PWM mode with the HS-FET OFF and without an external ramp circuit. The ESR ripple dominates the output ripple. The  $V_{FB}$  downward slope is calculated as follows:

$$V_{\text{SLOPE1}} = \frac{-\text{ESR} \times V_{\text{REF}}}{L}$$

(7)

From equation 7, the  $V_{FB}$  downward slope is proportional to ESR/L. Therefore, it's necessary to know the minimum ESR value of the output capacitors without an external ramp. Also, there is an inductance limit: a smaller inductance leads to increased stability. Based on bench experiments, keep  $V_{SLOPE1}$  around 15V/ms to 30V/ms.

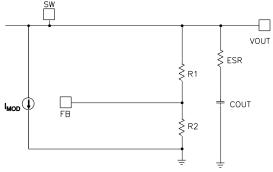

In skip mode, the external ramp does not affect the downward slope; the downward slope of the  $V_{FB}$  ripple remains the same with or without the external ramp. Figure 8 shows an equivalent circuit with the HS-FET OFF and the current modulator regulating the LS-FET.

Figure 8: Simplified Circuit in Skip Mode

The downward slope of the V<sub>FB</sub> ripple is:

$$V_{SLOPE2} = \frac{-V_{REF}}{(R_1 + R_2) \times C_{OUT}}$$

(8)

To keep the system stable during light loads, avoid large V<sub>FB</sub> resistors. Also, keep the V<sub>SLOPE2</sub> value around 0.4V/ms to 0.8mV/ms. Note that I<sub>MOD</sub> is excluded from the equation because it does not impact the system's light-load stability.

#### Soft-Start (SS)

The MPQ4473 employs soft-start (SS) to ensure smooth output during power-up. When the EN pin goes HIGH, an internal-current source (8.5 $\mu$ A) charges the SS capacitor (C<sub>SS</sub>). The C<sub>SS</sub> voltage takes over the REF voltage to the PWM

comparator. The output voltage smoothly ramps up with V<sub>SS</sub>. Once V<sub>SS</sub> reaches the same level as V<sub>REF</sub>, it continues ramping up while V<sub>REF</sub> takes over the PWM comparator. At this point, soft-start finishes and the MPQ4473 enters steady state.

$C_{\text{SS}}$  is then:

$$C_{ss}(nF) = \frac{t_{ss}(ms) \times I_{ss}(\mu A)}{V_{REF}(V)}$$

(9)

If the output capacitors have large capacitance values, avoid setting a short SS or risk hitting the current limit during SS. Select a minimum value of 4.7nF if the output capacitance value exceeds  $330\mu F$ .

#### Power Good (PGOOD)

The MPQ4473 has power-good (PGOOD) output. The PGOOD pin is the open drain of a MOSFET. It connects to  $V_{CC}$  (or a different voltage source) through a resistor (e.g.  $100k\Omega$ ). In the presence of an input voltage, the MOSFET turns ON so that the PGOOD pin is pulled to GND before SS is ready. After  $V_{FB}$  reaches  $90\% xV_{REF}$ , the PGOOD pin is pulled HIGH (after a delay, typically 700µs).

When the FB voltage drops to  $85\% xV_{REF}$ , the PGOOD pin is pulled LOW.

#### Over-Current Protection (OCP) and Short-Circuit Protection (SCP)

The MPQ4473 has cycle-by-cycle over-current limit control. The inductor current is monitored during the ON state. Once the inductor current exceeds the current limit, the HS-FET turns OFF. Simultaneously, the OCP timer starts. The OCP timer is set at 100µs. Hitting the current limit every cycle during the 100µs time frame will trigger hiccup SCP.

If a short circuit occurs, the MPQ4473 immediately will hit its current limit and  $V_{FB}$  will drop below 50%xV<sub>REF</sub> (0.815V). The device considers this an output dead short and will trigger hiccup SCP immediately.

#### **Under-Voltage Protection (UVP)**

The MPQ4473 monitors the output voltage through the tap of a resistor divider to the FB pin. This detects output under-voltage conditions.

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2016 MPS. All Rights Reserved. A  $V_{FB}$  drop below 50%x $V_{REF}$  triggers UVP. Also, it triggers a current limit that initiates SCP.

#### **Under-Voltage Lock-Out Protection (UVLO)**

The MPQ4473 has under-voltage lock-out protection (UVLO). When the input voltage is higher than the UVLO rising threshold voltage, the MPQ4473 begins to power up. It shuts off when the input voltage is lower than the UVLO falling threshold voltage. This is non-latch protection.

#### **Floating Driver and Bootstrap Charging**

An external bootstrap capacitor powers the floating-power MOSFET driver. A dedicated, internal regulator charges and regulates the bootstrap capacitor voltage to ~5V. When the voltage between the BST and SW nodes drops below regulation, a PMOS pass transistor, connected from VIN to BST, turns on. The charging current path travels from VIN to BST and then to SW. The external circuit should provide enough voltage headroom to facilitate charging.

The bootstrap capacitor remains charged if the  $V_{IN}$  is significantly higher than the SW. When the HS-FET is ON,  $V_{IN} \approx V_S$ . This prevents the bootstrap capacitor from charging.

When the LS-FET is ON,  $V_{IN}-V_{SW}$  reaches its maximum for fast charging. When there is no inductor current,  $V_{SW}=V_{OUT}$ ; the difference between  $V_{IN}$  and  $V_{OUT}$  can charge the bootstrap capacitor.

At higher duty cycles, the bootstrap-charging time is shorter. Therefore, the bootstrap capacitor may not charge sufficiently. If the internal circuit does not have sufficient time and voltage to charge the bootstrap capacitor, the bootstrap capacitor voltage drops low. When V<sub>BST</sub>-V<sub>SW</sub> drops below 2.3V, the HS-FET turns OFF. A UVLO circuit allows the LS-FET to conduct and refresh the charge on the bootstrap capacitor. Once the bootstrap capacitor voltage is charged, the HS-FET turns ON again and the part normal switching. The bootstrap resumes refreshing function allows the MPQ4473 to work on low drop-out mode.

#### Thermal Shutdown (TSD)

The MPQ4473 uses thermal shutdown (TSD). The junction temperature of the IC is internally monitored. If the junction temperature exceeds the threshold value (typically 175°C), the converter shuts off. This is a non-latched protection, with about 45°C hysteresis. Once the junction temperature drops to 130°C, it initiates a SS.

## **APPLICATION INFORMATION**

#### Setting the Output Voltage

To set V<sub>OUT</sub>, connect a resistor divider from the output voltage to the FB pin.

Without an external ramp, the feedback resistors  $(R_1 \text{ and } R_2)$  set the output voltage. To determine the values for the resistors, first choose  $R_2$ (typically  $5k\Omega$ -40k $\Omega$ ). Then R<sub>1</sub> is calculated as follows:

$$R1 = \frac{V_{OUT} - V_{REF}}{V_{REF}} \times R2$$

(10)

When using a low-ESR ceramic capacitor on the output, add an external voltage ramp to the FB pin through  $R_4$  and  $C_4$ . The ramp voltage ( $V_{RAMP}$ ) affects output voltage. Calculate V<sub>RAMP</sub> using equation 19. Choose  $R_2$  between  $5k\Omega$  and  $40k\Omega$ . Determine R<sub>1</sub> as follows :

$$\mathbf{R}_{1} = \left(\frac{\mathbf{V}_{\mathsf{REF}} + \frac{1}{2}\mathbf{V}_{\mathsf{RAMP}}}{\mathbf{R}_{2} \times (\mathbf{V}_{\mathsf{OUT}} - \mathbf{V}_{\mathsf{REF}} - \frac{1}{2}\mathbf{V}_{\mathsf{RAMP}})} - \frac{1}{\mathbf{R}_{4}}\right)^{-1} (11)$$

Using equation 11 to calculate the output voltage is complicated. As V<sub>RAMP</sub> changes (due to changes in  $V_{OUT}$  and  $V_{IN}$ ),  $V_{FB}$  also varies. To improve output-voltage accuracy and simplify the R<sub>2</sub> calculation from equation 11, add a DCblocking capacitor ( $C_{DC}$ ). Figure 9 shows a simplified circuit with external ramp compensation and a DC-blocking capacitor. (Equation 10 can then estimate  $R_{1}$ )

Select a  $C_{DC}$  value between 1µF and 4.7µF to improve DC-blocking performance.

#### **Input Capacitor**

The input current to the step-down converter is discontinuous, requiring a capacitor to supply the AC current while maintaining the DC-input voltage. Ceramic capacitors are recommended for high performance. Place the input capacitors as close to the IN pin as possible.

The capacitance varies significantly with temperature. Capacitors with X5R and X7R ceramic dielectrics are fairly stable over temperature fluctuations.

The capacitors must have a ripple-current rating greater than the converter's maximum inputripple current. The input-ripple current can be estimated as follows:

$$I_{CIN} = I_{OUT} \times \sqrt{\frac{V_{OUT}}{V_{IN}} \times (1 - \frac{V_{OUT}}{V_{IN}})}$$

(12)

The worst condition occurs at  $V_{IN} = 2V_{OUT}$ :

where,

$$I_{CIN} = \frac{I_{OUT}}{2}$$

(13)

To simplify calculations, choose an input capacitor whose RMS-current rating is greater than half of the maximum load current. The inputcapacitance value determines the input-voltage ripple of the converter. If there is an inputvoltage-ripple requirement in the system design, choose an input capacitor that meets the specification

The input-voltage ripple can be estimated as follows:

$$\Delta V_{\rm IN} = \frac{I_{\rm OUT}}{F_{\rm SW} \times C_{\rm IN}} \times \frac{V_{\rm OUT}}{V_{\rm IN}} \times (1 - \frac{V_{\rm OUT}}{V_{\rm IN}}) \quad (14)$$

The worst condition occurs at  $V_{IN} = 2V_{OUT}$ :

where,

$$\Delta V_{\rm IN} = \frac{1}{4} \times \frac{I_{\rm OUT}}{F_{\rm SW} \times C_{\rm IN}}$$

(15)

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2016 MPS. All Rights Reserved.

#### **Output Capacitor**

The output capacitor maintains the DC-output voltage. Use ceramic or POSCAP capacitors. The output voltage ripple can be estimated as:

$$\Delta V_{\text{OUT}} = \frac{V_{\text{OUT}}}{F_{\text{SW}} \times L} \times (1 - \frac{V_{\text{OUT}}}{V_{\text{IN}}}) \times (R_{\text{ESR}} + \frac{1}{8 \times F_{\text{SW}} \times C_{\text{OUT}}}) (16)$$

where,

R<sub>ESR</sub>\_The equivalent series resistance of the output capacitor.

For ceramic capacitors, capacitance dominates the impedance at the switching frequency. This is the primary cause of the output-voltage ripple. To simplify calculations, estimate the output-voltage ripple as:

$$\Delta V_{\text{OUT}} = \frac{V_{\text{OUT}}}{8 \times F_{\text{SW}}^{2} \times L \times C_{\text{OUT}}} \times (1 - \frac{V_{\text{OUT}}}{V_{\text{IN}}})$$

(17)

The output-voltage ripple caused by ESR is very small, requiring an external ramp to stabilize the system. The voltage ramp is  $\sim$ 30mV. The external ramp is generated through R<sub>4</sub> and C<sub>4</sub> using the following equation:

$$V_{\text{RAMP}} = \frac{(V_{\text{IN}} - V_{\text{OUT}}) \times T_{\text{ON}}}{R4 \times C4}$$

(18)

Select C<sub>4</sub> to meet the following condition:

$$\frac{1}{2\pi \times F_{sw} \times C4} < \frac{1}{5} \times \left(\frac{R1 \times R2}{R1 + R2}\right)$$

(19)

For POSCAP capacitors, the ESR dominates the impedance at the switching frequency. The ramp voltage generated from the ESR is high enough to stabilize the system. Therefore, an external ramp is not needed. A minimum ESR value of  $12m\Omega$  is required to ensure stable operation of the converter. To simplify calculations, the output ripple can be approximated as:

$$\Delta V_{OUT} = \frac{V_{OUT}}{F_{SW} \times L} \times (1 - \frac{V_{OUT}}{V_{IN}}) \times R_{ESR}$$

(20)

#### Inductor

The inductor is required to supply constant current to the output load while being driven by the switching-input voltage. A larger inductance results in less ripple current and a lower outputripple voltage. However, a larger inductance results in a larger inductor, which is not only physically larger, but has a higher series resistance and/or lower saturation current. A good rule for determining the inductor value is to allow the peak-to-peak ripple current in the inductor to be approximately 30% to 40% of the maximum switch-current limit. Ensure that the peak-inductor current is below the maximum switch-current limit. The inductance value can be calculated as:

$$L = \frac{V_{OUT}}{F_{SW} \times \Delta I_{L}} \times (1 - \frac{V_{OUT}}{V_{IN}})$$

(21)

where,

$\Delta I_{L}$ —The peak-to-peak inductor ripple current.

Choose an inductor that will not saturate under the maximum inductor peak current. The peakinductor current can be calculated as:

$$I_{LP} = I_{OUT} + \frac{V_{OUT}}{2F_{SW} \times L} \times (1 - \frac{V_{OUT}}{V_{IN}})$$

(22)

#### **Typical Design Parameter Tables**

The following tables include recommended component values for typical output voltages (3.3V, 5V) and switching frequencies (300kHz, 500kHz, and 700kHz). Refer to tables 1-3 for cases without external design ramp compensation. Refer to tables 4-6 for design cases with external ramp compensation. An external ramp is not needed when using high-ESR capacitors, such as electrolytic or POSCAPs. An external ramp is needed when using low-ESR capacitors, such as ceramic capacitors. To calculate approximate component values for cases not listed, an Excel spreadsheet available through vour local sales is representative.

#### Table 1: 300kHz, 24V<sub>IN</sub>

| V <sub>out</sub><br>(V) | L<br>(µH) | R1<br>(kΩ) | R2<br>(kΩ) | R <sub>FREQ</sub><br>(kΩ) |

|-------------------------|-----------|------------|------------|---------------------------|

| 3.3                     | 10        | 30.1       | 10         | 110                       |

| 5                       | 10        | 51.1       | 10         | 169                       |

#### Table 2: 500kHz, 24V<sub>IN</sub>

| V <sub>оит</sub><br>(V) | L<br>(µH) | R1<br>(kΩ) | R2<br>(kΩ) | R <sub>FREQ</sub><br>(kΩ) |

|-------------------------|-----------|------------|------------|---------------------------|

| 3.3                     | 10        | 30.1       | 10         | 63.4                      |

| 5                       | 10        | 51.1       | 10         | 100                       |

#### Table 3: 700kHz, 24V<sub>IN</sub>

| V <sub>о∪т</sub><br>(V) | L<br>(µH) | R1<br>(kΩ) | R2<br>(kΩ) | R <sub>FREQ</sub><br>(kΩ) |

|-------------------------|-----------|------------|------------|---------------------------|

| 3.3                     | 10        | 30.1       | 10         | 44.2                      |

| 5                       | 10        | 51.1       | 10         | 69.8                      |

#### Table 4: 300kHz, 24V<sub>IN</sub>

|                         |           | ·          |            |            |            |                           |  |  |

|-------------------------|-----------|------------|------------|------------|------------|---------------------------|--|--|

| V <sub>OUT</sub><br>(V) | L<br>(µH) | R1<br>(kΩ) | R2<br>(kΩ) | R4<br>(kΩ) | C4<br>(pF) | R <sub>FREQ</sub><br>(kΩ) |  |  |

| 3.3                     | 10        | 30.9       | 10         | 953        | 390        | 110                       |  |  |

| 5                       | 10        | 53.6       | 10         | 845        | 560        | 169                       |  |  |

#### Table 5: 500kHz, 24V<sub>IN</sub>

| V <sub>оит</sub><br>(V) | L<br>(µH) | R1<br>(kΩ) | R2<br>(kΩ) | R4<br>(kΩ) | C4<br>(pF) | R <sub>FREQ</sub><br>(kΩ) |

|-------------------------|-----------|------------|------------|------------|------------|---------------------------|

| 3.3                     | 10        | 31.6       | 10         | 620        | 390        | 63.4                      |

| 5                       | 10        | 53.6       | 10         | 845        | 390        | 100                       |

#### Table 6: 700kHz, 24V<sub>IN</sub>

| V <sub>OUT</sub><br>(V) | L<br>(µH) | R1<br>(kΩ) | R2<br>(kΩ) | R4<br>(kΩ) | C4<br>(pF) | R <sub>FREQ</sub><br>(kΩ) |

|-------------------------|-----------|------------|------------|------------|------------|---------------------------|

| 3.3                     | 10        | 31.6       | 10         | 560        | 390        | 44.2                      |

| 5                       | 10        | 54.9       | 10         | 620        | 390        | 69.8                      |

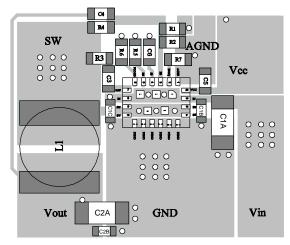

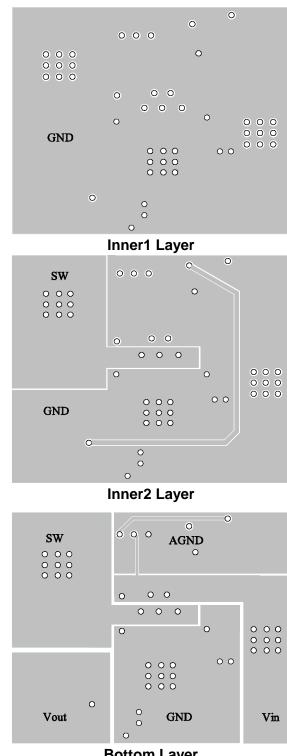

## LAYOUT RECOMMENDATION

- 1. Place high-current paths (GND, IN, and SW) very close to the device with short, direct, and wide traces.

- 2. Place input capacitors on both VIN sides (PIN8 and PIN19) and as close to the IN and GND pins as possible.

- 3. Place the decoupling capacitor as close to the Vcc and GND pins as possible.

- 4. Keep the switching node SW short and far away from the feedback network.

- 5. Place the external feedback resistors next to the FB pin. Do not place vias on the FB trace.

- 6. Keep the BST voltage path (BST, C3, and SW) as short as possible.

- 7. Connect the bottom IN and SW pads to a large copper area to achieve optimal thermal performance.

- 8. A four-layer layout is strongly recommended to achieve optimal thermal performance.

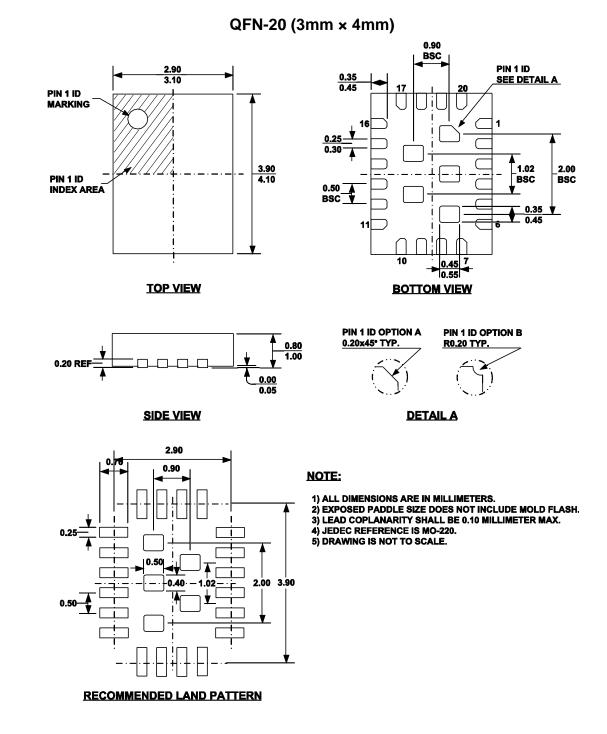

Top Layer

Bottom Layer Figure 10: PCB Layout

## **TYPICAL APPLICATION CIRCUITS**

## **PACKAGE INFORMATION**

**NOTICE:** The information in this document is subject to change without notice. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.