# MP8868 High-Efficiency, 10A, 17V, Synchronous

Step-Down Converter with I<sup>2</sup>C Interface

The Future of Analog IC Technology

# DESCRIPTION

The MP8868 is a high-frequency, synchronous, rectified, stepdown, switch-mode converter with an I2C control interface. Its fully integrated solution achieves a 10A output current with excellent load and line regulation over a wide input-supply range.

The reference voltage level is controlled on-thefly by the I<sup>2</sup>C serial interface with the reference voltage range adjustable from 0.6V to 1.87V in 10mV steps. In addition, the voltage scaling slew rate, the switching frequency, enable, and power-save mode are selectable through the I2C interface.

Current-mode operation provides fast transient response and eases loop stabilization. EN/SYNC supports external clock synchronization, and an open-drain power good pin indicates when the output voltage is in the nominal range. Full protection features include:

- Over-voltage protection (OVP)

- Hiccup over-current protection (OCP)

- Thermal shutdown

The MP8868 requires a minimal number of available. standard. readily external components, and it is available in a QFN-14 (3x4mm) package.

# **FEATURES**

- Wide 4.5V-to-17V Operating Input Range

- 1% Internal Reference Accuracy

- 1<sup>2</sup>C Programmable Reference Output Voltage

- Range from 0.6V to 1.87V in 10mV Steps with Slew Rate Control

- I<sup>2</sup>C Selectable Switching Frequency •

- 200kHz-2MHz Synchronized External Clock •

- OTP, OCP Hiccup Indication Via I2C

- Selectable PSM and Fs Through I2C •

- Programmable Soft-Start Time •

- **Open-Drain Power Good Indicator**

- Small 3x4mm QFN14 Package

# APPLICATIONS

- SoC and Media Processors

- **FPGA-based Systems**

- **ASIC Supplies**

- **Distributed Power Systems**

All MPS parts are lead-free, halogen free, and adhere to the RoHS directive. For MPS green status, please visit MPS website under Quality Assurance. "MPS" and "The Future of Analog IC Technology" are Registered Trademarks of Monolithic Power Systems, Inc.

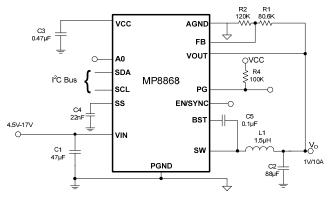

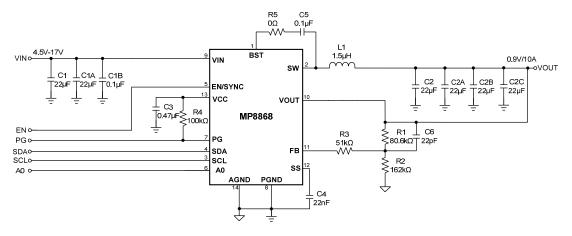

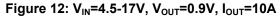

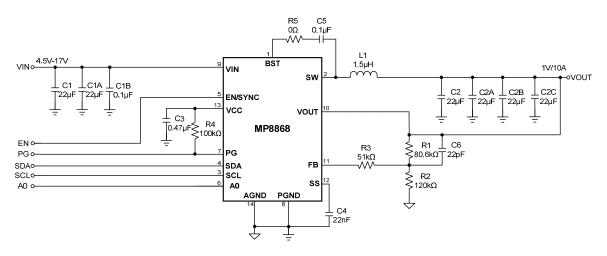

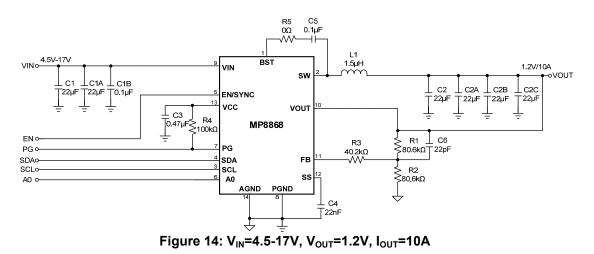

# TYPICAL APPLICATION

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2015 MPS. All Rights Reserved.

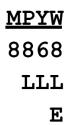

# **ORDERING INFORMATION**

| Part Number* | Package          | Top Marking |  |  |

|--------------|------------------|-------------|--|--|

| MP8868GLE    | QFN-14 (3mmx4mm) | See Below   |  |  |

\* For Tape & Reel, add suffix -Z (e.g. MP8868GLE-Z);

# **TOP MARKING**

MP: MPS prefix: Y: year code; W: week code: 8868: first four digits of the part number; LLL: lot number; E: product code;

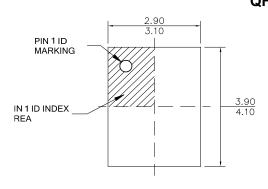

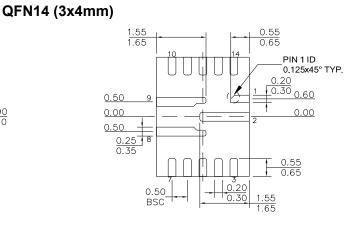

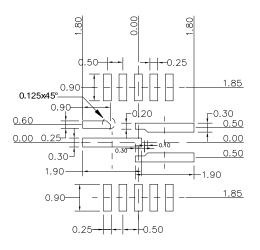

# PACKAGE REFERENCE

# ABSOLUTE MAXIMUM RATINGS (1)

| V <sub>IN</sub> | 0.3V to 19V |

|-----------------|-------------|

| V <sub>SW</sub> |             |

| -0.3V (-6V for <10ns) to 20V    | (24V for <10ns)               |

|---------------------------------|-------------------------------|

| V <sub>BST</sub>                | V <sub>SW</sub> +5.5V         |

| All Other Pins                  | -0.3V to 5.5V <sup>(2)</sup>  |

| Continuous Power Dissipation (T | $T_{A} = +25^{\circ}C)^{(3)}$ |

| QFN 3x4                         | 2.6W                          |

| Junction Temperature            | 150°C                         |

| Lead Temperature                | 260°C                         |

| Storage Temperature             | -65°C to 150°C                |

# Recommended Operating Conditions (4)

| Supply Voltage V <sub>IN</sub>                 | 1.5V to 17V |

|------------------------------------------------|-------------|

| Output Voltage Vout                            | 0.6V        |

| to $V_{IN} \times D_{MAX}$ or $5.5 V^{(5)}$    |             |

| Operating Junction Temp. (T <sub>J</sub> )40°C | C to +125°C |

## *Thermal Resistance* <sup>(6)</sup> *θ<sub>JA</sub> θ<sub>JC</sub>* QFN (3x4).....48......48.......48......

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) About the details of EN pin's ABS MAX rating, please refer to Page 15, Enable/SYNC control section.

- 3) The maximum allowable power dissipation is a function of the maximum junction temperature T<sub>J</sub> (MAX), the junction-toambient thermal resistance  $\theta_{JA}$ , and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub> (MAX) = (T<sub>J</sub> (MAX)-T<sub>A</sub>)/ $\theta_{JA}$ . Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- 4) The device is not guaranteed to function outside of its operating conditions.

- 5) The output voltage can't exceed 5.5V absolute maximum value at any input condition.

- 6) Measured on JESD51-7, 4-layer PCB.

# **ELECTRICAL CHARACTERISTICS**

$V_{IN} = 12V$ ,  $T_J = -40^{\circ}$ C to  $125^{\circ}$ C<sup>(7)</sup>, unless otherwise noted, typical value is based on average value when  $T_J=25^{\circ}$ C.

| Parameter                                         | Symbol                                           | Condition                                                                     | Min          | Тур  | Мах          | Units           |

|---------------------------------------------------|--------------------------------------------------|-------------------------------------------------------------------------------|--------------|------|--------------|-----------------|

| Supply Current (Shutdown)                         | I <sub>IN</sub>                                  | V <sub>EN</sub> =0V                                                           |              | 9    | 13           | μA              |

| Supply Current (Quiescent)                        | l <sub>q</sub>                                   | V <sub>EN</sub> = 2V, No Switching,<br>PFM mode                               |              | 560  | 800          | μA              |

| HS Switch-On Resistance                           | $HS_{RDS-ON}$                                    | V <sub>BST-SW</sub> = 5V                                                      |              | 26   |              | mΩ              |

| LS Switch-On Resistance                           | $LS_{RDS-ON}$                                    | $V_{CC} = 5V$                                                                 |              | 11   |              | mΩ              |

| Switch Leakage                                    | $\mathrm{SW}_{\mathrm{LKG}}$                     | $V_{EN}$ = 0V, $V_{SW}$ =12V or 0V, $T_J$ = 25°C                              |              |      | 1            | μA              |

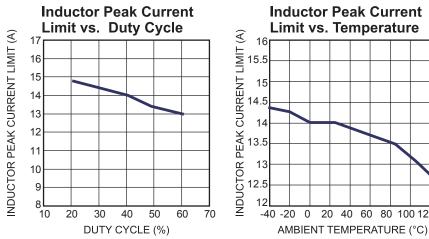

| High Side Current Limit <sup>(8)</sup>            | I <sub>LIMIT_H</sub>                             | Under 40% Duty<br>Cycle                                                       | 11.7         | 14   |              | А               |

| Oscillator Frequency                              | $f_{SW}$                                         | $T_J = 25^{\circ}C$<br>$T_J = -40^{\circ}C$ to $125^{\circ}C$                 | 400<br>350   | 500  | 570<br>600   | kHz             |

| Fold-Back Frequency                               | f <sub>VOUT</sub>                                | V <sub>FB</sub> = 150mV                                                       |              | 0.5  |              | f <sub>SW</sub> |

| SYNC Frequency Range                              | <b>f</b> <sub>SYNC</sub>                         |                                                                               | 200          |      | 2000         | kHz             |

| Maximum Duty Cycle                                | D <sub>MAX</sub>                                 | $V_{FB}$ = 500mV,<br>fs=500kHz                                                | 93           | 95   |              | %               |

| Minimum On Time <sup>(8)</sup>                    | t <sub>on_min</sub>                              |                                                                               |              | 40   |              | ns              |

| FB Voltage                                        | $V_{\text{FB}}$                                  | $T_{J} = 25^{\circ}C$<br>$T_{J} = -40^{\circ}C \text{ to } 85^{\circ}C^{(8)}$ | 594<br>588   | 600  | 606<br>612   | mV              |

| VOUT                                              | V <sub>OUT=</sub> 1.2V<br>V <sub>OUT=</sub> 1.2V | $T_J = 25^{\circ}C$ 1188 $T_J = -40^{\circ}C$ to $85^{\circ}C^{(8)}$ 1182     |              | 1200 | 1212<br>1218 | mV              |

| FB pin Current                                    | I <sub>FB</sub>                                  | V <sub>FB</sub> = 620mV                                                       |              | 10   | 50           | nA              |

| A0 pin High Level                                 | V <sub>ADD_H</sub>                               |                                                                               | 2            |      |              | V               |

| A0 pin Low Level                                  | V <sub>ADD_L</sub>                               |                                                                               |              |      | 0.4          | V               |

|                                                   |                                                  | V <sub>EN</sub> = 0V, T <sub>J</sub> = 25°C                                   | 4.3          |      | 7.5          | μA              |

| EN Pull-up Current                                | I <sub>EN_PU</sub>                               | V <sub>EN</sub> = 0V,<br>T <sub>J</sub> = -40°C to 125°C                      | 3.2          | 6.2  | 8            |                 |

| EN Rising Threshold                               | V <sub>EN_Rise</sub>                             | T <sub>J</sub> = 25°C                                                         | 1.28         | 1.4  | 1.5          | V               |

|                                                   | V EN_Rise                                        | $T_J$ = -40°C to 125°C                                                        | 1.26         | 1.4  | 1.52         | v               |

| EN Hysteresis                                     | $V_{\text{EN}_{\text{HYS}}}$                     | T <sub>J</sub> = 25°C                                                         | 120          | 170  | 220          | mV              |

|                                                   | VEN_HTS                                          | $T_J = -40^{\circ}C$ to $125^{\circ}C$                                        | 100          |      | 240          |                 |

| EN Turn Off Delay                                 | EN <sub>td-off</sub>                             |                                                                               |              | 10   |              | μs              |

| VIN Under-Voltage Lockout<br>Threshold-Rising     | INUV <sub>Vth</sub>                              | T <sub>J</sub> = 25°C                                                         | 4.04         | 4.2  | 4.36         | v               |

| Threshold-Nising                                  |                                                  | $T_J = -40^{\circ}C$ to $125^{\circ}C$                                        | 4.02         |      | 4.38         |                 |

| VIN Under-Voltage Lockout<br>Threshold-Hysteresis | INUV <sub>HYS</sub>                              |                                                                               | 560          | 660  | 740          | mV              |

| Power Good UV Threshold Rising                    | PGVth-Hi                                         | $T_{J} = 25^{\circ}C$ $T_{J} = -40^{\circ}C \text{ to } 125^{\circ}C$         | 0.85<br>0.84 | 0.9  | 0.94<br>0.95 | VOUT            |

| Power Good UV Threshold Falling                   | PGVth-Lo                                         | $T_{J} = 25^{\circ}C$ $T_{J} = -40^{\circ}C \text{ to } 125^{\circ}C$         | 0.64<br>0.63 | 0.7  | 0.73<br>0.74 | VOUT            |

**ELECTRICAL CHARACTERISTICS** *(continued)*  $V_{IN} = 12V$ ,  $T_J = -40^{\circ}C$  to  $125^{\circ}C^{(7)}$ , unless otherwise noted, typical value is based on average value when  $T_J=25^{\circ}C$ .

| Parameter                         | Symbol               | Condition                                            | Min   | Тур  | Max  | Units            |  |

|-----------------------------------|----------------------|------------------------------------------------------|-------|------|------|------------------|--|

| Power Good Deglitch time          | PGTd                 |                                                      |       | 100  | 160  | μs               |  |

| OVP Discharge Resistor            | R <sub>ov</sub>      | From VOUT pin to GND                                 |       | 35   | 70   | Ω                |  |

| OVP Rising Threshold              | V <sub>EN_Rise</sub> | VOUT and FB pins, $T_J = 25^{\circ}C$                | 1114% |      | 126% | V <sub>REF</sub> |  |

|                                   | V EN_Rise            | VOUT and FB pins,<br>T <sub>J</sub> = -40°C to 125°C | 120%  |      | 127% | ¥ REF            |  |

| OVP Falling Threshold             | $V_{EN\_Fall}$       | VOUT and FB pins                                     | 101%  | 105% | 108% | $V_{REF}$        |  |

| Soft-Start Current                | i <sub>ss</sub>      |                                                      | 7     | 10   | 12   | μA               |  |

| VCC Voltage                       | V <sub>CC</sub>      | $T_J = -40^{\circ}C$ to $125^{\circ}C$               | 4.75  | 4.95 | 5.1  | V                |  |

| VCC Load Regulation               |                      | I <sub>CC</sub> =5mA                                 |       | 1    | 3    | %                |  |

| Thermal Shutdown <sup>(8)</sup>   | T <sub>TSD</sub>     |                                                      |       | 160  |      | °C               |  |

| Thermal Hysteresis <sup>(8)</sup> | T <sub>TSD_HYS</sub> |                                                      |       | 20   |      | °C               |  |

#### Notes:

7) Not tested in production and guaranteed by over-temperature correlation.

8) Guaranteed by Design and Characterization Test.

#### **I/O Level Characteristics**

| Parameter                                                                            | Symbol           | Condition                                                                                       | HS-N                     | /lode                     | LS-                      | Units                     |       |

|--------------------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------|--------------------------|---------------------------|--------------------------|---------------------------|-------|

| Falallielei                                                                          | Symbol           | Condition                                                                                       | Min Max                  |                           | Min Max                  |                           | Units |

| Low-level input voltage                                                              | V <sub>IL</sub>  |                                                                                                 | -0.5                     | 0.3<br>V <sub>Bus</sub>   | -0.5                     | 0.3V<br>Bus               | V     |

| High-level input voltage                                                             | V <sub>IH</sub>  |                                                                                                 | 0.7<br>3V <sub>Bus</sub> | V <sub>Bus</sub> +<br>0.5 | 0.7<br>V <sub>Bus</sub>  | V <sub>Bus</sub> +<br>0.5 | V     |

| Hysteresis of Schmitt trigger                                                        | V                | V <sub>Bus</sub> >2V                                                                            | 0.05V<br><sub>Bus</sub>  | -                         | 0.05<br>V <sub>Bus</sub> | -                         | V     |

| inputs                                                                               | V <sub>HYS</sub> | V <sub>Bus</sub> <2V                                                                            | 0.1<br>V <sub>Bus</sub>  | -                         | 0.1<br>V <sub>Bus</sub>  | -                         | v     |

| Low-level output voltage(Open                                                        |                  | V <sub>Bus</sub> >2V                                                                            | 0                        | 0.4                       | 0                        | 0.4                       |       |

| drain) at 3mA sink current                                                           | V <sub>OL</sub>  | V <sub>Bus</sub> <2V                                                                            | 0                        | 0.2<br>V <sub>Bus</sub>   | 0                        | 0.2V <sub>B</sub>         | V     |

| Low-level output current                                                             | I <sub>OL</sub>  |                                                                                                 | -                        | 3                         | -                        | 3                         | mA    |

| Transfer gate on resistance for<br>currents between SDA and<br>SCAH, or SCL and SCLH | R <sub>onL</sub> | VOL level, IOL=3mA                                                                              | -                        | 50                        | -                        | 50                        | Ω     |

| Transfer gate on resistance<br>between SDA and SCAH, or<br>SCL and SCLH              | $R_{onH}$        | Both signals (SDA and SDAH,<br>or SCL and SCLH) at VBus<br>level                                | 50                       | -                         | 50                       | -                         | kΩ    |

| Pull-up current of the SCLH current source                                           | I <sub>cs</sub>  | SCLH output levels between 0.3VBus and $0.7V_{Bus}$                                             | 2                        | 6                         | 2                        | 6                         | mA    |

| Rise time of the SCLH or SCL                                                         | 4                | Output rise time (current source<br>enabled) with an external pull-<br>up current source of 3mA |                          |                           |                          |                           |       |

| signal                                                                               | t <sub>rCL</sub> | Capacitive load from 10pF to 100pF                                                              | 10                       | 40                        |                          |                           | ns    |

|                                                                                      |                  | Capacitive load of 400pF                                                                        | 20                       | 80                        |                          |                           | ns    |

| Fall time of the SCLH or SCL                                                         |                  | Output fall time (current source<br>enabled) with an external pull-<br>up current source of 3mA |                          |                           |                          |                           |       |

| signal                                                                               | t <sub>fCL</sub> | Capacitive load from 10pF to 100pF                                                              | 10                       | 40                        |                          |                           | ns    |

|                                                                                      |                  | Capacitive load of 400pF                                                                        | 20                       | 80                        | 20                       | 250                       | ns    |

| Rise time of SDAH signal                                                             | t <sub>rDA</sub> | Capacitive load from 10pF to 100pF                                                              | 10                       | 80                        | -                        | -                         | ns    |

|                                                                                      |                  | Capacitive load of 400pF                                                                        | 20                       | 160                       | 20                       | 250                       | ns    |

| Fall time of SDAH signal                                                             | t <sub>fDA</sub> | Capacitive load from 10pF to 100pF                                                              | 10                       | 80                        | -                        | -                         | ns    |

|                                                                                      |                  | Capacitive load of 400pF                                                                        | 20                       | 160                       | 20                       | 250                       | ns    |

| Pulse width of spikes that must be suppressed by the input filter                    | t <sub>SP</sub>  |                                                                                                 | 0                        | 10                        | 0                        | 50                        | ns    |

| Input current each I/O pin                                                           | li               | Input voltage between $0.1V_{\text{Bus}}$ and $0.9V_{\text{Bus}}$                               | -                        | 10                        | -10                      | +10                       | uA    |

| Capacitance for each I/O pin                                                         | Ci               |                                                                                                 | -                        | 10                        | -                        | 10                        | pF    |

#### Notes:

$V_{\mbox{\tiny Bus}}$  is the I^2C Bus Voltage, 3.0V to 3.6V range, 3.3V typical

# I<sup>2</sup>C Port Signal Characteristics

| Parameter                                                                                    | Symbol              | Condition                          | Cb= | 100pF                | Cb=400               | Units |       |

|----------------------------------------------------------------------------------------------|---------------------|------------------------------------|-----|----------------------|----------------------|-------|-------|

| Farameter                                                                                    | Symbol              | Condition                          | Min | Max                  | Min                  | Max   | Units |

| SCLH and SCL clock<br>frequency                                                              | f <sub>SCHL</sub>   |                                    | 0   | 3.4                  | 0                    | 0.4   | MHz   |

| Set-up time for a repeated START condition                                                   | T <sub>SU;STA</sub> |                                    | 160 | -                    | 600                  | -     | ns    |

| Hold time (repeated) START condition                                                         | T <sub>HD;STA</sub> |                                    | 160 | -                    | 600                  | -     | ns    |

| Low period of the SCL clock                                                                  | t <sub>LOW</sub>    |                                    | 160 | -                    | 1300                 | -     | ns    |

| High period of the SCL clock                                                                 | t <sub>HIGH</sub>   |                                    | 60  | -                    | 600                  | -     | ns    |

| Data set-up time                                                                             | T <sub>SU:DAT</sub> |                                    | 10  | -                    | 100                  | -     | ns    |

| Data hold time                                                                               | T <sub>HD;DAT</sub> |                                    | 0   | 70                   | 0                    | -     | ns    |

| Rise time of SCLH signal                                                                     | t <sub>rCL</sub>    |                                    | 10  | 40                   | 20*0.1Cb             | 300   | ns    |

| Rise time of SCLH signal after<br>a repeated START condition<br>and after an acknowledge bit | t <sub>fCL1</sub>   |                                    | 10  | 80                   | 20*0.1Cb             | 300   | ns    |

| Fall time of SCLH signal                                                                     | T <sub>fCL</sub>    |                                    | 10  | 40                   | 20*0.1Cb             | 300   | ns    |

| Rise time of SDAH signal                                                                     | t <sub>fDA</sub>    |                                    | 10  | 80                   | 20*0.1Cb             | 300   | ns    |

| Fall time of SDAH signal                                                                     | T <sub>fDA</sub>    |                                    | 10  | 80                   | 20*0.1Cb             | 300   | ns    |

| Set-up time for STOP condition                                                               | T <sub>SU;STO</sub> |                                    | 160 | -                    | 600                  | -     | ns    |

| Bus free time between a STOP and START condition                                             | T <sub>BUF</sub>    |                                    | 160 | -                    | 1300                 | -     | ns    |

| Data Valid Time                                                                              | T <sub>VD;DAT</sub> |                                    | -   | 16                   | -                    | 90    | ns    |

| Data valid acknowledge time                                                                  | T <sub>VD;ACK</sub> |                                    | -   | 160                  | -                    | 900   | ns    |

| Capacitive load for each bus                                                                 | Cb                  | SDAH and SCLH line                 | -   | 100                  | -                    | 400   | pF    |

| line                                                                                         |                     | SDAH+SDA line and<br>SCLH+SCL line | -   | 400                  | -                    | 400   | pF    |

| Noise margin at the LOW level                                                                | Ci                  | For each connected device          | -   | $0.1 V_{\text{Bus}}$ | $0.1 V_{\text{Bus}}$ | -     | V     |

| Noise margin at the HIGH level                                                               | V <sub>nH</sub>     | For each connected device          | -   | $0.2V_{\text{Bus}}$  | $0.2V_{\text{Bus}}$  | -     | V     |

#### Notes:

V<sub>Bus</sub> is the I<sup>2</sup>C Bus Voltage, 3.0V to 3.6V range, 3.3V typical

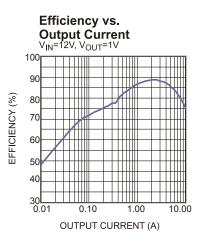

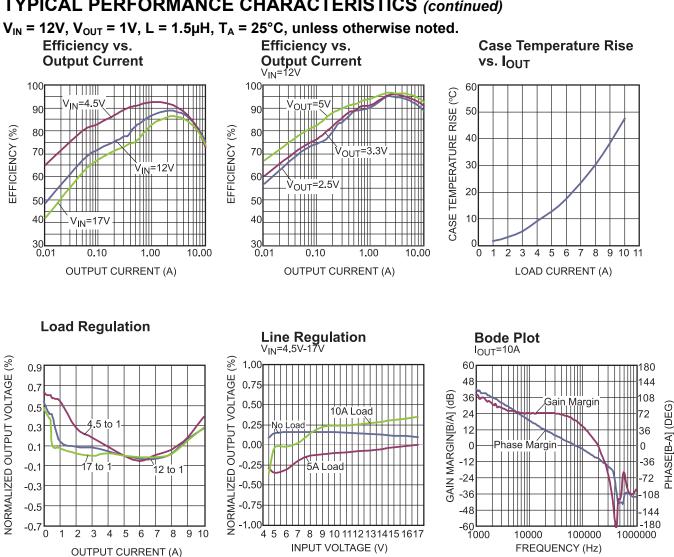

#### TYPICAL PERFORMANCE CHARACTERISTICS $V_{IN} = 12V$ , $V_{OUT} = 1V$ , $L = 1.5\mu$ H, $T_A = 25^{\circ}$ C, unless otherwise noted. **Enabled Supply Current Disabled Supply Current VIN UVLO Rising Threshold** vs. Input Voltage vs. Input Voltage vs. Temperature V<sub>EN</sub>=0V V<sub>FB</sub>=0.65V 4.4 700 15 ENABLED SUPPLY CURRENT (µA) DISABLED SUPPLY CURRENT (µA) 14 €4.35 650 4.33 4.3 4.3 4.2 94.15 4.1 94.15 13 600 12 11 550 10 500 9 450 8 7 400 6 ₹4.05 350 300 4 -40 -20 6 7.5 9 10.5 12 13.5 15 16.5 7.5 9 10.5 12 13.5 15 16.5 0 20 40 60 80 100 120 125 4.5 4.5 6 **INPUT VOLTAGE (V)** INPUT VOLTAGE (V) AMBIENT TEMPERATURE (°C) EN Rising Threshold vs. **Reference Voltage vs.** Switching Frequency vs. **Ambient Temperature Temperature Temperature** 1.6 618 (ZHX) 540 614 1.55 (mV) EN RISING THRESHOLD (V) 610 ANITCHING FREFQUENCY 480 460 470 470 470 470 470 470 1.5 REFERENCE VOLTAGE 606 1.45 602 1.4 598 1.35 594 1.3 590

586

582

-40 -20

20 40 60 80 100 120 125

AMBIENT TEMPERATURE (°C)

20 40 60

AMBIENT TEMPERATURE (°C)

0

80 100 120125

1.25

1.2

-40 -20

0

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2015 MPS. All Rights Reserved.

20 40 60 80 100 120 125

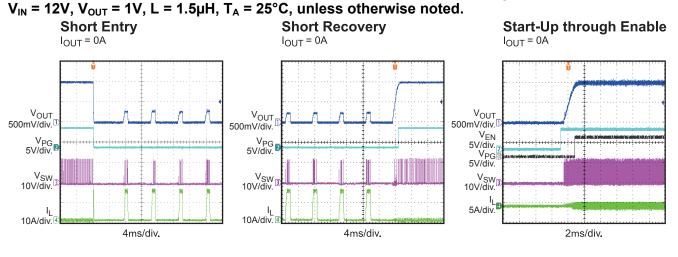

# **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

# **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

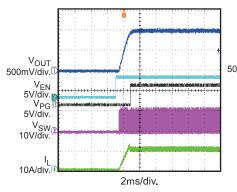

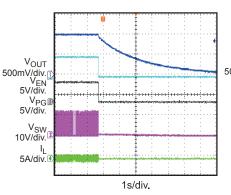

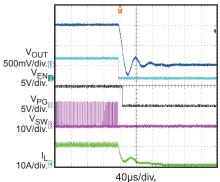

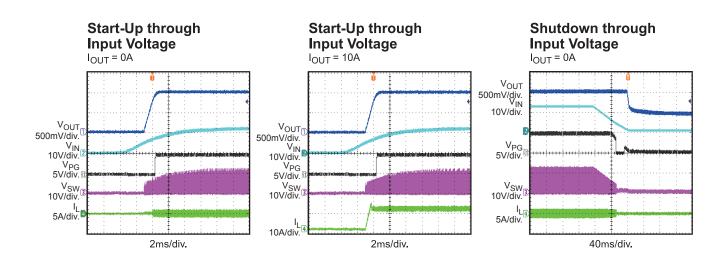

Performance waveforms are tested on the evaluation board of the Design Example section.

Start-Up through Enable I<sub>OUT</sub> = 10A

Shutdown through Enable

# Shutdown through Enable I<sub>OUT</sub> = 10A

# **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

Performance waveforms are tested on the evaluation board of the Design Example section.  $V_{IN} = 12V$ ,  $V_{OUT} = 1V$ ,  $L = 1.5\mu$ H,  $T_A = 25^{\circ}$ C, unless otherwise noted.

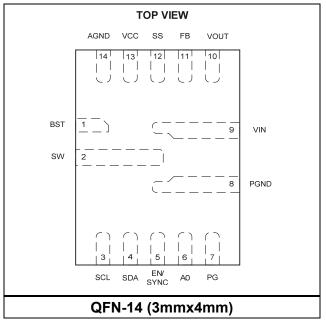

# **PIN FUNCTIONS**

| QFN14<br>PIN# | Name    | Description                                                                                                                                                                                          |

|---------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | BST     | Bootstrap. Requires a capacitor between SW and BST pins to form a floating supply across the high-side switch driver.                                                                                |

| 2             | SW      | Switch Output. Connect using a wide PCB trace.                                                                                                                                                       |

| 3             | SCL     | I <sup>2</sup> C Serial Clock.                                                                                                                                                                       |

| 4             | SDA     | I <sup>2</sup> C Serial Data.                                                                                                                                                                        |

| 5             | EN/SYNC | EN high to enable the MP8868. EN pin has internal 5.4uA pull-up current to 5V, so it can auto startup when EN floating. Apply an external clock can to the EN pin to change the switching frequency. |

| 6             | A0      | I <sup>2</sup> C address set pin. Left this pin float or pull it to VCC can set one address. Pull A0 pin to ground can set another different address.                                                |

| 7             | PG      | Power Good Indication. Open drain structure. PG switches low if the output voltage is out of regulation window. PG only indicates UV condition.                                                      |

| 8             | PGND    | System Power Ground. Reference ground of the regulated output voltage. Requires special consideration during PCB layout. Connect to ground plane with copper traces and vias.                        |

| 9             | VIN     | Supply Voltage. The MP8868 operates from a 4.5V-to-17V input rail. Requires ceramic capacitor to decouple the input rail. Connect using a wide PCB trace.                                            |

| 10            | VOUT    | Sense input of output voltage. Connect it to the positive terminal of loading.                                                                                                                       |

| 11            | FB      | Feedback. Connect to the tap of an external resistor divider from the output to GND to set the output voltage in FB control loop.                                                                    |

| 12            | SS      | Soft start pin. Connect a capacitor from SS to ground can set the soft start time.                                                                                                                   |

| 13            | VCC     | Internal LDO regulator output. Decouple with 0.47µF capacitor.                                                                                                                                       |

| 14            | AGND    | Signal Ground. AGND is not internally directly connected to System Ground, make sure AGND connected to system Ground in PCB layout.                                                                  |

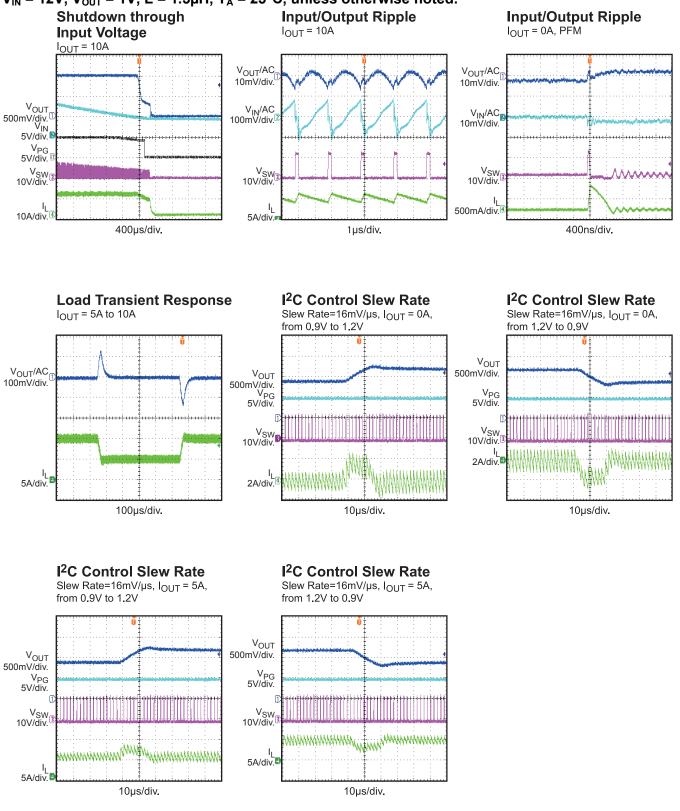

FUNCTIONAL BLOCK DIAGRAM

Figure 1: Functional Block Diagram

# **OPERATION**

The MP8868 is a high-frequency, synchronous, rectified, step-down, switch-mode converter with built-in power MOSFETs. It offers a very compact solution that achieves a 10A output current with excellent load and line regulation over a wide input supply range.

The MP8868 has three working modes: CCM (Continues-Conduction Mode), AAM mode (Advanced Asynchronous Modulation) and DCM (Discontinues-Conduction Mode). The MP8868 default operation mode is CCM. When set MODE bit(reg01[0]) in the I<sup>2</sup>C register to "0". MP8868 can works in the AAM mode.

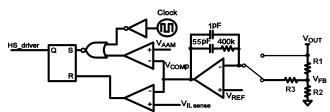

#### **CCM** Control Operation

In CCM the internal clock initiates the PWM cycle, the HS-FET turns on and remains on until  $V_{ILsense}$  reaches the value set by  $V_{COMP}$ , after a period of dead time, the LS-FET will turn on and remain on until the next clock cycle starts. The device will repeat the same operation in every clock cycle to regulate the output voltage.

If within 95% (500kHz switching frequency) of one PWM period,  $V_{ILsense}$  does not reach the value set by  $V_{COMP}$ , the HS power MOSFET is forced off.

# AAM Control Operation

In the light load condition, MP8868 works in AAM (Advanced Asynchronous Modulation) mode if Mode bit is set to "0". Refer to Figure 2, the  $V_{AAM}$  is an internal fixed voltage when input and output voltages are fixed.  $V_{COMP}$  is the error amplifier output which represents the peak inductor current information. When  $V_{COMP}$  is lower than  $V_{AAM}$ , the internal clock is blocked, thus the MP8868 skips some pulses and achieves the light load power save. Refer to AN032 for more detail.

The internal clock resets every time when  $V_{COMP}$  is higher than  $V_{AAM}$ . At the same time the HS-FET(High-Side MOSFET) turns on and remains on until  $V_{ILsense}$  reaches the value set by  $V_{COMP}$ .

The light load feature in this device is optimized for 12V input applications.

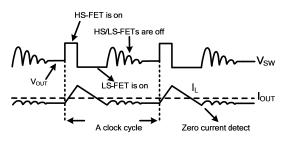

Figure 2: Simplified AAM Control Logic DCM Control Operation

The V<sub>COMP</sub> voltage ramps up with the increasing of the output current, when its minimum value exceeds V<sub>AAM</sub>, the device will enter DCM (Discontinues-Conduction Mode). In this mode the internal clock initiates the PWM cycle, the HS-FET turns on and remains on until V<sub>ILsense</sub> reaches the value set by V<sub>COMP</sub>, after a period of dead time, the LS-FET (Low-Side MOSFET) will turn on and remain on until the inductor current value decreases to zero. The device will repeat the same operation in every clock cycle to regulate the output voltage.

Figure 3: DCM Control Operation

# **VCC Regulator**

A 5V internal regulator powers most of the internal circuitries. This regulator takes the V<sub>IN</sub> input and operates in the full V<sub>IN</sub> range. When V<sub>IN</sub> is greater than 5.0V, the output of the regulator is in full regulation. When V<sub>IN</sub> is lower than 5.0V, the output voltage decreases and follows the input voltage. A  $0.47\mu$ F ceramic capacitor for decoupling purpose is required.

#### **Error Amplifier**

The error amplifier compares the FB pin voltage against the internal reference (REF) for FB control loop and outputs the COMP voltage which controls the power MOSFET current. In I<sup>2</sup>C mode, the FB pin is opened and VOUT pin is connected to the EA non-inverter input. The optimized internal compensation network

minimizes the external component count and simplifies the control loop design.

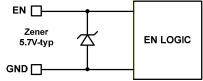

#### **EN/SYNC** Control

EN/SYNC is a digital control pin that turns the regulator including  $I^2C$  block on and off. Drive EN/SYNC high to turn on the regulator; drive it low to turn it off. An internal 5.4µA pull-up current to 5V power supply allows auto startup when EN/SYNC pin is floating.

The EN/SYNC pin is clamped internally using a 5.7 V series-Zener-diode as shown in Figure 4. Connecting the EN/SYNC input pin through a pull-up resistor to the voltage on the  $V_{IN}$  pin limits the EN/SYNC input current to less than 100µA.

For example, with 12V connected to Vin,  $R_{PULLUP} \ge (12V - 5.7V) \div 100 \mu A = 63 k \Omega.$

Connecting the EN/SYNC pin is directly to a voltage source without any pullup resistor requires limiting the amplitude of the voltage source to  $\leq$ 5.5V to prevent damage to the Zener diode.

Figure 4: 5.7V Zener Diode Connection

For external clock synchronization, connect a clock with a frequency range between 200kHz and 2MHz to EN/SYNC pin. The internal clock rising edge will synchronize with the external clock rising edge once external clock is present. Set the external clock signal with a pulse width less than 80% of one internal clock cycle time.

#### Under-Voltage Lockout (UVLO)

Under-voltage lockout (UVLO) protects the chip from operating at insufficient supply voltage. The MP8868 UVLO comparator monitors the output voltage of the internal regulator, VCC. The UVLO rising threshold is about 4.2V while its falling threshold is 3.54V.

#### Soft-Start

The MP8868 employs soft start (SS) mechanism to ensure smooth output during power-up. When the EN pin becomes high, an internal current source ( $10\mu A$ ) charges up the

SS capacitor. The SS capacitor voltage takes over the REF voltage to the PWM comparator. The output voltage smoothly ramps up with the SS voltage. Once the SS voltage reaches the same level as the REF voltage, it keeps ramping up while  $V_{REF}$  takes over the PWM comparator. At this point, the soft start finishes and it enters into steady state operation.

The SS capacitor value can be determined as follows:

$$C_{SS}(nF) = \frac{T_{SS}(ms) \times I_{SS}(\mu A)}{V_{REF}(V)}$$

If the output capacitors have large capacitance value, it's not recommended to set the SS time too small. Otherwise, it's easy to hit the current limit during SS.

#### **Pre-Bias Startup**

The MP8868 has been designed for monotonic startup into pre-biased output voltage. If the output is pre-biased to a certain voltage during startup, the voltage on the soft-start capacitor will be charged. When the soft-Start capacitor's voltage exceeds the sensed output voltage at the FB pin <sup>(9)</sup>, the part starts to turn on high side and low side power switches sequentially. Output voltage starts to ramp up following with soft-start slew rate.

Note:

FB pin voltage in FB control loop, or VOUT pin voltage in I<sup>2</sup>C control loop.

#### Power Good Indicator

The MP8868 has power good (PG) output used to indicate whether the output voltage of the module is ready or not. The PG pin is an open drain output. Connect PG pin to VCC or other voltage source through a pull up resistor (e.g. 100k $\Omega$ ). When the input voltage is applied, the PG pin is pulled down to GND. When V<sub>FB</sub><sup>(9)</sup> is above 90% of V<sub>REF</sub>, the PG pin will be pulled high after 100us delay time. During normal operation, the PG pin will be pulled low when the V<sub>FB</sub><sup>(9)</sup>. drops below 70% of V<sub>REF</sub> after 100us delay.

When UVLO or OTP happens, the PG pin will be pulled low immediately; When OC(Over current) happens, the PG pin will be pulled low MP8868 – SYNCHRONOUS STEP-DOWN CONVERTER

when  $V_{FB}^{(9)}$ . drops below 70% of  $V_{REF}$  after 100us delay.

The PG won't response to output over voltage condition.

The PG bit in the  $I^2C$  register have the same indication as the external PG pin.

# **Output over Voltage Protection (OVP)**

MP8868 monitors both FB pin and VOUT pin to detect over voltage event. When "V\_BOOT" bit=1, internal comparator monitors FB pin while "V\_BOOT" bit=0, it monitors VOUT pin. When the feedback voltage becomes higher than 120% of the internal reference voltage, the controller will enter linear discharge mode. During this period, there is a 35 $\Omega$  resistor connected between VOUT pin and ground, this will then discharge the output and try to keep it within the normal range. Once output voltage falls lower than 105% of reference, controller exits linear discharge mode.

# **Over-Current-Protection and Hiccup**

The MP8868 has a cycle-by-cycle over-current limit. When the inductor current peak value exceeds the set current limit threshold, the HS-FET will turn off and the LS-FET will turn on and remains on until the inductor current falls below the internal "valley" current limit threshold. The "valley" current limit circuit is employed to decrease the operation frequency after the "peak" current limit threshold is triggered. Meanwhile, the output voltage drops until  $V_{FB}^{(9)}$ is below the Under-Voltage (UV) thresholdtypically 30% below the reference. Once UV is triggered, the MP8868 enters hiccup mode to periodically restart the part. This protection mode is especially useful when the output is dead-shorted to ground. The average short circuit current is greatly reduced to alleviate thermal issues and to protect the regulator. The MP8868 exits the hiccup mode once the overcurrent condition is removed.

# **Thermal Shutdown**

Thermal shutdown prevents the chip from operating at exceedingly high temperatures. When the silicon die reaches temperatures that exceed 160°C, it shuts down the whole chip. When the temperature is less than its lower

threshold, typically 140°C, the chip is enabled again.

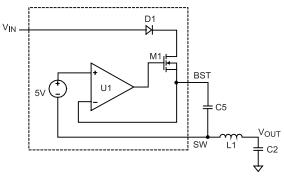

# Floating Driver and Bootstrap Charging

An external bootstrap capacitor powers the floating power MOSFET driver. This floating driver has its own UVLO protection. This UVLO's rising threshold is 2.2V with a hysteresis of 150mV. The bootstrap capacitor voltage is regulated internally by  $V_{IN}$  through D1, M1, C5, L1 and C2 (Figure ). If ( $V_{IN}$ - $V_{SW}$ ) exceeds 5V, U1 will regulate M1 to maintain a 5V BST voltage across C5.

Figure 5: Internal Bootstrap Charging Circuit

# Startup and Shutdown

If both  $V_{IN}$  and EN exceed their respective thresholds, the chip starts. The reference block starts first, generating stable reference voltage and currents, and then the internal regulator is enabled. The regulator provides a stable supply for the remaining circuitries.

Three events can shut down the chip: EN low,  $V_{IN}$  low, and thermal shutdown. In the shutdown procedure, the signaling path is first blocked to avoid any fault triggering. The COMP voltage and the internal supply rail are then pulled down. The floating driver is not subject to this shutdown command.

# I<sup>2</sup>C Control and Default Output Voltage

When the MP8868 is enabled which means EN=high and VIN>UVLO, the chip starts up to an output voltage which is set by FB feedback resistors with programmed soft-start time. After that, the  $I^2C$  bus can communicate with master. If the chip doesn't receive  $I^2C$  communication signal all the time, it works well through FB pin feedback and performs the similar behavior as traditional non- $I^2C$  part.

Once the I<sup>2</sup>C receives valid output reference voltage scaling instruction, if V\_BOOT="1", output voltage is determined by the resistor divider R1, R2 and V<sub>REF</sub> voltage. V<sub>OUT</sub> value can be calculated by following equation (V<sub>REF</sub> default value is 0.6V):

$$V_{OUT} = V_{REF} \times (1 + \frac{R1}{R2})$$

If V\_BOOT="0", the output voltage will be determined by  $I^2C$  control and the FB feedback loop is disabled.

The output reference voltage scaling is realized by adjusting internal reference voltage V\_REF which is the non-invert input of error amplifier. After MP8868 receives a valid data byte of output reference voltage setting, it searches the corresponding reference voltage from the truth table and then sends the command of adjusting Vref with controlled slew rate. The slew rate is determined by 3 bits of another register which can be read and write accordingly.

# I<sup>2</sup>C INTERFACE

# I<sup>2</sup>C Serial Interface Description

I<sup>2</sup>C is a 2-wire, bidirectional serial interface, consisting of a data line (SDA) and a clock line (SCL). The lines are externally pulled to a bus voltage when they are "idle". Connecting to the line, a master device generates the SCL signal device address and arranges the and communication sequence. MP8868 interface is an I<sup>2</sup>C slave. The I<sup>2</sup>C interface adds flexibility to the power supply solution. The output voltage, transition slew rate or other interesting parameters can be instantaneously controlled by I<sup>2</sup>C interface. The default I<sup>2</sup>C address of MP8868 is "62" (HEX) or "1100010" (BINARY) and is "6A" (HEX) or "1101010" if pull A0 pin to ground.

# Data validity

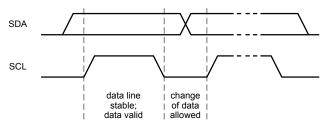

One clock pulse is generated for each data bit transferred. The data on the SDA line must be stable during the HIGH period of the clock. The HIGH or LOW state of the data line can only change when the clock signal on the SCL line is LOW (see Figure.6).

Figure 6: Bit transfer on the l<sup>2</sup>C-bus

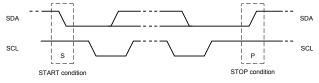

The START and STOP are signaled by the master device which signifies the beginning and the end of the  $I^2C$  transfer. The START condition is defined as the SDA signal transitioning from HIGH to LOW while the SCL is HIGH. The STOP condition is defined as the SDA signal transitioning from LOW to HIGH while the SCL is HIGH as shown in Figure 7.

START and STOP conditions are always generated by the master. The bus is considered to be busy after the START condition. The bus is considered to be free again after a minimum of 4.7uS after the STOP condition. The bus stays busy if a repeated START (Sr) is generated instead of a STOP condition. The START (S) and repeated START (Sr) conditions are functionally identical.

#### **Transfer Data**

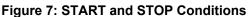

Every byte put on the SDA line must be 8-bits long. Each byte has to be followed by an acknowledge bit. The acknowledge-related clock pulse is generated by the master. The transmitter releases the SDA line (HIGH) during the acknowledge clock pulse. The receiver must pull down the SDA line during the acknowledge clock pulse so that it remains stable LOW during the HIGH period of this clock pulse.

Data transfers follow the format shown in Figure 8. After the START condition (S), a slave address is sent. This address is 7 bits long followed by an eighth bit which is a data direction bit (R/W) - a 'zero' indicates a transmission (WRITE), a 'one' indicates a request for data (READ). A data transfer is always terminated by a STOP condition (P) generated by the master. However, if a master still wishes to communicate on the bus, it can generate a repeated START condition (Sr) and address another slave without first generating a STOP condition.

#### Figure 8: A complete data transfer

The MP8868 requires a start condition, a valid I<sup>2</sup>C address, a register address byte, and a data byte for a single data update. After receipt of each byte, MP8868 acknowledges by pulling the SDA line low during the high period of a single clock pulse. A valid I<sup>2</sup>C address selects the MP8868. MP8868 performs an update on the falling edge of the LSB byte.

# **REGISER DESCRIPTION**

### **Register Map**

| ADD | NAME        | R/W | D7        | D6               | D5 | D4        | D3  | D2   | D1             | D0   |

|-----|-------------|-----|-----------|------------------|----|-----------|-----|------|----------------|------|

| 00  | VSEL        | R/W | V_BOOT    | Output Reference |    |           |     |      |                |      |

| 01  | SysCntlreg1 | R/W | EN        | GO_BIT           |    | Slew Rate |     |      | ching<br>Jency | Mode |

| 02  | ID1         | R   | Vendor ID |                  |    |           | Die | id   |                |      |

| 03  | Status      | R   | Reserved  |                  |    | VID_OK    | OC  | OTEW | OT             | PG   |

# **Register Description**

# 1. Reg00 VSEL

| NAME                | BITS   | DEFAULT | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------|--------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V_BOOT              | D7     | 1       | "FB" control loop enable bit. V_BOOT="1" means the output voltage is determined by resistor divider connecting to "FB" (FB control loop). V_BOOT="0" means the output voltage is controlled by I <sup>2</sup> C through "VOUT" (I <sup>2</sup> C control loop). This bit is helpful for the default output voltage setting before I <sup>2</sup> C signal comes. If the I <sup>2</sup> C is not used, the part works well with "FB" pin. |

| Output<br>Reference | D[6:0] | 0000000 | Set output voltage from 0.6V to 1.87V as Table 1. Default value is 0.6V.                                                                                                                                                                                                                                                                                                                                                                 |

#### Table 1 Output Voltage Chart

| D[6:0]   | VOUT | D[6:0]   | VOUT | D[6:0]   | VOUT | D[6:0]   | VOUT |

|----------|------|----------|------|----------|------|----------|------|

| 000 0000 | 0.60 | 010 0000 | 0.92 | 100 0000 | 1.24 | 110 0000 | 1.56 |

| 000 0001 | 0.61 | 010 0001 | 0.93 | 100 0001 | 1.25 | 110 0001 | 1.57 |

| 000 0010 | 0.62 | 010 0010 | 0.94 | 100 0010 | 1.26 | 110 0010 | 1.58 |

| 000 0011 | 0.63 | 010 0011 | 0.95 | 100 0011 | 1.27 | 110 0011 | 1.59 |

| 000 0100 | 0.64 | 010 0100 | 0.96 | 100 0100 | 1.28 | 110 0100 | 1.60 |

| 000 0101 | 0.65 | 010 0101 | 0.97 | 100 0101 | 1.29 | 110 0101 | 1.61 |

| 000 0110 | 0.66 | 010 0110 | 0.98 | 100 0110 | 1.30 | 110 0110 | 1.62 |

| 000 0111 | 0.67 | 010 0111 | 0.99 | 100 0111 | 1.31 | 110 0111 | 1.63 |

| 000 1000 | 0.68 | 010 1000 | 1.00 | 100 1000 | 1.32 | 110 1000 | 1.64 |

| 000 1001 | 0.69 | 010 1001 | 1.01 | 100 1001 | 1.33 | 110 1001 | 1.65 |

| 000 1010 | 0.70 | 010 1010 | 1.02 | 100 1010 | 1.34 | 110 1010 | 1.66 |

| 000 1011 | 0.71 | 010 1011 | 1.03 | 100 1011 | 1.35 | 110 1011 | 1.67 |

| 000 1100 | 0.72 | 010 1100 | 1.04 | 100 1100 | 1.36 | 110 1100 | 1.68 |

| 000 1101 | 0.73 | 010 1101 | 1.05 | 100 1101 | 1.37 | 110 1101 | 1.69 |

| 000 1110 | 0.74 | 010 1110 | 1.06 | 100 1110 | 1.38 | 110 1110 | 1.70 |

| 000 1111 | 0.75 | 010 1111 | 1.07 | 100 1111 | 1.39 | 110 1111 | 1.71 |

| 001 0000 | 0.76 | 011 0000 | 1.08 | 101 0000 | 1.40 | 111 0000 | 1.72 |

| 001 0001 | 0.77 | 011 0001 | 1.09 | 101 0001 | 1.41 | 111 0001 | 1.73 |

| 001 0010 | 0.78 | 011 0010 | 1.10 | 101 0010 | 1.42 | 111 0010 | 1.74 |

| 001 0011 | 0.79 | 011 0011 | 1.11 | 101 0011 | 1.43 | 111 0011 | 1.75 |

| 001 0100 | 0.80 | 011 0100 | 1.12 | 101 0100 | 1.44 | 111 0100 | 1.76 |

| 001 0101 | 0.81 | 011 0101 | 1.13 | 101 0101 | 1.45 | 111 0101 | 1.77 |

| 001 0110 | 0.82 | 011 0110 | 1.14 | 101 0110 | 1.46 | 111 0110 | 1.78 |

| 001 0111 | 0.83 | 011 0111 | 1.15 | 101 0111 | 1.47 | 111 0111 | 1.79 |

| 001 1000 | 0.84 | 011 1000 | 1.16 | 101 1000 | 1.48 | 111 1000 | 1.80 |

| 001 1001 | 0.85 | 011 1001 | 1.17 | 101 1001 | 1.49 | 111 1001 | 1.81 |

| 001 1010 | 0.86 | 011 1010 | 1.18 | 101 1010 | 1.50 | 111 1010 | 1.82 |

| 001 1011 | 0.87 | 011 1011 | 1.19 | 101 1011 | 1.51 | 111 1011 | 1.83 |

| 001 1100 | 0.88 | 011 1100 | 1.20 | 101 1100 | 1.52 | 111 1100 | 1.84 |

| 001 1101 | 0.89 | 011 1101 | 1.21 | 101 1101 | 1.53 | 111 1101 | 1.85 |

| 001 1110 | 0.90 | 011 1110 | 1.22 | 101 1110 | 1.54 | 111 1110 | 1.86 |

| 001 1111 | 0.91 | 011 1111 | 1.23 | 101 1111 | 1.55 | 111 1111 | 1.87 |

# 2. Reg01 SysCntIreg1

| NAME      | BITS   | DEFAULT | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |        |           |

|-----------|--------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------|-----------|

| EN        | D[7]   | 1       | $I^2C$ controlled turn-on or turn-off the part. When external EN pin is low, the converter is off and $I^2C$ is also shutdown. When EN pin is high, the EN bit will take over. The default EN bit is "1".                                                                                                                                                                                                                                                                                          |           |        |           |

| GO_BIT    | D[6]   | 0       | Switch bit of I <sup>2</sup> C writing authority for output reference command only.<br>Set GO_BIT="1" to enable the I <sup>2</sup> C authority of writing output reference.<br>When the command is finished, GO_BIT will auto reset to "0" to prevent<br>false operation of VOUT scaling. If reference adjust is within 50mV,<br>GO_BIT won't be auto reset to "0". In this case need manually set<br>GO_BIT to "0". Suggest writing GO_BIT="1" first, then write the output<br>reference voltage. |           |        |           |

|           |        |         | D[5:3]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | SLEW RATE | D[5:3] | SLEW RATE |

|           |        |         | 000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 64 mV/uS  | 100    | 4 mV/uS   |

| Slew Rate | D[5:3] | 100     | 001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 32 mV/uS  | 101    | 2 mV/uS   |

|           |        |         | 010                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 16 mV/uS  | 110    | 1 mV/uS   |

|           |        |         | 011                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8 mV/uS   | 111    | 0.5 mV/uS |

|           |        |         | D[2:1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Fs        |        |           |

| Owitabiaa | D[2:1] | 00      | 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 500kHz    |        |           |

| Switching |        |         | 01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 750KHz    |        |           |

| Frequency |        |         | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1MHz      |        |           |

|           |        |         | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1.5MHz    |        |           |

| Mode      | D0     | 1       | A "0" enables PFM mode, a high disables PFM mode. Default in force CCM.                                                                                                                                                                                                                                                                                                                                                                                                                            |           |        |           |

# 3. Reg02 ID1

| NAME              | BITS   | DESCRIPTION |

|-------------------|--------|-------------|

| Vendor ID         | D[7:4] | 1000        |

| IC Revision<br>ID | D[3:0] | IC Revision |

### 4. Reg03 Status

| NAME     | BITS   | DESCRIPTION                                                                                                                                                                                                                                                                                                                       |  |

|----------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Reserved | D[7:5] | Reserved for future use. Always set at 0                                                                                                                                                                                                                                                                                          |  |

| VID_OK   | D[4]   | I <sup>2</sup> C controlled voltage adjustment is done. Internal circuit compares DAC output with<br>"VOUT" pin voltage, if "VOUT" is in the 90%-110% range of DAC output, VID_OK bit is<br>high which means the voltage scaling is finished. Otherwise, VID_OK="0".<br>VID_OK compares DAC with VOUT/FB. UV 90%+-3%, OV 110%+-3% |  |

| OC       | D[3]   | Output over current indication. When bit is high, IC is in hiccup mode.                                                                                                                                                                                                                                                           |  |

| OTEW     | D[2]   | Die temperature early warning bit. When the bit is high, the die temperature is higher than 120°C.                                                                                                                                                                                                                                |  |

| OT       | D[1]   | Over temperature indication. When bit is high the IC is in thermal shutdown                                                                                                                                                                                                                                                       |  |

| PG       | D[0]   | Output power good indication. When bit is high the VOUT power is good now. It means the VOUT is higher than 90% of designed regulation voltage. See details in "Power Good Indicator" Section.                                                                                                                                    |  |

# **APPLICATION INFORMATION**

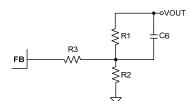

# Setting the Output Voltage in FB control Loop

Reference voltage and external resistor divider and can set the output voltage through FB. The feedback resistor R1 and R3 also sets the feedback loop bandwidth with the internal compensation capacitor. Choose R1 value firstly, R2 is then given by <sup>(10)</sup>:

$$R2 = \frac{R1}{\frac{V_{OUT}}{V_{REF}} - 1}$$

Notes:

10) VREF is 0.6V when Power up or EN on. After MP8868 is enabled, VREF can be programmed through  $I^2C$ . Set V\_BOOT=1 to enable FB control loop.

The T-type network (as shown in Figure 10) is highly recommended.

Figure 9: T-Type Network

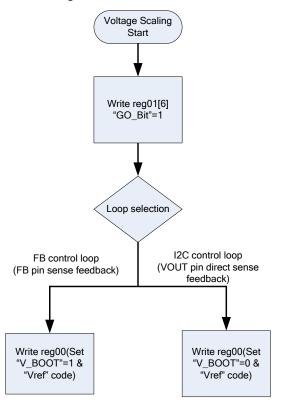

Table 2: Resistor Selection for Common Output Voltages with Default 0.6V VREF<sup>(11)</sup>

| Voltages with Default 0.6V VREF |              |              |              |            |           |

|---------------------------------|--------------|--------------|--------------|------------|-----------|

| V <sub>out</sub><br>(V)         | R1<br>(kΩ)   | R2<br>(kΩ)   | R3<br>(kΩ)   | C6<br>(pF) | L<br>(µH) |

| 0.9                             | 80.6<br>(1%) | 162<br>(1%)  | 51<br>(1%)   | 22         | 1.5       |

| 1.0                             | 80.6<br>(1%) | 120<br>(1%)  | 51<br>(1%)   | 22         | 1.5       |

| 1.2                             | 80.6<br>(1%) | 80.6<br>(1%) | 40.2<br>(1%) | 22         | 1.5       |

| 2.5                             | 60.4<br>(1%) | 19.1<br>(1%) | 30<br>(1%)   | 22         | 2.2       |

| 3.3                             | 60.4<br>(1%) | 13.3<br>(1%) | 20<br>(1%)   | 33         | 3.3       |

| 5                               | 60.4<br>(1%) | 8.25<br>(1%) | 20<br>(1%)   | 33         | 3.3       |

#### Note:

The recommended parameters is basing on 12V input voltage and 22µFx4 output capacitor, different input voltage and output capacitor value may affect the selection of R1, R2, R3, C6. For other components' parameters, please refer to TYPICAL APPLICATION CIRCUITS on page 26.

#### Setting the Output Voltage in I<sup>2</sup>C control Loop

Besides setting the output voltage through FB loop, I<sup>2</sup>C loop also can set the output voltage through VOUT pin by setting V\_BOOT=0. In this case, output voltage is the set reference voltage. Please refer to Table 1 for more details about output voltage setting.

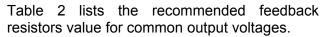

#### **Output Voltage Dynamic Scale**

To dynamic scale the output voltage during MP8868 normal operating, it suggests following below two steps and referring to the Figure 10:

Step1: Write the GO\_Bit (reg01[6]) to "1";

Step2: Write reg00 to select the feedback loop by setting V\_BOOT(reg00[7]) and set reference voltage by Output Reference (reg00[0:6]) simultaneously. If reference adjust is within 50mV, GO\_BIT won't be auto reset to "0", in this case it needs manually set GO\_BIT to "0".

Repeat above two steps if need dynamic scale to other voltage.

#### Figure 10: Output Voltage Dynamic Scale Flow Chart

#### Selecting the Inductor

Use a  $0.47\mu$ H-to- $10\mu$ H inductor with a DC current rating of at least 25% percent higher than the maximum load current for most applications. For highest efficiency, use an inductor with a DC resistance less than  $15m\Omega$ . For most designs, the inductance value can be derived from the following equation.

$$L_{1} = \frac{V_{\text{OUT}} \times (V_{\text{IN}} - V_{\text{OUT}})}{V_{\text{IN}} \times \Delta I_{\text{L}} \times f_{\text{OSC}}}$$

Where  $\Delta IL$  is the inductor ripple current.

Choose the inductor ripple current to be approximately 30% of the maximum load current. The maximum inductor peak current is:

$$I_{L(MAX)} = I_{LOAD} + \frac{\Delta I_{L}}{2}$$

Use a larger inductor for improved efficiency under light-load conditions—below 100mA.

#### Selecting the Input Capacitor

The input current to the step-down converter is discontinuous, therefore requires a capacitor is to supply the AC current to the step-down converter while maintaining the DC input voltage. Use low ESR capacitors for the best performance. Use ceramic capacitors with X5R or X7R dielectrics for best results because of their low ESR and small temperature coefficients. For most applications, use two piece  $22\mu$ F capacitors.

Since C1 absorbs the input switching current, it requires an adequate ripple current rating. The RMS current in the input capacitor can be estimated by:

$$\mathbf{I_{C1}} = \mathbf{I_{LOAD}} \times \sqrt{\frac{V_{OUT}}{V_{IN}}} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$$

The worse case condition occurs at VIN = 2VOUT, where:

$$I_{C1} = \frac{I_{LOAD}}{2}$$

For simplification, choose an input capacitor with an RMS current rating greater than half of the maximum load current. The input capacitor can be electrolytic, tantalum or ceramic. When using electrolytic or tantalum capacitors, add a small, high quality ceramic capacitor (e.g.  $0.1\mu$ F) placed as close to the IC as possible. When using ceramic capacitors, make sure that they have enough capacitance to provide sufficient charge to prevent excessive voltage ripple at input. The input voltage ripple caused by capacitance can be estimated by:

$$\Delta V_{\text{IN}} = \frac{I_{\text{LOAD}}}{f_{\text{S}} \times C1} \times \frac{V_{\text{OUT}}}{V_{\text{IN}}} \times \left(1 - \frac{V_{\text{OUT}}}{V_{\text{IN}}}\right)$$

Selecting the Output Capacitor

The output capacitor (C2) maintains the DC output voltage. Use ceramic, tantalum, or low-ESR electrolytic capacitors. For best results, use low ESR capacitors to keep the output voltage ripple low. The output voltage ripple can be estimated by:

$$\Delta V_{\text{OUT}} = \frac{V_{\text{OUT}}}{f_{\text{S}} \times L_{1}} \times \left(1 - \frac{V_{\text{OUT}}}{V_{\text{IN}}}\right) \times \left(R_{\text{ESR}} + \frac{1}{8 \times f_{\text{S}} \times C2}\right)$$

Where  $L_1$  is the inductor value and  $R_{\text{ESR}}$  is the equivalent series resistance (ESR) value of the output capacitor.

For ceramic capacitors, the capacitance dominates the impedance at the switching frequency, and the capacitance causes the majority of the output voltage ripple. For simplification, the output voltage ripple can be estimated by:

$$\Delta V_{\text{out}} = \frac{V_{\text{out}}}{8 \times f_{\text{s}}^{2} \times L_{1} \times C2} \times \left(1 - \frac{V_{\text{out}}}{V_{\text{IN}}}\right)$$

For tantalum or electrolytic capacitors, the ESR dominates the impedance at the switching frequency. For simplification, the output ripple can be approximated to:

$$\Delta V_{\text{out}} = \frac{V_{\text{out}}}{f_{\text{s}} \times L_{1}} \times \left(1 - \frac{V_{\text{out}}}{V_{\text{IN}}}\right) \times R_{\text{esr}}$$

The characteristics of the output capacitor also affect the stability of the regulation system. The MP8868 can be optimized for a wide range of capacitance and ESR values.

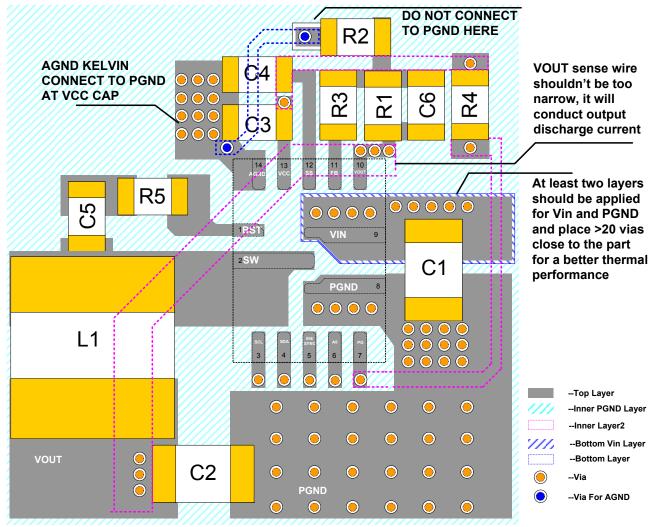

#### PC Board Layout<sup>(12)</sup>

PCB layout is very important for stable operation. Follow these guidelines for best results.

- 1. The high current paths (PGND, VIN, and SW) should be placed very close to the device with short, direct and wide traces.

- 2. Keep the IN and GND pads connected with large copper and use at least two layers for IN and GND trace to achieve better thermal performance. Also, add several Vias close to the IN and GND pads to help on thermal dissipation.

- 3. Put the input capacitors as close to the VIN and GND pins as possible.

- 4. Put the decoupling capacitor as close to the VCC and GND pins as possible.

- 5. The external feedback resistors should be placed next to the FB pin. Make sure that there is no via on the FB trace.

- 6. Keep the switching node SW short and away from the feedback network.

- 7. Keep the BST voltage path (BST, C5, and SW) as short as possible.

- 8. Four-layer layout is strongly recommended to achieve better thermal performance.

#### Notes:

12) The recommended layout is based on the Figure 13 Typical Application circuit in page26.

Figure 11: Recommend Layout

#### **Design Example**

Below is a design example following the application guidelines for the specifications:

#### Table 3 Design Example

| V <sub>IN</sub>  | 12V |

|------------------|-----|

| V <sub>OUT</sub> | 1V  |

| lo               | 10A |

The detailed application schematics are shown in Figure 13. The typical performance and circuit waveforms have been shown in the Typical Performance Characteristics section. For more device applications, please refer to the related Evaluation Board Datasheets.

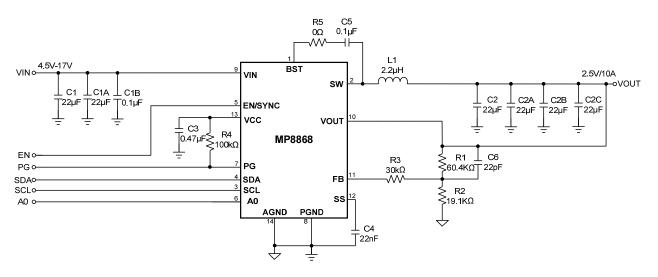

# **TYPICAL APPLICATION CIRCUITS** <sup>(13)</sup>

#### Figure 13: V<sub>IN</sub>=4.5-17V, V<sub>OUT</sub>=1V, I<sub>OUT</sub>=10A

#### Notes:

13) All circuits are basing on 0.6V default reference voltage.

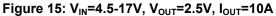

Figure 16: V<sub>IN</sub>=6-17V, V<sub>OUT</sub>=3.3V, I<sub>OUT</sub>=10A<sup>(14)</sup>

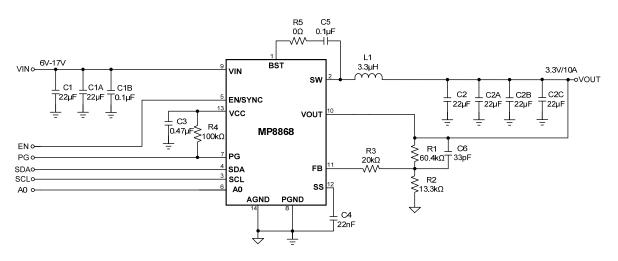

Figure 17: V<sub>IN</sub>=8-17V, V<sub>OUT</sub>=5V, I<sub>OUT</sub>=10A<sup>(14)</sup>

#### Notes:

14) Basing on Evaluation Board test result at 25°C ambient temperature, lower input voltage will trigger over temperature protection with full load.

# **PACKAGE INFORMATION**

TOP VIEW

BOTTOM VIEW

#### RECOMMENDED LAND PATTERN

#### <u>NOTE:</u>

ALL DIMENSIONS ARE IN MILLIMETERS.

EXPOSED PADDLE SIZE DOES NOT INCLUDE MOLD FLASH.

LEAD COPLANARITY SHALL BE 0.10 MILLIME MAX.

JEDEC REFERENCE IS MO-220.

DRAWING IS NOT TO SCALE.

**NOTICE:** The information in this document is subject to change without notice. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.