## **MP24830** 4.5V – 90V, Programmable Frequency White LED Driver

The Future of Analog IC Technology

## DESCRIPTION

The MP24830 is a 90V white LED driver suitable for either step-down or inverting step-up/down applications. It supports a wide input range with excellent load and line regulation. Its programmable current limit provides customized applications with a wide power range. Current mode operation provides a fast transient response and eases loop stabilization. Fault condition protection includes thermal shutdown, cycle-by-cycle peak-current limiting, open-string protection, and output short-circuit protection.

The MP24830 incorporates both DC and PWM dimming onto a single control pin. The separate input reference ground pin allows for direct enable and/or dimming control for a positive-tonegative power conversion.

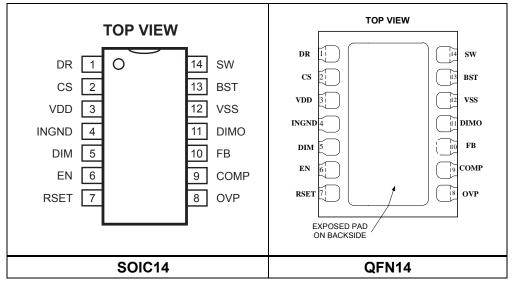

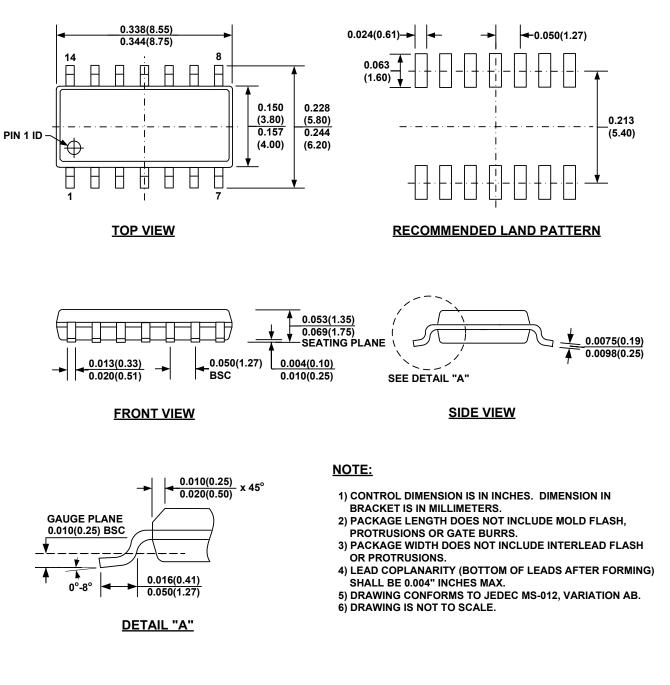

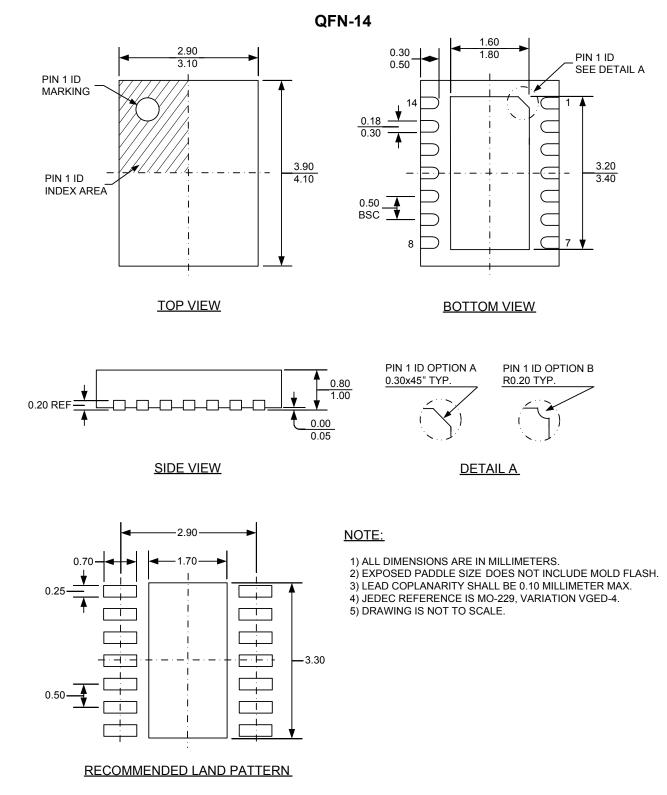

The MP24830 requires a minimal number of readily-available external components. It is available in 14-pin SOIC and QFN packages.

## FEATURES

- Programmable Maximum Output Current •

- Unique Step-Up/Down Operation (Buck-Boost Mode)

- Wide 4.5V-to-90V Operating Input Range • for Step-Down Applications (Buck Mode)

- Adjustable Switching Frequency

- Analog and PWM Dimming

- 0.2V Reference Voltage •

- 10uA Shutdown Mode •

- No Minimum LED Quantity Required

- Stable with Low ESR Output Ceramic • Capacitors

- Cycle-by-Cycle Over-Current Protection •

- **Thermal Shutdown Protection**

- **Open-String Protection** •

- **Output Short-Circuit Protection** •

- Available in 14-Pin SOIC and QFN Packages

## APPLICATIONS

- General LED Illumination

- Automotive LED Lighting

- LCD Backlight

All MPS parts are lead-free, halogen free, and adhere to the RoHS directive. For MPS green status, please visit MPS website under Quality Assurance. "MPS" and "The Future of Analog IC Technology" are Registered Trademarks of Monolithic Power Systems, Inc.

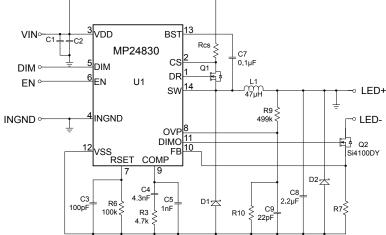

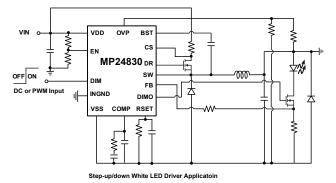

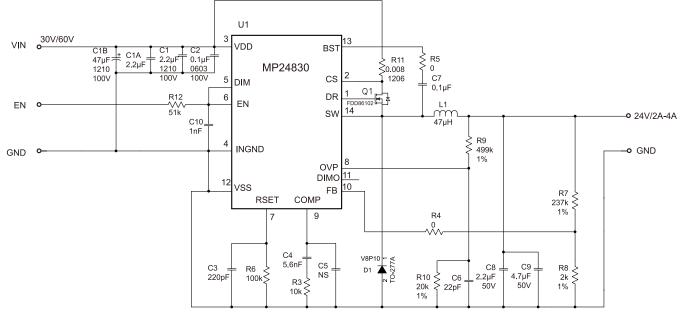

## **TYPICAL APPLICATION**

### **ORDERING INFORMATION**

| Part Number | Package | Top Marking |

|-------------|---------|-------------|

| MP24830HS*  | SOIC-14 | MP24830     |

| MP24830HL** | QFN-14  | 24830       |

\* For Tape & Reel, add suffix –Z (e.g. MP24830HS–Z); For RoHS Compliant Packaging, add suffix –LF (e.g. MP24830HS–LF–Z)

\*\* For Tape & Reel, add suffix –Z (e.g. MP24830HL–Z); For RoHS Compliant Packaging, add suffix –LF (e.g. MP24830HL–LF–Z)

## PACKAGE REFERENCE

## ABSOLUTE MAXIMUM RATINGS (1)

| Supply Voltage $V_{DD} - V_{SS}$ , $V_{CS} - V_{SS}$ 90V                           |   |

|------------------------------------------------------------------------------------|---|

| $V_{\text{SW}} - V_{\text{SS}}$ 0.3V to $V_{\text{IN}}$ + 0.3V                     |   |

| $V_{BST}, V_{DR}$ $V_{SW}$ + 6V                                                    | ' |

| $V_{\text{EN}} - V_{\text{INGND}},  V_{\text{Dim}} - V_{\text{INGND}}$ 0.3V to +6V | ' |

| $V_{\text{INGND}} - V_{\text{SS}}$ 0.3V to 90V                                     | ' |

| Other pins – $V_{SS}$ 0.3V to +6V                                                  | ' |

| Continuous Power Dissipation $(T_A = +25^{\circ}C)^{(2)}$                          |   |

| SOIC-14                                                                            |   |

| QFN-142.6W                                                                         |   |

| Junction Temperature 150°C                                                         |   |

| Lead Temperature                                                                   |   |

| Storage Temperature65°C to +150°C                                                  |   |

#### Recommended Operating Conditions <sup>(3)</sup>

## **Thermal Resistance** <sup>(4)</sup> $\theta_{JA}$ $\theta_{JC}$

| SOIC-14 |           |

|---------|-----------|

| QFN-14  | 49 10°C/W |

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature T<sub>J</sub> (MAX), the junction-toambient thermal resistance  $\theta_{JA}$ , and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub> (MAX) = (T<sub>J</sub> (MAX)-T<sub>A</sub>)/ $\theta_{JA}$ . Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- 3) The device function is not guaranteed outside of the recommended operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB.

## **ELECTRICAL CHARACTERISTICES**

$V_{IN}$  = 12V,  $T_J$  = +25°C, all voltages with respect to  $V_{SS}$ , unless otherwise noted.

| Parameters                                      | Symbol                 | Condition                                           | Min   | Тур  | Мах   | Units |

|-------------------------------------------------|------------------------|-----------------------------------------------------|-------|------|-------|-------|

| Feedback Voltage                                | V <sub>FB</sub>        | $4.5V \le V_{IN} \le 90V$                           | 0.192 | 0.2  | 0.208 | V     |

| Feedback Current                                | I <sub>FB</sub>        | V <sub>FB</sub> = 0.22V                             | -50   |      | 50    | nA    |

| Under Voltage Lockout Threshold Rising          | V <sub>UVLOTH</sub>    |                                                     | 3.7   | 4.1  | 4.4   | V     |

| Under Voltage Lockout Threshold Hysteresis      | V <sub>UVLOHY</sub>    |                                                     |       | 160  |       | mV    |

| Operation Current (Quiescent)                   | Ι <sub>Q</sub>         | V <sub>EN</sub> = 2V, V <sub>FB</sub> = 0.25V       |       | 0.8  | 1.1   | mA    |

| Supply Current (Quiescent) at EN Off            | I <sub>OFF</sub>       | V <sub>EN</sub> =0V                                 |       | 10   | 23    | μA    |

| Gate Driver Pull-Up Impedance                   | R <sub>PULL UP</sub>   |                                                     |       | 25   |       | Ω     |

| Gate Driver Pull-Down Impedance                 | R <sub>PULL Down</sub> |                                                     |       | 7    |       | Ω     |

| Gate Driver Output-High to SW                   | V <sub>OH-SW</sub>     | I <sub>DR</sub> =10mA                               | 5.6   | 5.8  |       | V     |

| Gate Driver Output-Low to SW                    | V <sub>OL-SW</sub>     | I <sub>DR</sub> =10mA                               |       | 0.1  | 0.3   | V     |

| DIMO Source Current                             | IDIMOSC                |                                                     |       | 0.05 |       | А     |

| DIMO Sink Current                               | I <sub>DIMOSK</sub>    |                                                     |       | 0.05 |       | А     |

| DIMO Output High                                | V <sub>DIMOH</sub>     | I <sub>DR</sub> =10mA                               | 4.6   | 5    |       | V     |

| DIMO Output Low                                 | V <sub>DIMOL</sub>     | I <sub>DR</sub> =10mA                               |       | 0.4  | 0.5   | V     |

| Oscillator Frequency                            | f <sub>SW</sub>        | $V_{FB} = 0.15V,$<br>$R_{SET} = 100k\Omega$         | 145   | 215  | 265   | kHz   |

| Min. Oscillator Frequency                       | f <sub>SWMIN</sub>     | V <sub>FB</sub> = 0.15V,<br>R <sub>SET</sub> =380kΩ | 30    | 50   | 75    | kHz   |

| Max. Oscillator Frequency                       | f <sub>SWMAX</sub>     | V <sub>FB</sub> = 0.15V, R <sub>SET</sub> open      | 245   | 365  | 465   | kHz   |

| Foldback Frequency                              | f <sub>SWFB</sub>      | $V_{FB} = 0V, V_{OVP}=0V, R_{SET}=100k\Omega$       |       | 30   |       | kHz   |

| GM of Error Amplifier                           | GM                     |                                                     |       | 80   |       | μs    |

| Error Amplifier Output Current                  | I <sub>Oamp</sub>      |                                                     |       | 40   |       | μA    |

| Current Sensing Gain                            | G <sub>CS</sub>        |                                                     |       | 20   |       |       |

| High-Side Current Limit Threshold               | V <sub>CLTH</sub>      |                                                     |       | 45   |       | mV    |

| Min. Off-Time                                   | t <sub>OFFMIN</sub>    | V <sub>FB</sub> = 0.19V,<br>R <sub>SET</sub> =100kΩ |       | 280  |       | ns    |

| Min. On-Time <sup>(5)</sup>                     | t <sub>on</sub>        |                                                     |       | 100  |       | ns    |

| EN Input Current                                | I <sub>ENIN</sub>      | V <sub>EN</sub> = 3.3V                              |       | 3.7  |       | μA    |

| EN OFF Threshold (w/Respect to INGND)           | V <sub>ENOFFTH</sub>   | V <sub>EN</sub> Falling                             | 0.4   |      |       | V     |

| EN ON Threshold (w/Respect to INGND)            | V <sub>ENONTH</sub>    | V <sub>EN</sub> Rising                              |       |      | 1.4   | V     |

| Min. DIM Threshold                              | V <sub>DIMTHL</sub>    | V <sub>FB</sub> = 0.2V                              | 0.6   | 0.7  | 0.8   | V     |

| Max. DIM Threshold                              | V <sub>DIMTHH</sub>    | V <sub>FB</sub> = 0.2V                              | 1.55  | 1.75 | 1.95  | V     |

| LED-Short Threshold for Immediate Latch-<br>Off |                        |                                                     |       | 600  |       | mV    |

| LED Short Delay for Latch-Off                   |                        |                                                     |       | 450  |       | μs    |

| LED Short Threshold                             |                        |                                                     |       | 300  |       | mV    |

| Thermal Shutdown <sup>(5)</sup>                 | T <sub>TSHD</sub>      |                                                     |       | 160  |       | °C    |

| Open LED OV Threshold                           | V <sub>OVPTH</sub>     |                                                     | 1.1   | 1.2  | 1.3   | V     |

| Open LED OV Hysteresis                          | V <sub>OVPHY</sub>     |                                                     |       | 50   |       | mV    |

Notes:

5) Guaranteed by design.

### **PIN FUNCTIONS**

| SOIC14 | Name  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | DR    | Driver Output. Connect it to the high-side MOSFET gate.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2      | CS    | High-Side Current Sense. For over-current protection and current-mode control.                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3      | VDD   | Supply Voltage. Operates from a 4.5V-to-85V unregulated input (with respect to VSS). Needs C1 to prevent large input voltage spikes.                                                                                                                                                                                                                                                                                                                                                       |

| 4      | INGND | Input Ground Reference. Reference for the EN/DIM signal.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5      | DIM   | Dimming Command Input. Selects for DC or PWM dimming. When the DIM pin voltage (with respect to INGND) rises from 0.6V to 1.95V, the LED current changes from 0% to 100% of the maximum LED current. For PWM dimming, apply a 100Hz-to-2kHz square wave with an amplitude greater than 2V. For combined analog and PWM dimming, apply a 100Hz-to-2kHz square wave signal with amplitude from 0.6V to 1.95V.                                                                                |

| 6      | EN    | Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 7      | RSET  | Frequency Set. Connect a resistor to VSS to set the switching frequency, and a 1nF capacitor to VSS to bypass the noise. Leaving this pin open for the 350kHz default operating frequency.                                                                                                                                                                                                                                                                                                 |

| 8      | OVP   | Over-Voltage Protection. Use a voltage divider to program OVP threshold. When the OVP pin voltage reaches the 1.2V shutdown threshold, the switch turns off and recovers when the OVP voltage decreases sufficiently. When the OVP pin voltage (with respect to VSS) falls below 0.4V and the FB pin voltage falls below 0.1V, the chip interprets this as a short circuit and the operating frequency will fold back. Program the OVP pin voltage from 0.4V to 1.2V for normal operation. |

| 9      | COMP  | Error Amplifier Output. Connect a 1nF or larger capacitor on COMP and an RC network from FB to COMP to improve the stability and to provide soft-start and PWM dimming.                                                                                                                                                                                                                                                                                                                    |

| 10     | FB    | LED Current Feedback Input. A current-sensing resistor between FB and VSS provides circuit feedback. The regulation voltage is 0.2V. Short-circuit protection triggers If the FB voltage exceeds 300mV for 450µs or the FB voltage exceeds 600mV.                                                                                                                                                                                                                                          |

| 11     | DIMO  | DIM Output. Provides for accurate PWM diming control following DIM logic. Connect to the gate of the external dimming MOSFET. Leave floating if dimming accuracy is not a concern.                                                                                                                                                                                                                                                                                                         |

| 12     | VSS   | Power Return. Connect to the circuit's point of lowest potential, which is typically the anode of the Schottky rectifier. Acts as the voltage reference for the regulated output voltage, and layout requires extra consideration. Place this node outside of the D1-to-C1 ground path to prevent switching current spikes from inducing voltage noise. Connect the exposed pad to this pin.                                                                                               |

| 13     | BST   | Bootstrap. Connect a capacitor between the SW and BST pins to form a floating supply across the power switch driver. Use a 100nF or larger ceramic capacitor to provide sufficient energy to drive the power switch's gate above the supply voltage.                                                                                                                                                                                                                                       |

| 14     | SW    | Switch. Connect to the source of the external MOSFET                                                                                                                                                                                                                                                                                                                                                                                                                                       |

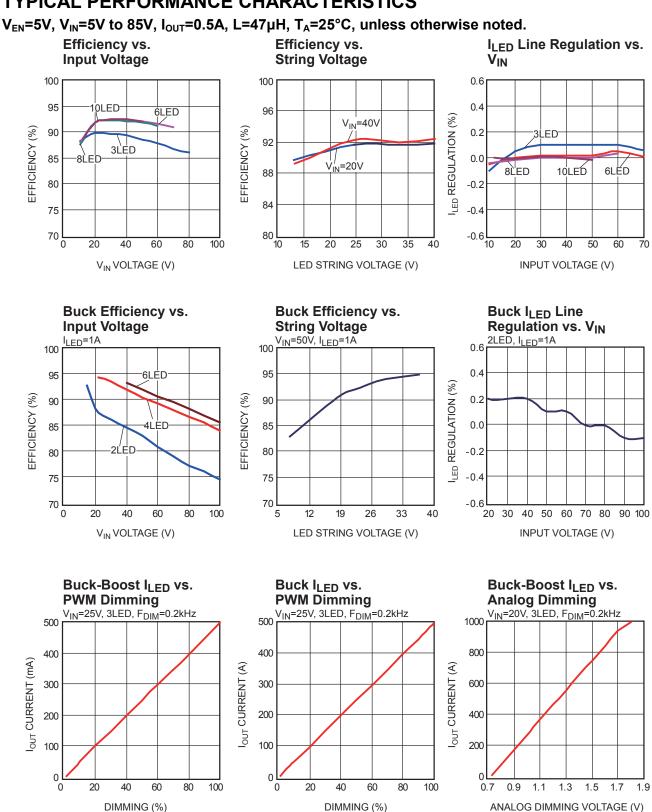

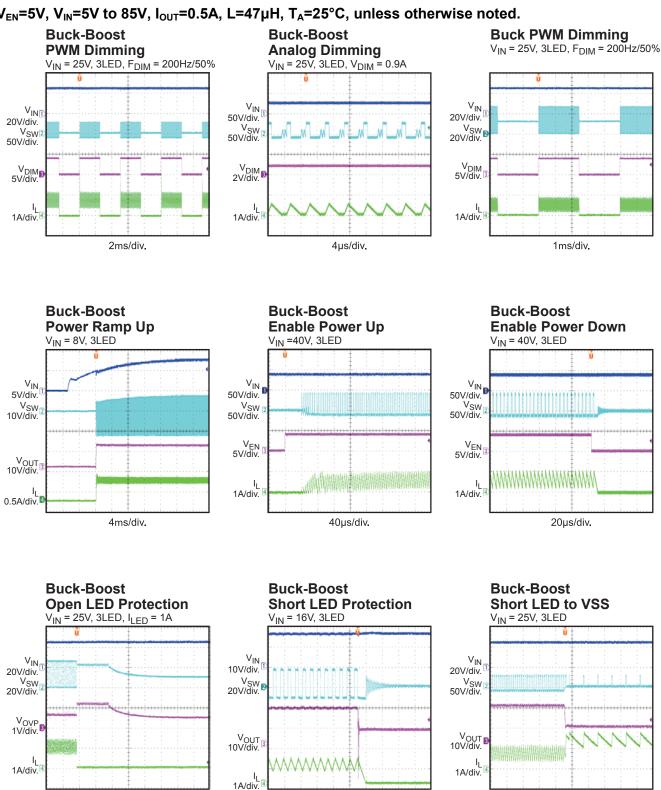

## TYPICAL PERFORMANCE CHARACTERISTICS

MP24830 Rev. 1.02 4/29/2015

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2015 MPS. All Rights Reserved.

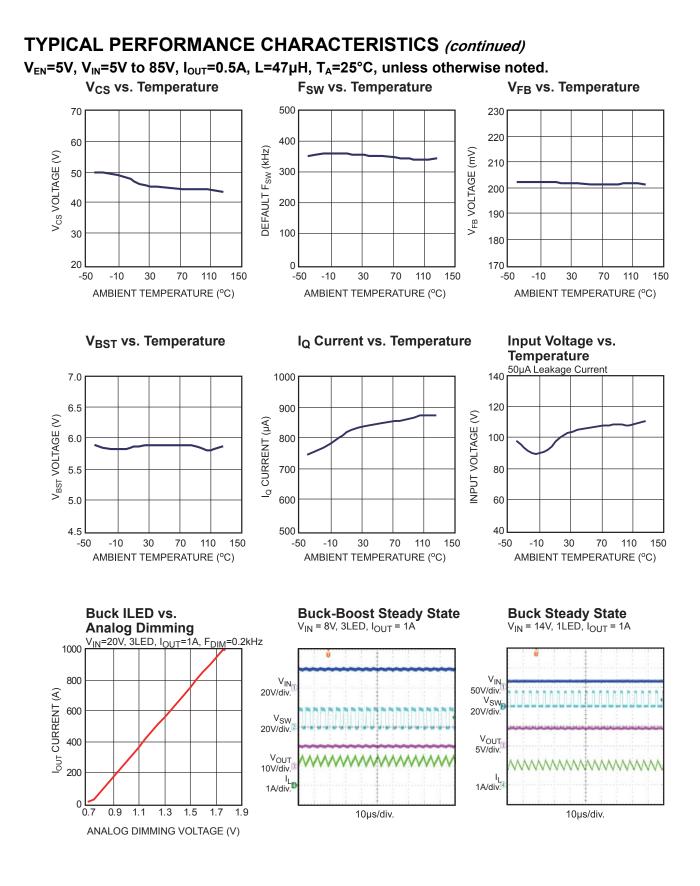

### **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

V<sub>EN</sub>=5V, V<sub>IN</sub>=5V to 85V, I<sub>OUT</sub>=0.5A, L=47µH, T<sub>A</sub>=25°C, unless otherwise noted.

MP24830 Rev. 1.02 4/29/2015

1s/div.

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2015 MPS. All Rights Reserved.

10µs/div.

40µs/div.

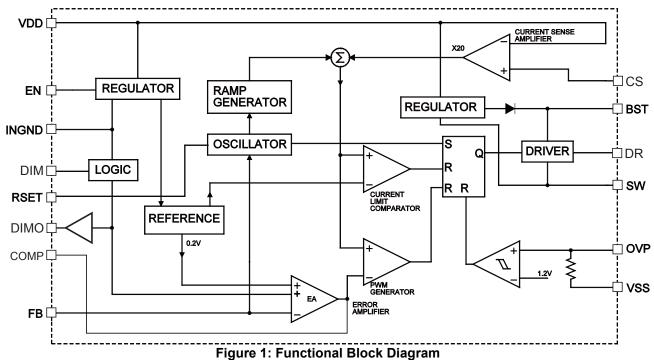

FUNCTIONAL BLOCK DIAGRAM

## **OPERATION**

The MP24830 is a current-mode regulator. The error amplifier (EA) output voltage is proportional to the peak inductor current.

At the beginning of a cycle, M1 is off. The EA output voltage exceeds the current sense amplifier output, and the current comparator's output is low. The rising edge of the CLK signal (its frequency equals the switching frequency) triggers the RS flip-flop. The driver turns on the external MOSFET, thus connecting the SW pin and inductor to the input supply.

The current-sense amplifier (CSA) senses the increasing inductor current. The PWM comparator compares the sum of the ramp generator and the CSA output against the output of the error amplifier. When the sum of the CSA output and the ramp generator signal exceeds the EA output voltage, the RS flip-flop resets and driver turns off the external MOSFET. The external Schottky rectifier diode (D1) conducts the inductor current.

If the sum of the CSA output and the ramp compensation signal does not exceed the EA output for a whole cycle, then the falling edge of the CLK resets the flip-flop.

The output of the EA integrates the voltage difference between the feedback and the 0.2V reference: A value of  $0.2V-V_{FB}$  increases the EA output voltage. Since the EA output voltage is proportional to the peak inductor current, increasing its voltage also increases the current delivered to the output.

#### **LED Open Protection**

If the LED is open, there is no voltage on the FB pin. The duty cycle increases until OVP-VSS reaches the shutdown threshold set by the external resistor divider. The top switch remains off until the voltage OVP-VSS drops below 1.2V.

#### **LED Short Protection**

If the FB voltage exceeds 600mV, the latches off immediately and DIMO goes low. If the FB voltage exceeds 300mV for 450µs, the IC latches off and DIMO is pulled low. The EN needs to reset to restart the IC.

#### **Dimming Control**

The MP24830 allows both DC and PWM dimming on the DIM pin. For analog dimming, a voltage range from 0.6V to 1.95V linearly sets the LED current from 0% to 100% of the maximum LED current. DIM voltages exceeding 2V results in the maximum LED current. For PWM dimming, use a square signal with an amplitude ( $V_{DIM} - V_{INGND}$ ) that exceeds 1.95V. For good dimming linearity, select a PWM frequency in range of 100Hz to 2kHz. For a higher dimming frequency or dimming ratio, use the DIMO pin to control an external dimming MOSFET. For combined analog and PWM dimming, apply a PWM signal with amplitude of 0.6V to 1.95V on the DIM pin.

#### **Output Short-Circuit Protection**

The MP24830 integrates output short-circuit protection (SCP) to foldback the operating frequency and decrease power consumption when the output is shorted to VSS. Such shorts cause the voltage on the OVP pin to drop below 0.4V, and the FB pin senses no voltage (<0.1V) as no current goes through the WLED.

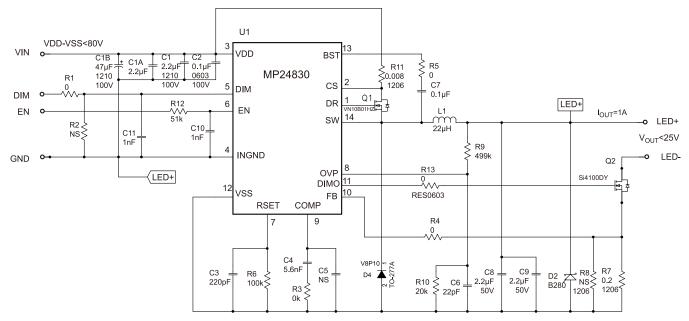

In buck-boost applications, when there is a possibility that LED+ short-circuits to VSS, add a diode from VSS to INGND to protect the IC, as shown in below in Figure 2.

Figure 2: Buck-Boost Application with Possible LED+ Short to VSS

## APPLICATION INFORMATION

The MP24830 can be used in buck mode and buck-boost mode applications.

#### Setting the LED Current

An external resistor R<sub>FB</sub> sets the maximum LED current as per the equation:

$$\mathsf{R}_{\mathsf{FB}} = \frac{0.2\mathsf{V}}{\mathsf{I}_{\mathsf{LED}}}$$

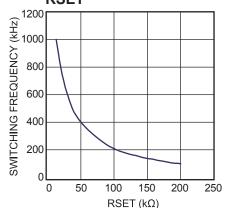

#### Setting the Switching Frequency

The switching frequency is set by an external resistor, R<sub>SET</sub>, connected from the RSET pin to VSS The relationship between the switching frequency and the programming resister is as per the following table and shown in Figure 3.

#### Table 1 R<sub>SET</sub> and f<sub>sw</sub> Relationship

| f <sub>sw</sub> (kHz) | R <sub>SET</sub> (kΩ) |

|-----------------------|-----------------------|

| 100                   | 200                   |

| 125                   | 165                   |

| 210                   | 100                   |

| 400                   | 50.4                  |

| 600                   | 30.3                  |

| 800                   | 19.9                  |

| 1000                  | 13.2                  |

| 350                   | Open                  |

#### Switching Frequency vs. RSET

Figure 3: Switching Frequency vs. R<sub>SET</sub> The MP24380 implements current mode control by sensing the inductor current through a current sensing resistor R<sub>CS</sub>, as calculated by:

$$\mathsf{R}_{\mathsf{CS}} = \frac{0.9 \times \mathsf{V}_{\mathsf{CL}}}{\mathsf{I}_{\mathsf{L}_{\mathsf{PK}}\mathsf{Max}}}$$

Where the  $V_{CL}$  is the current limit,  $V_{CL}$ =50mV, and IL PK Max is the maximum peak current in the inductor.

Calculate R<sub>cs</sub> using the minimum input voltage, the maximum output voltage and the maximum output current.

#### Setting the Over-Voltage Protection

The MP24380 detects output over-voltage via the OVP pin. The OVP pin monitors the output voltage through a voltage divider (R<sub>OVP1</sub> and  $R_{OVP2}$ ): When the OVP voltage exceeds 1.24V, the IC triggers OVP.

Select the resistor value ratio using the following equation:

$$\frac{R_{_{OVP1}}}{R_{_{OVP2}}} = \frac{V_{_{OUT\_OVP}}}{V_{_{th\_OVP}}} - 1$$

The OVP trip-point is set between 0.4V and 1.24V.

#### Setting the Compensation

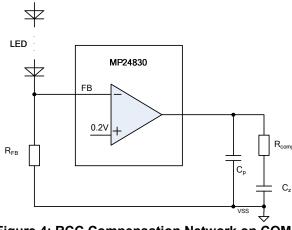

The MP24830 implements current-mode control to regulate the LED current feedback through the compensation network on the COMP pin. applications. For most use an RCC compensation network to ensure current accuracy and the system stability, as shown in Figure 4.

Its DC gain is:

$$DCGain\_EA = \frac{gm \times R_{_{FB}}}{C_{_{z}} + C_{_{p}}}$$

Where gm is error amplifier's transconductance of 80µA/V.

The zero of the compensation network is:

$$\mathbf{f}_{z_{-}\mathsf{EA}} = \frac{1}{2\pi \times \mathbf{R}_{\mathsf{COMP}} \times \mathbf{C}_{z}}$$

The pole of the compensation network is:

$$f_{p\_EA} = \frac{1}{2\pi \times R_{COMP} \times \frac{C_z \times C_p}{C_z + C_p}}$$

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2015 MPS. All Rights Reserved.

Figure 4: RCC Compensation Network on COMP Pin

# (1)Compensation network for Buck-boost application

The DC modulator gain of the buck-boost power stage (from the output current to the control voltage on COMP pin) is:

$$DCGain\_PS = \frac{\frac{V_{OUT} \times V_{IN}}{V_{OUT} + V_{IN}}}{20 \times R_{CS} \times (\frac{V_{OUT}}{R_{FB} + R_{LED}} + \frac{I_{OUT} * V_{OUT}}{V_{OUT} + V_{IN}}) \times (R_{FB} + R_{LED})}$$

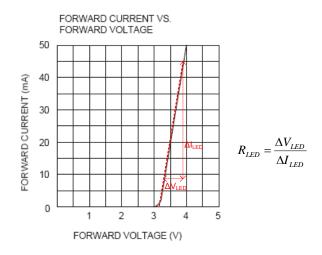

Where  $R_{CS}$  is the switch current sensing resistor on CS pin,  $R_{LED}$  is the equivalent dynamic resistance of the LED load, as shown in Figure 5.

**Figure 5: LED Dynamic Resistance Equivalent** The dominant low-frequency pole of the buckboost power stage is:

$$f_{P\_PS} = \frac{\frac{V_{\text{OUT}}}{R_{\text{FB}} + R_{\text{LED}}} + \frac{I_{\text{OUT}} * V_{\text{OUT}}}{V_{\text{OUT}} + V_{\text{IN}}}}{2\pi V_{\text{OUT}} \times C_{\text{OUT}}}$$

The right-half plane (RHP) zero of the buckboost power stage is:

$$f_{Z_{RHP}} = \frac{V_{IN}^{2}}{2\pi \times L \times I_{OUT} \times (V_{OUT} + V_{IN})}$$

Step 1: Select R<sub>COMP</sub>

Choose a crossing frequency,  $f_c$ , below  $1/3 \times f_{Z_RHP}$  to derive the compensation network as follow (assume  $C_Z >> C_p$ ):

$$R_{\text{COMP}} = \frac{f_{c}}{gm \times R_{\text{FB}} \times DCGain\_PS * f_{P\_PS}}$$

That is:

$$R_{\text{COMP}} = \frac{2\pi f_{c} \times C_{\text{OUT}} \times 20 \times R_{\text{CS}} \times (R_{\text{FB}} + R_{\text{LED}})(V_{\text{OUT}} + V_{\text{IN}})}{gm \times R_{\text{FB}} \times V_{\text{IN}}}$$

Use the maximum input voltage and minimum output voltage to calculate  $R_{COMP}$ .

Step 2: Select C<sub>Z</sub>

Set the zero of the compensation network to cancel the minimum pole of the power stage to get:

$$C_z = \frac{1}{2\pi \times f_{P\_PS} \times R_{COMP}}$$

Choose  $C_z$  with the maximum input voltage and maximum output voltage.

Step 3: Select C<sub>P</sub>

Set the pole of the compensation network to cancel the minimum RHP zero to get:

$$C_{p} \approx \frac{1}{2\pi \times f_{z_{-}RHP} \times R_{COMP}}$$

Choose  $C_{\mathsf{P}}$  with the minimum input voltage and maximum output voltage.

# (2)Compensation network for Buck application

The DC modulator gain of the buck power stage (from the output current to the control voltage) is:

DCGain\_Buck =

$$\frac{1}{20 \times R_{cs}}$$

The dominant, low frequency pole of the buck power stage is:

$$f_{P_Buck} = \frac{1}{2\pi \times (R_{FB} + R_{LED} + R_{ESR}) \times C_{OUT}}$$

The zero produced by the ESR of the output capacitor is:

$$f_{Z\_ESR} = \frac{1}{2\pi \times C_{OUT} * R_{ESR}}$$

Where  $R_{ESR}$  is the ESR of the output capacitor.

Step 1: Select R<sub>COMP</sub>

Choose a crossing frequency,  $f_C$ , below  $1/5 \times f_C$  to derive the compensation network as follows (assume  $C_Z >> C_P$ ):

$$R_{\text{COMP}-\text{Buck}} = \frac{f_{c}}{gm \times R_{\text{FB}} \times DCGain\_Buck * f_{p\_Buck}}$$

That is:

$$R_{\text{COMP}_Buck} = \frac{2\pi f_{c} \times C_{\text{OUT}} \times 20 \times R_{\text{CS}} \times (R_{\text{FB}} + R_{\text{LED}} + R_{\text{ESR}})}{gm \times R_{\text{FB}}}$$

Step 2: Select C<sub>Z</sub>

Set the zero of the compensation network to cancel the minimum pole of the Buck power stage to get:

$$C_{z\_Buck} = \frac{1}{2\pi \times f_{P\_Buck} \times R_{COMP\_Buck}}$$

Step 3: Select C<sub>P</sub>

Set the pole of the compensation network to cancel the ESR zero. If the ESR zero is too high, set this pole at around 3 to 5 times  $f_c$ :

$$C_{p} \approx max(\frac{1}{2\pi \times f_{z\_ESR} \times R_{COMP\_Buck}}, \frac{1}{2\pi \times 5f_{c} \times R_{COMP\_Buck}})$$

#### Selecting the Inductor

Select the inductor based on the input voltage, the output voltage, and the LED current. Select the inductor to make the circuit operate in continuous current mode (CCM). Select the inductor current rating to ensure that the inductor does not saturate and with consideration to power consumption based on the DC resistance.

(1) Selecting the Inductor for Buck-Boost Applications

For buck-boost applications, select the inductor based on the following equation:

$$L = \frac{V_{IN} \times V_{OUT}}{f_{SW} \times (V_{IN} + V_{OUT}) \times \Delta I_{L}}$$

Where  $\Delta I_{L}$  is the peak-to-peak inductor current ripple. Design  $\Delta I_{L}$  to be between 30% and 60% of the average current of the inductor, which is:

$$I_{L_{AVG}} = I_{LED} * (1 + \frac{V_{OUT}}{V_{IN}})$$

Select the inductor with a DC current rating that ensurew that the inductor does not saturated at the peak current of:

$$I_{L\_PK} = I_{L\_AVG} + 0.5 \Delta I_L$$

(2) Selecting the Inductor for Buck Applications

For buck applications, derive the inductance value from the following equation.

$$L = \frac{V_{OUT} \times (V_{IN} - V_{OUT})}{V_{IN} \times \Delta I_L \times f_{SW}}$$

Where  $\Delta I_{L}$  is the peak-to-peak inductor ripple current.

Choose the inductor ripple current to around 30% to 60% of the maximum load current. The maximum inductor peak current is calculated as:

$$I_{L(MAX)} = I_{LOAD} + \frac{\Delta I_{L}}{2}$$

#### Selecting the Input Capacitor

The input capacitor reduces the surge current drawn from the input supply and the switching noise from the device. For best results, use

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.

© 2015 MPS. All Rights Reserved.

MPS.

ceramic capacitors with X7R dielectrics with low ESR and small temperature coefficients.

Select a large-enough capacitor to limit input the voltage ripple,  $\Delta V_{IN}$ , to less than 5% to 10% of the DC value.

$$C_{\text{IN}} > \frac{I_{\text{L}_{\text{AVG}}} \times V_{\text{OUT}}}{f_{\text{SW}} \times \Delta V_{\text{IN}} \times (V_{\text{IN}} + V_{\text{OUT}})}$$

#### Selecting the Output Capacitor

The output capacitor limits the output voltage ripple,  $\Delta V_{OUT}$  (normally less than 1% to 5% of the DC value), and ensures feedback loop stability. Use an output capacitor with impedance at the switching frequency. Use ceramic capacitors with low ESR characteristics.

$$C_{\text{OUT}} > \frac{I_{\text{LED}} \times V_{\text{OUT}}}{f_{\text{SW}} \times \Delta V_{\text{OUT}} \times (V_{\text{IN}} + V_{\text{OUT}})}$$

#### **PC Board Layout**

Place the high-current paths (VSS, VDD and SW) very close to the device with short, direct, and wide traces. Place the input capacitor as close as possible to the VDD and VSS pins. Place the external feedback resistors next to the FB pin. Keep the switch node traces short and away from the feedback network.

Pay special attention is required to the switching frequency loop layout, which should be as small as possible.

For buck applications, the switching frequency loop is composed of the input capacitor, the power MOSFET and the Schottky diode. Place the Schottky diode close to the power MOSFET and the input capacitor.

For buck-boost or boost applications, the switching frequency loop is composed of the input capacitor, the power MOSFET, the Schottky diode and the output capacitor. Make this component loop as small as possible. For most applications, place the output capacitor close to the input capacitor and the power MOSFET.

## **TYPICAL APPLICATION CIRCUIT**

Figure 7: Step-down Constant Voltage Converter Application

## PACKAGE INFORMATION

SOIC-14

**NOTICE:** The information in this document is subject to change without notice. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.