MP2208 16V, 4A, 600kHz Synchronous Step-Down Converter

The Future of Analog IC Technology

## DESCRIPTION

The MP2208 is an internally compensated 600kHz fixed frequency PWM synchronous step-down regulator. With a 3V to 6V bias supply, MP2208 operates from a 3V to 16V input and generates an adjustable output voltage from 0.8V to  $0.9xV_{\rm IN}$  at up to 4A load current.

The MP2208 integrates a  $80m\Omega$  high-side switch and a  $80m\Omega$  synchronous rectifier for high efficiency without an external Schottky diode. With peak current mode control and internal compensation, it can be stabilized with ceramic capacitors and small inductors. Fault condition protection includes short-circuit protection, cycle-by-cycle current limiting and thermal shutdown.

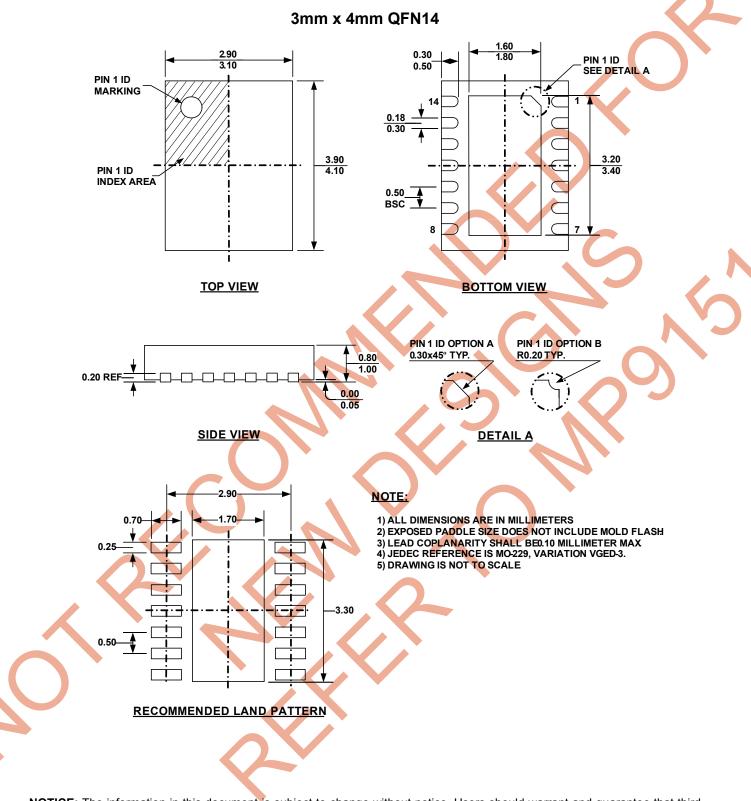

The MP2208 is available in small 3mmx4mm 14-lead QFN packages.

## FEATURES

- 4A Output Current

- Input Supply Range: 3V to 16V

- 80mΩ Internal Power MOSFET Switches

- Stable with Ceramic Output Capacitors

- High Efficiency

- 600kHz Fixed Switching Frequency

- Adjustable Output from 0.8V to 0.9xV<sub>IN</sub>

- Frequency Synchronization

- Power Good Pin

- Thermal Shutdown

- Cycle-by-Cycle Current Limiting

- Short Circuit Protection

- 3mmx4mm 14-lead QFN Package

## APPLICATIONS

- µP/ASIC/DSP/FPGA Core and I/O Supplies

- Printers and LCD TVs

- Network and Telecom Equipment

- Point of Load Regulators

"MPS" and "The Future of Analog IC Technology" are Trademarks of Monolithic Power Systems, Inc.

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2012 MPS. All Rights Reserved.

### **ORDERING INFORMATION**

| Part Number* | Package           | Top Marking | Free Air Temperature (Ta) |  |

|--------------|-------------------|-------------|---------------------------|--|

| MP2208DL     | QFN14 (3mm x 4mm) | 2208        | –40°C to +85°C            |  |

\* For Tape & Reel, add suffix –Z; (e.g. MP2208DL–Z);

For RoHS Compliant Packaging, add suffix –LF; (e.g. MP2208DL–LF–Z)

## PACKAGE REFERENCE

## ABSOLUTE MAXIMUM RATINGS (1)

| IN to GND                    | –0.3V to +18V                |

|------------------------------|------------------------------|

| SW to GND0                   | $0.3V$ to $V_{IN} + 0.3V$    |

| 2.5V to V <sub>IN</sub>      |                              |

| FB, EN/SYNC, VCC to GND      | –0.3V to +6.5V               |

| BS to SW                     | 0.3V to +6.5V                |

| Continuous Power Dissipation | $(T_A = +25^{\circ}C)^{(2)}$ |

|                              | 2.6W                         |

| Junction Temperature         | 150°C                        |

| Lead Temperature             | 260°C                        |

| Storage Temperature          | .–65°C to +150°C             |

|                              |                              |

| Recommended Operating Conditions <sup>(3)</sup> |                                |  |  |  |  |  |  |

|-------------------------------------------------|--------------------------------|--|--|--|--|--|--|

| Supply Voltage VIN                              |                                |  |  |  |  |  |  |

| Bias Voltage V <sub>cc</sub>                    |                                |  |  |  |  |  |  |

| Output Voltage Vout                             | 0.8V to 0.9 x V <sub>IN</sub>  |  |  |  |  |  |  |

| Max Operating Junct. Temp.                      | (T <sub>J</sub> ) +125°C       |  |  |  |  |  |  |

| EN/SYNC Voltage                                 | . No more than V <sub>cc</sub> |  |  |  |  |  |  |

|                                                 |                                |  |  |  |  |  |  |

## Thermal Resistance (4)

QFN14 (3mm x 4mm) ......48 ..... 11 ... °C/W

$\theta_{JA}$

$\theta_{JC}$

Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature T<sub>J</sub> (MAX), the junction-toambient thermal resistance  $\theta_{JA}$ , and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub> (MAX) = (T<sub>J</sub> (MAX)-T<sub>A</sub>)/ $\theta_{JA}$ . Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

The device is not guaranteed to function outside of its operating conditions.

Measured on JESD51-7, 4-layer PCB.

92 www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2012 MPS. All Rights Reserved.

## **ELECTRICAL CHARACTERISTICS**

$V_{IN}$  = 12V,  $V_{CC}$  =  $V_{EN}$  = 3.6V,  $T_A$  = +25°C, unless otherwise noted.

| $v_{\rm IN} = 12V, V_{\rm CC} = V_{\rm EN} = 3.6V, I_{\rm A}$ | = +25°C, unless otherwise noted.                                         |       |       |       |                  |   |

|---------------------------------------------------------------|--------------------------------------------------------------------------|-------|-------|-------|------------------|---|

| Parameters                                                    | Condition                                                                | Min   | Тур   | Max   | Units            |   |

| V <sub>CC</sub> Supply Current                                |                                                                          |       | 750   |       | μA               |   |

| V <sub>cc</sub> Shutdown Current                              | $V_{EN} = 0V, V_{IN} = 12V, V_{CC} = 6V$                                 |       | 1     |       | μ <mark>Α</mark> |   |

| V <sub>cc</sub> Undervoltage Lockout<br>Threshold             | Rising Edge                                                              |       | 2.8   | 2.95  | V                |   |

| V <sub>cc</sub> Undervoltage Lockout<br>Hysteresis            |                                                                          |       | 200   |       | mV               |   |

| IN Under voltage lockout threshold                            | Rising Edge                                                              |       | 2.85  | 2.95  | V                |   |

| IN Under voltage lockout hysteresis                           |                                                                          |       | 300   |       | mV               |   |

| Pogulated EP Voltage                                          | T <sub>A</sub> = +25°C                                                   | 0.778 | 0.794 | 0.810 | V                |   |

| Regulated FB Voltage                                          | –40°C ≤ T <sub>A</sub> ≤ +85°C                                           | 0.770 |       | 0.818 | V                |   |

| FB Input Current                                              | V <sub>FB</sub> = 0.85V                                                  | -50   |       | 50    | nA               |   |

| EN High Threshold                                             | –40°C ≤ T <sub>A</sub> ≤ +85°C                                           | 1.6   |       |       | V                |   |

| EN Low Threshold                                              | –40°C ≤ T <sub>A</sub> ≤ +85°C                                           |       |       | 0.4   | V                |   |

| Soft-Start Charging Current                                   |                                                                          |       | 5     |       | μA               |   |

| High-Side Switch On-Resistance                                | I <sub>sw</sub> = 300mA                                                  |       | 80    |       | mΩ               |   |

| Low-Side Switch On-Resistance                                 | I <sub>sw</sub> = –300mA                                                 |       | 80    |       | mΩ               |   |

| SW Leakage Current                                            | V <sub>EN</sub> = 0V; V <sub>IN</sub> = 12V; V <sub>SW</sub> = 0V or 12V | -10   |       | 10    | μA               |   |

| Oscillator Frequency                                          |                                                                          | 450   | 600   | 750   | kHz              |   |

| Synch Frequency <sup>(5)</sup>                                |                                                                          | 0.5   |       | 2     | MHz              |   |

| Minimum On Time                                               |                                                                          |       | 50    |       | ns               |   |

| Maximum Duty Cycle                                            |                                                                          |       | 90    |       | %                |   |

| Thermal Shutdown Threshold                                    | Hysteresis = 20°C                                                        |       | 150   |       | °C               |   |

| High-Side Switch Current Limit                                | Sourcing                                                                 |       | 6     |       | Α                |   |

| Low-Side Switch Current Limit                                 | Sinking                                                                  |       | 2     |       | А                |   |

| Minimum On Time                                               |                                                                          |       | 50    |       | ns               |   |

| Maximum Duty Cycle                                            |                                                                          | 90    |       |       | %                |   |

| Thermal Shutdown Threshold                                    | Hysteresis = 20°C                                                        |       | 150   |       | °C               | ] |

Note:

5) Guaranteed by design.

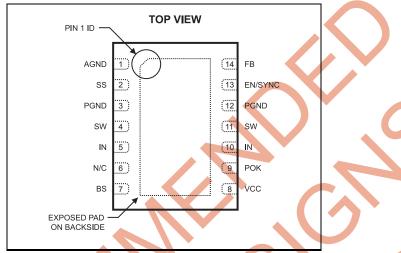

## **PIN FUNCTIONS**

| Pin #       | Name          | Description                                                                                                                                                                                                                                                               |

|-------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 3,<br>12 | PGND,<br>AGND | Ground. Connect these pins with larger copper areas to the negative terminals of the input and output capacitors.                                                                                                                                                         |

| 2           | SS            | Soft-Start Input. Place a capacitor from SS to AGND. The SS pin sources 5µA. As the SS voltage rises, the feedback threshold voltage increases to limit the inrush current during start-up. <b>Do not leave this pin open.</b>                                            |

| 4, 11       | SW            | Switch Node Connection to the Inductor. These pins connect to the internal high and low-<br>side power MOSFET switches. All SW pins must be connected together externally.                                                                                                |

| 5, 10       | IN            | Input Supply. This supplies power to the high side switch. A decoupling capacitor to ground is required close to this pin to reduce switching spikes.                                                                                                                     |

| 6           | N/C           | No Connect.                                                                                                                                                                                                                                                               |

| 7           | BS            | Bootstrap. A capacitor between this pin and SW provides a floating supply for the high-side gate driver.                                                                                                                                                                  |

| 8           | VCC           | Bias Supply. This supplies power to both the internal control circuit and the gate drivers. A decoupling capacitor to ground is required close to this pin.                                                                                                               |

| 9           | POK           | Power Okay Pin. Open drain power Good output. "HIGH" input indicates $V_{OUT}$ is within ±10% window, "LOW" output indicates $V_{OUT}$ is out of ±10% window.                                                                                                             |

| 13          | EN/SYNC       | Enable and Frequency Synchronization Input Pin. Forcing this pin below 0.4V shuts down the part. Forcing this pin above 1.6V turns on the part. Applying a 500kHz to 2MHz clock signal to this pin synchronizes the internal oscillator frequency to the external source. |

| 14          | FB            | Feedback. This is the input to the error amplifier. An external resistive divider connected between the output and GND is compared to the internal 0.8V reference to set the regulation voltage. Don't apply a voltage more than $V_{cc}$ to this pin.                    |

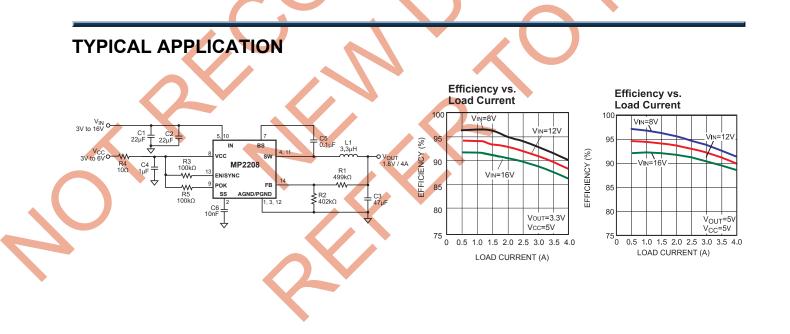

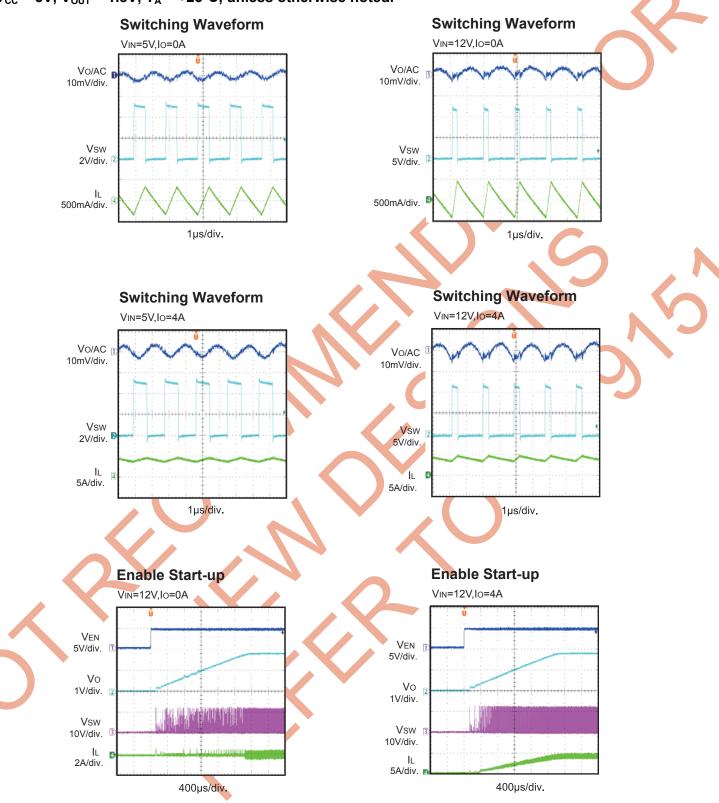

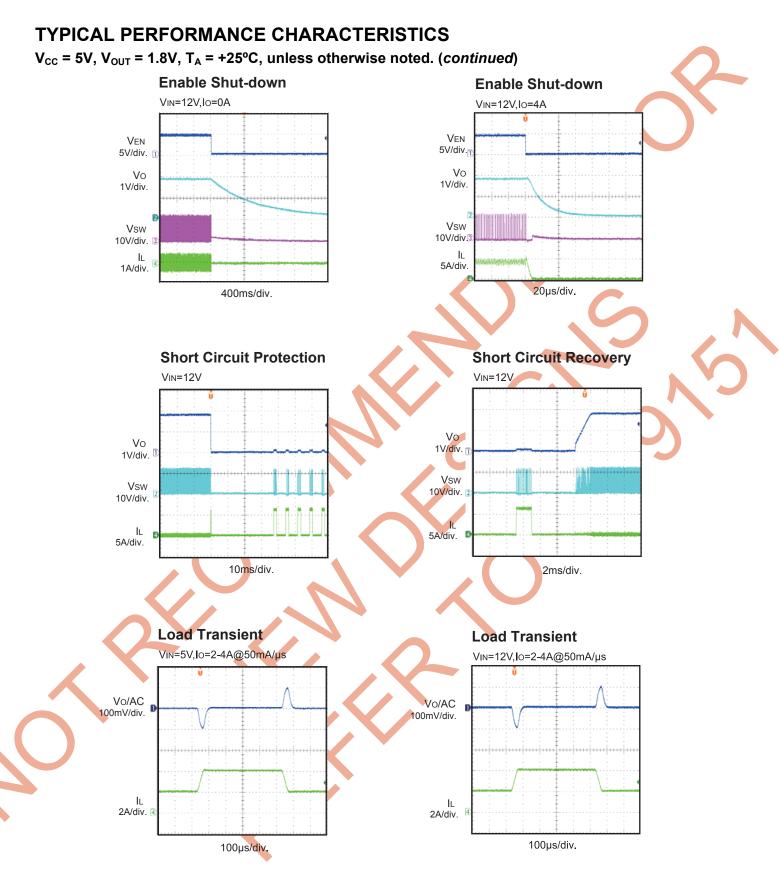

## **TYPICAL PERFORMANCE CHARACTERISTICS**

$V_{CC} = 5V$ ,  $V_{OUT} = 1.8V$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2012 MPS. All Rights Reserved.

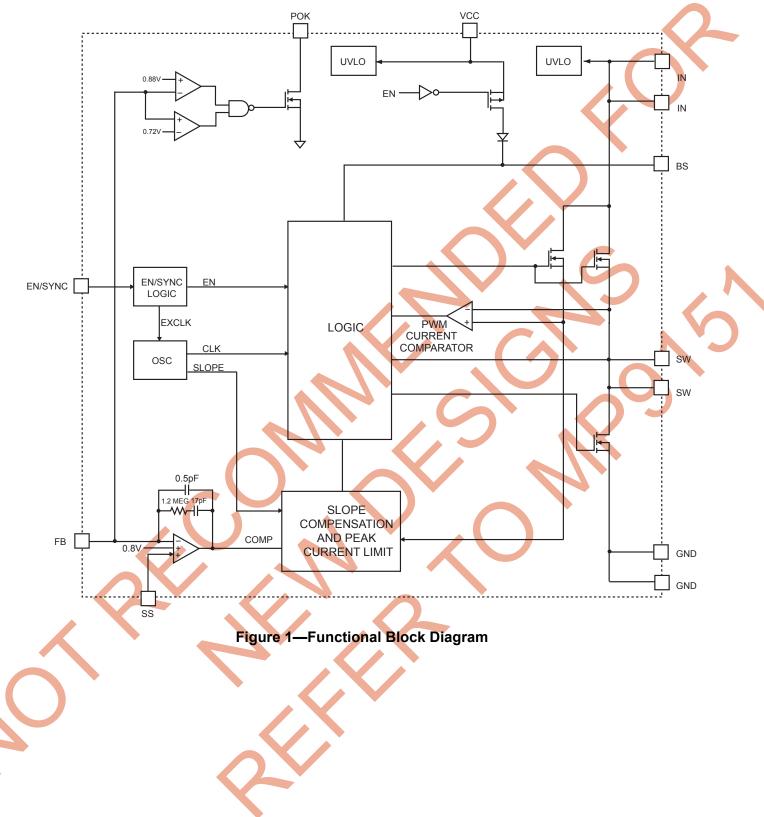

## FUNCTIONAL BLOCK DIAGRAM

## **OPERATION**

#### **PWM Control**

The MP2208 is a constant frequency peakcurrent-mode control PWM switching regulator. Refer to the functional block diagram. The high side N-Channel DMOS power switch turns on at the beginning of each clock cycle. The current in the inductor increases until the PWM current comparator trips to turn off the high side DMOS switch. The peak inductor current at which the current comparator shuts off the high side power switch is controlled by the COMP voltage at the feedback error amplifier. output of The transconductance from the COMP voltage to the output current is set at 11.25A/V.

This current-mode control greatly simplifies the feedback compensation design by approximating the switching converter as a single-pole system. Only Type II compensation network is needed, which is integrated into the MP2208. The loop bandwidth is adjusted by changing the upper resistor value of the resistor divider at the FB pin. The internal compensation in the MP2208 simplifies the compensation design, minimizes external component counts, and keeps the flexibility of external compensation for optimal stability and transient response.

# Enable and Frequency Synchronization (EN/SYNC PIN)

This is a dual function input pin. Forcing this pin below 0.4V for longer than 4us shuts down the part; forcing this pin above 1.6V for longer than 4µs turns on the part. Applying a 0.5MHz to 2MHz clock signal to this pin also synchronizes the internal oscillator frequency to the external clock. When the external clock is used, the part turns on after detecting the first few clocks regardless of duty cycles. If any ON or OFF period of the clock is longer than 4µs, the signal will be intercepted as an enable input and disables the synchronization. For automatic start up, connect this pin to  $V_{CC}$  with a pull-up resistor; don't apply a voltage more than  $V_{CC}$  to this pin.

#### Soft-Start and Output Pre-Bias Startup

The soft start time can be adjusted by connecting a capacitor from this pin to ground. When the soft-start period starts, an internal  $5\mu$ A current source begins charging the external capacitor. During soft-start, the voltage on the soft-start capacitor is connected to the non-inverting input of the error amplifier. The soft-start period lasts until the voltage on the soft-start capacitor exceeds the reference voltage of 0.8V. At this point the reference voltage takes over at the no inverting error amplifier input. The soft-start time can be calculated as follows:

$t_{ss}(ms) = \frac{0.8V \times C_{ss}(nF)}{5\mu A}$

If the output of the MP2208 is pre-biased to a certain voltage during startup, the IC will disable the switching of both high-side and low-side switches until the voltage on the internal soft-start capacitor exceeds the sensed output voltage at the FB pin.

#### **Over Current Protection**

The MP2208 offers cycle-to-cycle current limiting for both high-side and low-side switches. The high-side current limit is relatively constant regardless of duty cycles. When the output is shorted to ground, causing the output voltage to drop below 50% of its nominal output, the IC is shut down momentarily and begins discharging the soft start capacitor. It will restart with a full soft-start when the soft-start capacitor is fully discharged. This hiccup process is repeated until the fault is removed.

#### Power Good Output (POK pin)

The MP2208 includes an open-drain power good output that indicates whether the regulator output is within  $\pm 10\%$  of its nominal output. When the output voltage moves outside this range, the POK output is pulled to ground. There is a 30µs deglitch time when POK output change its state. Connect this pin to V<sub>CC</sub> through a pull-up resistor to get a proper power good output.

#### Bootstrap (BST PIN)

The gate driver for the high-side N-channel DMOS power switch is supplied by a bootstrap capacitor connected between the BS and SW pins. When the low-side switch is on, the capacitor is charged through an internal boost diode. When the high-side switch is off and the high-side switch turns on, the voltage on the bootstrap capacitor is boosted above the input voltage and the internal bootstrap diode prevents the capacitor from discharging.

MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2012 MPS. All Rights Reserved.

#### Input UVLO

Both VCC and IN pins have input UVLO detection. Until both VCC and IN voltage exceed under voltage lockout threshold, the parts remain in shutdown condition. There are also under voltage lockout hysesteres at both VCC and IN pins.

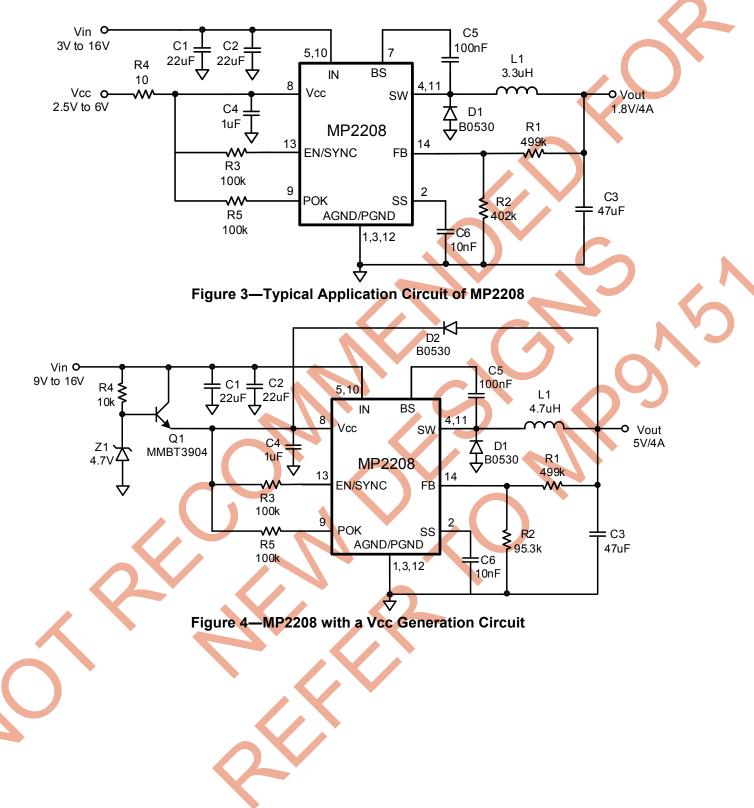

#### VCC Power Supply

VCC is the power supply of both the internal control circuit and the gate drivers. Generally, the VCC power supply could be provided directly by a proper power rail or generated from other VCC generation circuits. For instance, figure 4 shows a typical VCC generation circuit for VOUT=5V application. It is noteworthy that the voltage applied on the VCC pin should never be higher than 6V.

## **APPLICATION INFORMATION**

#### Setting the Output Voltage

The external resistor divider sets the output voltage (see Figure 1). The feedback resistor R1 also sets the feedback loop bandwidth with the internal compensation network (see Figure 1). The relation between R1 and feedback loop bandwidth ( $f_{C}$ ), output capacitance ( $C_{O}$ ) is as follows:

$$\mathsf{R1}(\mathsf{K}\Omega) = \frac{1.24 \times 10^6}{\mathsf{f}_{\rm C}(\mathsf{KHz}) \times \mathsf{C}_{\rm O}(\mathsf{uF})}$$

The recommended feedback loop bandwidth (fc) is no higher than  $1/10_{th}$  of switching frequency of MP2208. In the case of ceramic capacitor as Co, it's usually set to be in the range of 30kHz and 50kHz for optimal transient performance and good phase margin. If electrolytic capacitor is used, the recommended loop bandwidth is no higher than  $1/4_{th}$  of the ESR zero frequency (*f*<sub>ESR</sub>). f<sub>ESR</sub> is given by:

$$f_{ESR} = \frac{1}{2\pi \times R_{ESR} \times C_{O}}$$

For example, choose  $f_c=50$ kHz with ceramic capacitor, Co=47uF, R1 is estimated to be 523K $\Omega$ . R2 is then given by:

$$R2 = \frac{R1}{\frac{V_{OUT}}{0.8V} - 1}$$

#### Table 1—Resistor Selection vs. Output Voltage Setting

| VOUT<br>(V) | R1<br>(kΩ) | R2<br>(kΩ) | L (µH)      | COUT<br>(ceramic) |

|-------------|------------|------------|-------------|-------------------|

| 1.2         | 499        | 1000       | 2.2µH-6.8µH | 47µF              |

| 1.5         | 499        | 562        | 2.2µH-6.8µH | 47µF              |

| 1.8         | 499        | 402        | 2.2µH-6.8µH | 47µF              |

| 3.3         | 499        | 158        | 3.3µH-6.8µH | 47µF              |

| 5           | 499        | 95.3       | 4.7µH-10µH  | 47µF              |

|                  |                           | ggcoled oun        |                 | Inductore             |                               |

|------------------|---------------------------|--------------------|-----------------|-----------------------|-------------------------------|

| Manufacturer     | Part Number               | Inductance<br>(µH) | Max DCR<br>(mΩ) | Current<br>Rating (A) | Dimensions L x W x<br>H (mm3) |

| ТОКО             |                           |                    |                 |                       |                               |

|                  | FDA1055-3R3M              | 3.3                | 7.3             | 11.7                  | 10.8x11.6x5.5                 |

|                  | D128C-931AS-4R7M          | 4.7                | 9.6             | 8.7                   | 12.3x12.3x8                   |

| Wurth Electronic | S                         |                    |                 |                       |                               |

|                  | 744314330                 | 3.3                | 9.6             | 8                     | 7x6.9x5                       |

|                  | 74 <mark>4</mark> 7797470 | 4.7                | 27              | 8                     | 10x10x4.3                     |

| TDK              |                           |                    |                 |                       |                               |

|                  | ULF100457-3R3N6R9         | 3.3                | 11.6            | 7.5                   | 10x9.7x4.5                    |

|                  | VLF12060T-4R7N7R7         | 4.7                | 11.6            | 9.1                   | 12.3x12x6                     |

| Solocting the    | Inductor                  |                    |                 |                       | ΔL                            |

#### Table 2—Suggested Surface Mount Inductors

#### Selecting the Inductor

A 2.2 $\mu$ H to 10 $\mu$ H inductor with DC current rating at least 25% higher than the maximum load current is recommended for most applications. For best efficiency, the inductor DC resistance shall be <10m $\Omega$ . See Table 2 for recommended inductors and manufacturers. For most designs, the inductance value can be derived from the following equation:

$$L = \frac{V_{OUT} x (V_{IN} - V_{OUT})}{V_{IN} x \Delta I_L x f_{OSC}}$$

where  $\Delta I_{\perp}$  is Inductor Ripple Current. Choose inductor ripple current approximately 30% of the maximum load current, 4A. The maximum inductor peak current is

$$I_{\text{(MAX)}} = I_{\text{LOAD}} + \frac{\Delta I_{\text{L}}}{2}$$

Under light load conditions, larger inductance is recommended for improved efficiency

#### Input Capacitor Selection

I,

The input capacitor reduces the surge current drawn from the input and switching noise from the device. The input capacitor impedance at the switching frequency shall be less than input source impedance to prevent high frequency switching current passing to the input. Ceramic capacitors with X5R or X7R dielectrics are highly recommended because of their low ESR and small temperature coefficients. For most applications, a 47µF capacitor is sufficient.

#### **Output Capacitor Selection**

The output capacitor keeps output voltage ripple small and ensures regulation loop stable. The output capacitor impedance shall be low at the switching frequency. Ceramic capacitors with X5R or X7R dielectrics are recommended. If electrolytic capacitor is used, pay attention to output ripple voltage, extra heating, and the selection of feedback resistor R1 (refer to "Output Voltage Setting" section) due to large ESR of electrolytic capacitor.

#### **External Schottky Diode**

For this part, an external schottky diode is recommended to be placed close to "SW" and "GND" pins, especially when the output current is larger than 2A.

With the external schottky diode, the voltage spike and negative kick on "SW" pin can be minimized; moreover, the conversion efficiency can also be improved a little.

For the external schottky diode selection, it's noteworthy that the maximum reverse voltage rating of the external diode should be larger than the maximum input voltage. As for the current rating of this diode, 0.5A rating should be sufficient.

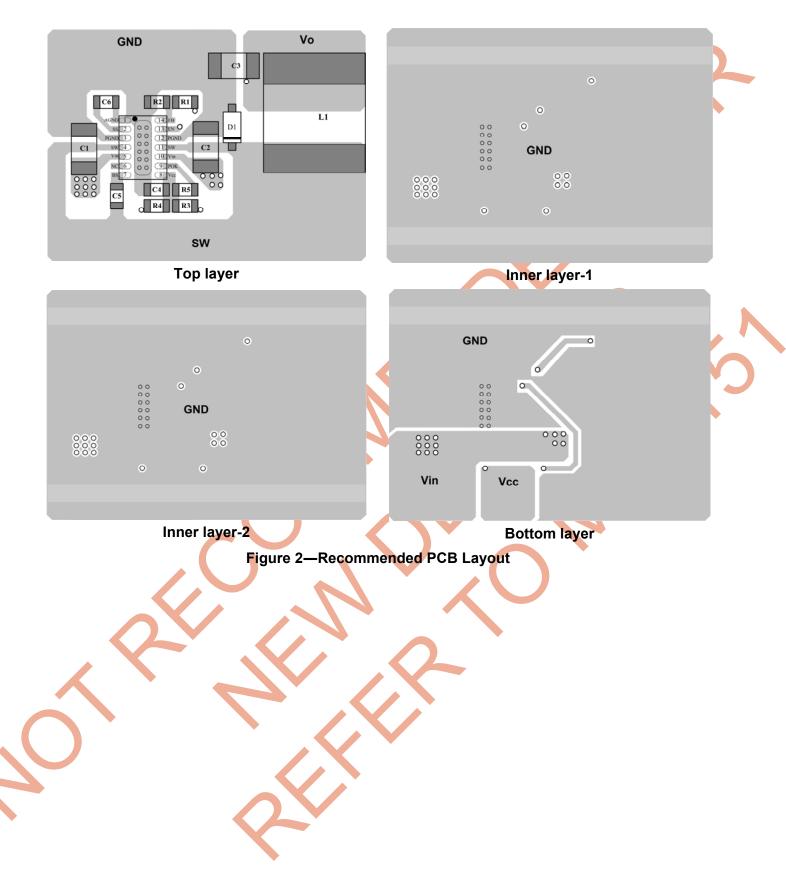

#### **PCB Layout Guide**

PCB layout is very important to achieve stable operation. It is highly recommended to duplicate EVB layout for optimum performance. If change is necessary, please follow these guidelines as follows. Here, the typical application circuit is taken as an example to illustrate the key layout rules should be followed.

- 1) For MP2208, a PCB layout with >=4 layers is recommended.

- 2) The high current paths (GND, IN and SW) should be placed very close to the device with short, direct and wide traces.

- Two input ceramic capacitors (2 x (10μF~22μF)) are strongly recommended to be placed on both sides of the MP2208DL package and keep them as close as possible to the "IN" and "GND" pins.

- 4) A RC low pass filter is recommended for VCC supply. The VCC decoupling capacitor must be placed as close as possible to "VCC" pin and "GND" pin.

- 5) The external feedback resistors shall be placed next to the FB pin. Keep the FB trace as short as possible.

- 6) Keep the switching node SW short and away from the feedback network.

## **TYPICAL APPLICATION CIRCUIT**

## **PACKAGE INFORMATION**

**NOTICE:** The information in this document is subject to change without notice. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.