# **MP2110** 3A Synchronous Step-Down Converter with Programmable Input Current Limit

The Future of Analog IC Technology

# DESCRIPTION

The MP2110 is a monolithic step-down switch mode converter with integrated input current limit switch. The step-down converter integrates a main switch and a synchronous rectifier for high efficiency without an external Schottky diode. The input average current limit can be externally programmed. It is ideal for powering portable equipment that is powered by an USB port. The MP2110 can supply 3A of load current from a 3.3V to 5.4V continuous input voltage with excellent load and line regulation. The MP2110 input can support up to 12V transient and clamp the current limit switch output at 5.65V (Typical).

The Constant-On-time (COT) control scheme provides fast transient response high light-load efficiency and easy loop stabilization. Fault condition protection includes cycle-by-cycle current limit and thermal shutdown.

The MP2110 is available in a space-saving 14-pin 3mmx3mm QFN package.

## **FEATURES**

- High Efficiency: Up to 95%

- High Current Step-Down Converter

- 1.5MHz Switching Frequency

- 70mΩ/50mΩ Internal Power MOSFET

- 3A Available Load Current

- ◆ 100% Low Dropout Operation

- Output Voltage as Low as 0.6V

- Input Current Limit Switch

- Programmable Current Limit: 0.3-3A

- ± 10% Current Limit Accuracy when Current Limit > 1A

- Wide Input Voltage Range: 3.3V to 5.4V

- ◆ 12V Input Transient Tolerance

- 70mΩ Internal MOSFET

- OVP Clamp Protection

- Independent Enable Pins

- External Temperature Sense & Protection

- Internal Thermal Fault Protection

- Space Saving 3mm x 3mm QFN14 Package

## **APPLICATIONS**

- Wireless Modem Data Cards

- USB Powered Devices

- Cellular and Smart Phones

- Portable Instruments

All MPS parts are lead-free and adhere to the RoHS directive. "MPS" and "The Future of Analog IC Technology" are Registered Trademarks of Monolithic Power Systems, Inc. ADAM (Analog Digital Adaptive Modulation), AAM (....) are Trademarks of Monolithic Power Systems, Inc.

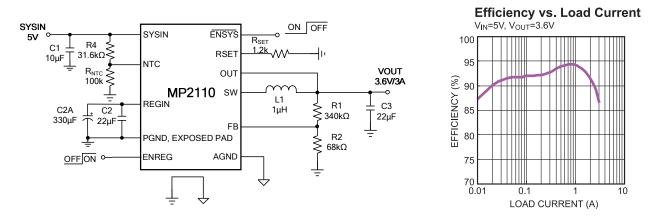

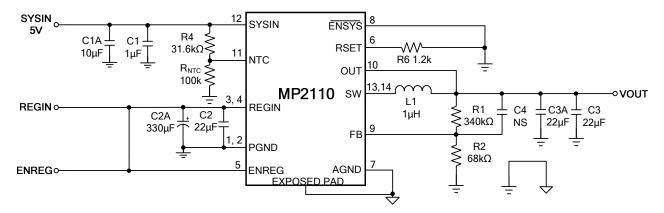

# TYPICAL APPLICATION

1 www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2014 MPS. All Rights Reserved.

## **ORDERING INFORMATION**

| Part Number* | Package            | Top Marking |

|--------------|--------------------|-------------|

| MP2110GQ     | QFN-14 (3mm x 3mm) | AFQ         |

\* For Tape & Reel, add suffix –Z (e.g. MP2110GQ–Z).

## ABSOLUTE MAXIMUM RATINGS (1)

| V <sub>SYSIN</sub> , V <sub>NTC</sub> to GND | 0.3V to +13V                  |

|----------------------------------------------|-------------------------------|

| V <sub>REGIN</sub> to GND                    | 0.3V to +6.5V                 |

| V <sub>sw</sub> to GND0.3                    | V to V <sub>REGIN</sub> +0.3V |

| All other pins to GND                        | 0.3V to +6.5V                 |

| Continuous Power Dissipation                 | $(T_A = +25^{\circ}C)^{(2)}$  |

|                                              |                               |

| Junction Temperature                         | +150°C                        |

| Lead Temperature                             | +260°C                        |

| Storage Temperature                          | -65°C to +150°C               |

## *Thermal Resistance* <sup>(4)</sup> *θ<sub>JA</sub> θ<sub>JC</sub>* QFN-14 (3mmx3mm) ...... 50 ...... 12... °C/W

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature T<sub>J</sub> (MAX), the junction-toambient thermal resistance  $\theta_{JA}$ , and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub> (MAX) = (T<sub>J</sub> (MAX)-T<sub>A</sub>)/ $\theta_{JA}$ . Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB.

## **ELECTRICAL CHARACTERISTICS**

$V_{SYSIN} = V_{ENREG} = 5.0V$ ,  $V_{ENSYS} = GND$ , L=1µH, T<sub>A</sub> = +25°C, unless otherwise noted.

| Parameter                                  | Symbol                        | Condition                                          | Min   | Тур   | Max   | Units               |

|--------------------------------------------|-------------------------------|----------------------------------------------------|-------|-------|-------|---------------------|

| Supply Current (No Switching)              | Ι <sub>Q</sub>                | V <sub>FB</sub> = 0.63V                            |       | 190   | 230   | μA                  |

| Shutdown Current                           | I <sub>STD</sub>              | V <sub>ENSYS</sub> = 5V                            |       | 3     | 5     | μA                  |

| SYSIN Under Voltage<br>Lockout Threshold   | $V_{SYSIN_R}$                 | Rising Edge                                        | 2.2   | 2.4   | 2.6   | V                   |

| SYSIN Under Voltage<br>Lockout Hysteresis  | V <sub>SYSIN_HYS</sub>        |                                                    |       | 140   |       | mV                  |

| REGIN Under Voltage<br>Lockout Threshold   | $V_{\text{REGIN}_R}$          | Rising Edge                                        | 2.5   | 2.8   | 3.1   | V                   |

| REGIN Under Voltage<br>Lockout Hysteresis  | $V_{\text{REGIN}_{HYS}}$      |                                                    |       | 340   |       | mV                  |

| Regulator Input<br>Discharge Threshold     | $V_{\text{DISCH}_F}$          | SYSIN Falling                                      | 2.7   | 2.9   | 3.1   | V                   |

| Discharge Hysteresis                       | V <sub>DISCH_HYS</sub>        |                                                    |       | 100   |       | mV                  |

| Discharge MOSEFT On Resistance             | R <sub>ON_DISCH</sub>         | V <sub>SYSIN</sub> = 2.6V                          |       | 8.5   | 15    | Ω                   |

| External Thermal Sense Trip Voltage        | $V_{NCT_R}$                   | R <sub>NTC</sub> =NCP18WF104<br>(100°C), R4=31.6kΩ | 12.5  | 14.5  | 16.5  | %V <sub>SYSIN</sub> |

| External Thermal Sense<br>Recovery Voltage | V <sub>NCT_F</sub>            | R <sub>NTC</sub> =NCP18WF104<br>(80°C), R4=31.6kΩ  | 25    | 27    | 29    | %V <sub>SYSIN</sub> |

| System Input Current Lin                   | nit Switch                    |                                                    |       |       |       |                     |

| Current Limit Switch On Resistance         | R <sub>ON_SW</sub>            | I <sub>SWITCH</sub> =100mA                         |       | 70    | 85    | mΩ                  |

|                                            | I <sub>LIMIT1</sub>           | R <sub>SET</sub> = 13.3kΩ                          | 290   | 390   | 490   | mA                  |

| Current Limit                              | I <sub>LIMIT2</sub>           | R <sub>SET</sub> = 5.1kΩ                           | 710   | 810   | 910   | mA                  |

|                                            | I <sub>LIMIT3</sub>           | R <sub>SET</sub> = 3.48kΩ                          | 1.05  | 1.15  | 1.25  | Α                   |

| EN Input Logic Low Voltage                 | $V_{\text{SYSEN}\_L}$         |                                                    |       |       | 0.4   | V                   |

| En Input Logic High Voltage                | $V_{\text{SYSEN}_{\text{H}}}$ |                                                    | 1.5   |       |       | V                   |

| EN Input Current                           | I <sub>SYSEN</sub>            | V <sub>EN</sub> = 5V                               |       | 3.5   | 7     | μA                  |

| Output Clamping Voltage                    | V <sub>OVP</sub>              | Over Voltage<br>Protection                         | 5.45  | 5.65  | 5.85  | V                   |

| Output Soft-start Time                     | t <sub>ss</sub>               | Output from 10% to 90%                             |       | 2.5   |       | ms                  |

| Step-Down Regulator                        |                               |                                                    |       |       |       |                     |

| Feedback Voltage                           | V <sub>FB</sub>               | $2.7V \le V_{\text{REGIN}} \le 6V$                 | 0.588 | 0.600 | 0.612 | V                   |

| Feedback Current                           | I <sub>FB</sub>               | V <sub>FB</sub> =0.6V                              |       | 10    | 50    | nA                  |

| PFET Switch On Resistance                  | Rdson_p                       | V <sub>REGIN</sub> =5V                             |       | 70    |       | mΩ                  |

| NFET Switch On<br>Resistance               | Rdson_n                       | V <sub>REGIN</sub> =5V                             |       | 50    |       | mΩ                  |

## **ELECTRICAL CHARACTERISTICS**

### $V_{SYSIN} = V_{ENREG} = 5.0V$ , $V_{ENSYS} = GND$ , L=1µH, T<sub>A</sub> = +25°C, unless otherwise noted.

| Parameter                                      | Symbol                 | Condition              | Min | Тур | Max | Units |

|------------------------------------------------|------------------------|------------------------|-----|-----|-----|-------|

| PFET Current Limit                             | I <sub>LIMIT REG</sub> |                        | 3.9 | 5   |     | А     |

| On Time <sup>(5)</sup>                         | T <sub>ON</sub>        | V <sub>OUT</sub> =3.6V |     | 520 |     | ns    |

| Minimum Off Time <sup>(5)</sup>                | T <sub>OFF</sub>       |                        |     | 60  |     | ns    |

| Soft-Start Time                                | t <sub>ss</sub>        | Output from 10% to 90% |     | 1.5 |     | ms    |

| EN Input Logic Low Voltage                     | V <sub>ENREG L</sub>   |                        |     |     | 0.4 | V     |

| En Input Logic High Voltage                    | V <sub>ENREG H</sub>   |                        | 1.5 |     |     | V     |

| EN Input Current                               | I <sub>ENREG</sub>     | $V_{EN}$ = 0V to 6V    | -1  |     | 1   | μA    |

| Thermal Shutdown Trip Threshold <sup>(5)</sup> | T <sub>OTP</sub>       |                        |     | 160 |     | °C    |

| Thermal Shutdown Hysteresis <sup>(5)</sup>     | T <sub>OTP_HYS</sub>   |                        |     | 20  |     | °C    |

Note:

5) Guaranteed by characterization test.

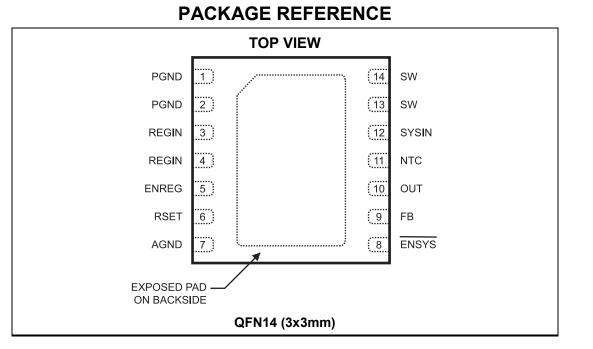

## **PIN FUNCTIONS**

mps

| Pin #  | Name           | Description                                                                                                                                                                                                                                                           |

|--------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2   | PGND           | Power Ground. PGND is internally connected to the source of the low-side N-channel MOSFET.                                                                                                                                                                            |

| 3, 4   | REGIN          | Current limit switch output and buck regulator input. Usually this pin connects to a large tantalum capacitor as energy reservoir.                                                                                                                                    |

| 5      | ENREG          | On/Off Control Input of Step-Down Regulator. Active high. Can not be floated.                                                                                                                                                                                         |

| 6      | RSET           | Input Current Limit setting pin. A resistor from this pin to ground sets the input current limit.                                                                                                                                                                     |

| 7      | AGND           | Analog Ground. Internally connects to the analog ground of control circuitry.                                                                                                                                                                                         |

| 8      | ENSYS          | Current Limit Switch Enable Input. Active low. It has internal pull down resister.                                                                                                                                                                                    |

| 9      | FB             | Feedback Input. Connect FB to the center point of the external resistor divider. The feedback threshold voltage is 0.6V.                                                                                                                                              |

| 10     | OUT            | Sense pin for output voltage.                                                                                                                                                                                                                                         |

| 11     | NTC            | Thermistor Input. Connect a resistor from this pin to SYSIN pin and the thermistor from this pin to ground. Connect to SYSIN to disable the thermal sense function.                                                                                                   |

| 12     | SYSIN          | Supply Voltage. SYSIN supplies power for internal current limit switch. MP2110 operates from a 3.3V to 5.4V continuous input voltage and 12V transient input voltage.C1 is needed to prevent large voltage spikes at the input. Put C1as close to the IC as possible. |

| 13, 14 | SW             | Power Switch Output. Inductor connection to drains of the internal PFET and NFET switches.                                                                                                                                                                            |

|        | Exposed<br>Pad | The exposed pad and PGND pin must be connected to the same ground plane.                                                                                                                                                                                              |

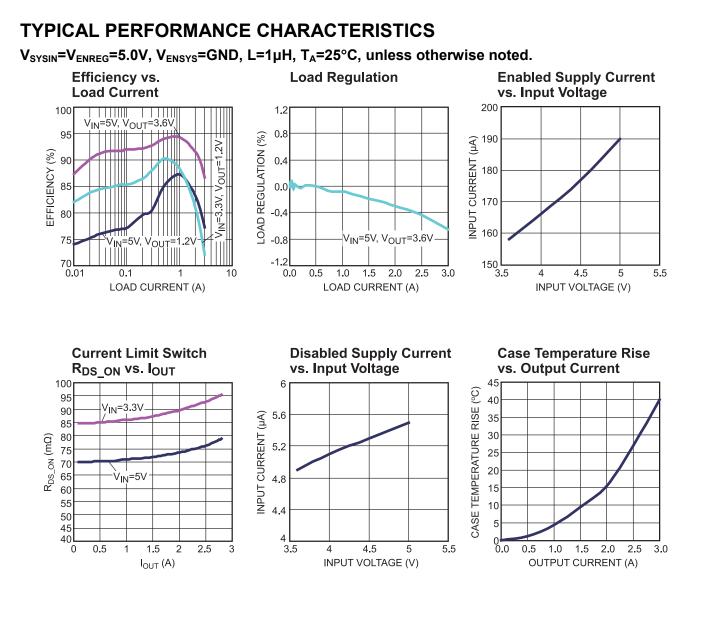

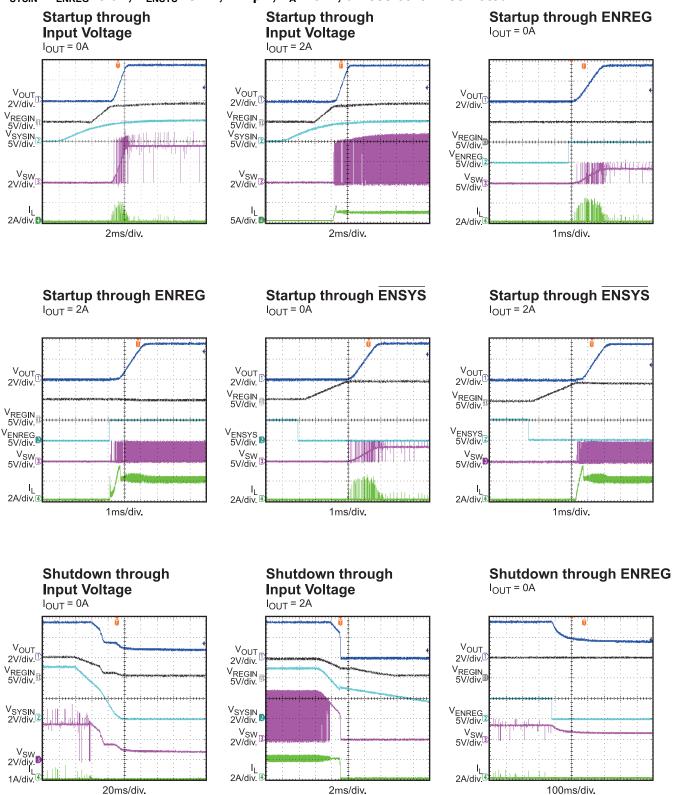

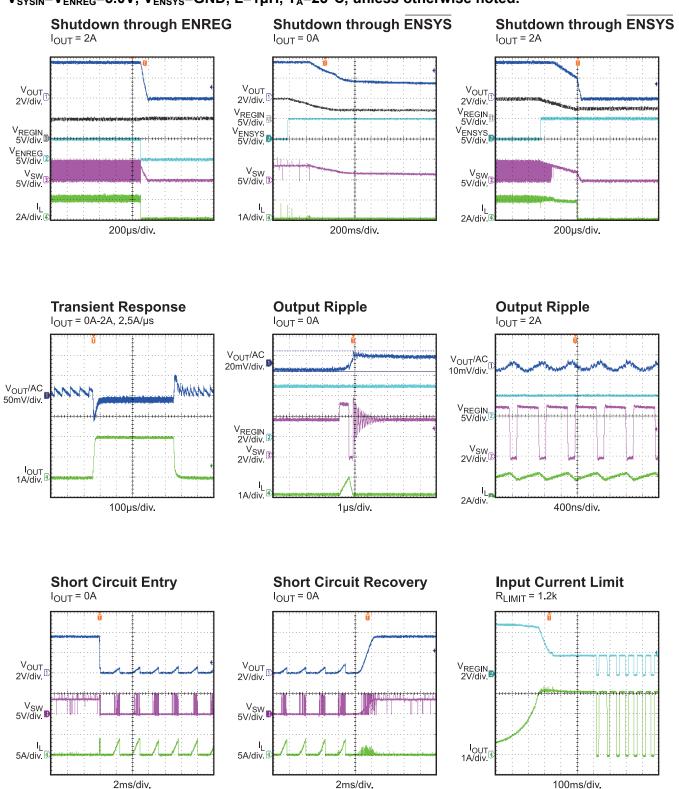

## **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

V<sub>SYSIN</sub>=V<sub>ENREG</sub>=5.0V, V<sub>ENSYS</sub>=GND, L=1µH, T<sub>A</sub>=25°C, unless otherwise noted.

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2014 MPS. All Rights Reserved.

## **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

V<sub>SYSIN</sub>=V<sub>ENREG</sub>=5.0V, V<sub>ENSYS</sub>=GND, L=1µH, T<sub>A</sub>=25°C, unless otherwise noted.

www.MonolithicPower.com MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited. © 2014 MPS. All Rights Reserved.

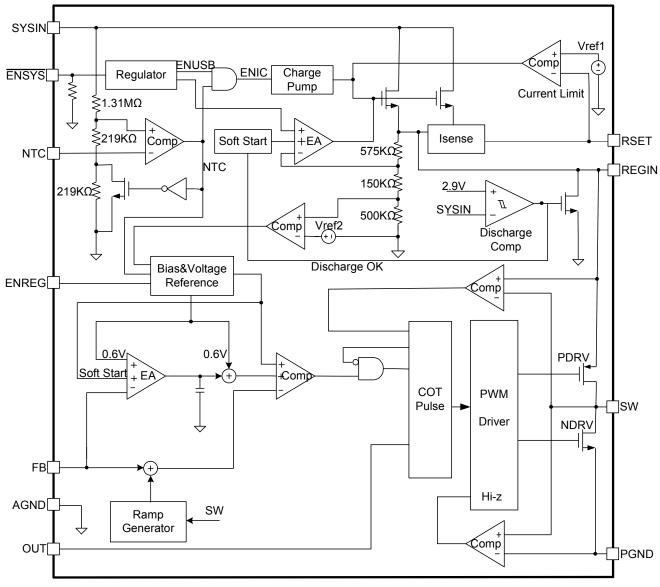

## FUNCTIONAL BLOCK DIAGRAM

Figure 1: Functional Block Diagram

## **OPERATION**

The MP2110 is a high efficiency, 1.5MHz, synchronous step-down converter with input current limit switch. The MP2110 is optimized for low voltage, USB port and Li-Ion battery powered applications where high efficiency and small size are critical. The MP2110 can achieve 100% duty cycle.

MP2110 uses constant on-time control with input voltage feed forward to stabilize the switching frequency over full input range. At light load, MP2110 employs a proprietary control of low side switch and inductor current to eliminate ringing on switching node and improve efficiency.

#### **Constant On-time Control**

Compare to fixed frequency PWM control, constant on-time control offers the advantage of simpler control loop and faster transient response. By using input voltage feed forward, MP2110 maintains a nearly constant switching frequency across input and output voltage range. The ontime of the switching pulse can be estimated as:

$$T_{ON} = \frac{V_{OUT}}{V_{IN}} \cdot 0.722 \mu s$$

To prevent inductor current run away during load transient, MP2110 fixes the minimum off time to be 60ns. However, this minimum off time limit will not affect operation of MP2110 in steady state.

#### **Light Load Operation**

In light load condition, MP2110 uses a proprietary control scheme to save power and improve efficiency. Instead of turning off the low side switch immediately when inductor current start to reverse, MP2110 gradually ramp down and regulates the low side switch current to a minimal level, thus avoids the ringing at switching node that always occurs in discontinuous conduction mode (DCM) operation.

#### **Current Limit**

MP2110 has a typical 5A current limit for the high side switch. When the high side switch hits current limit, the high side switch will turn off, and low side switch will turn on until the inductor current decreases to the valley current limit. This will prevent inductor current from continuing to build up which will result in damage of the components.

### **Short Circuit Protection**

MP2110 enters short circuit protection mode after the inductor current hits the current limit and lasts for 100µs, and tries to recover from short circuit with hiccup mode. In short circuit protection, MP2110 will disable output power stage, discharge soft-start cap and then automatically try to soft-start again. If the short circuit condition still holds, MP2110 repeats this operation cycle till short circuit disappears and output rises back to regulation level.

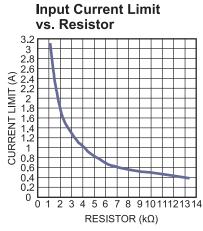

#### Programmable Input Current Limit

The MP2110 has an input current limit protection function. It will insure that the input current doesn't exceed the maximum value, when the input is supplied by the USB. Once the input current triggers the set current limit level, the output current will hold at the current limit until thermal shutdown.

The current limit can be estimated as:

$$I_{\text{LIM}} = \frac{0.96x4}{R_{\text{SET}}(k\Omega)} (A)^{(6)}$$

The input current limit resistor value can be found from Table 1.

#### Notes:

6) The formula is theoretic. Refer to table 1 for accurate current limit setting.

| I <sub>LIMIT</sub> (A) | R <sub>SET</sub> (kΩ) |

|------------------------|-----------------------|

| 0.39                   | 13.3                  |

| 0.6                    | 7.15                  |

| 0.81                   | 5.1                   |

| 1.05                   | 3.92                  |

| 1.15                   | 3.48                  |

| 1.52                   | 2.4                   |

| 1.85                   | 1.96                  |

| 2.05                   | 1.74                  |

| 2.25                   | 1.58                  |

| 2.57                   | 1.37                  |

| 2.83                   | 1.24                  |

| 3.08                   | 1.13                  |

#### **Output over Voltage Clamp**

As the system input voltage rises up and the current limit switch's output exceeds its OVP threshold 5.65V, the output voltage (REGIN) will be clamped to 5.65V.

#### **Current Limit Switch Output Discharge**

When the current limit switch's input SYSIN is lower than 2.9V, MP2110 turns on the discharge MOSFET to discharge the REGIN capacitor storage. Discharge resistance is typical  $8.5\Omega$  and the specific discharge time depends on the capacitance between REGIN and GND.

# Negative Thermal Coefficient (NTC) Thermistor

The MP2110 has a built-in NTC comparator that allows it to sense the external device's temperature via the thermistor mounted near the device. It ensures a safe operating environment and prevents any smoke and fire happen due to over temperature. Connect an appropriatelyvalued resistor from SYSIN to the NTC-pin and connect the thermistor from the NTC-pin to AGND. The resistor divider with a dividing ratio depends on device temperature determines the voltage on the NTC-pin. Once the voltage at the NTC-pin falls to 14.5% of V<sub>SYSIN</sub>, the MP2110 output is disabled. The MP2110 restarts if the voltage rises to 27% of V<sub>SYSIN</sub>.

#### Thermal Shutdown

Thermal shutdown is implemented to prevent the chip from operating at exceedingly high temperatures. When the silicon die temperature is higher than 160°C, it shuts down the whole chip. When the temperature is lower than its lower threshold, typically 140°C, the chip is enabled again.

## **APPLICATION INFORMATION**

#### **Output Voltage Setting**

The external resistor divider sets the output voltage (see Typical Application Circuit on page 1).

Choose R1 around  $200k\Omega$  for optimal transient response. R2 is then given by:

$$R2 = \frac{R1}{\frac{V_{OUT}}{0.6V} - 1}$$

#### Table 2—Resistor Selection vs. Output Voltage Setting

| V <sub>OUT</sub> | R1         | R2          |

|------------------|------------|-------------|

| 1V               | 180kΩ (1%) | 267kΩ (1%)  |

| 1.2V             | 180kΩ (1%) | 180kΩ (1%)  |

| 1.8V             | 180kΩ (1%) | 88.7kΩ (1%) |

| 2.5V             | 340kΩ (1%) | 107kΩ (1%)  |

| 3.3V             | 340kΩ (1%) | 75kΩ (1%)   |

| 3.6V             | 340kΩ (1%) | 68kΩ (1%)   |

#### **Inductor Selection**

A 0.47 $\mu$ H to 4.7 $\mu$ H inductor with DC current rating at least 25% higher than the maximum load current is recommended for most applications. For best efficiency, the inductor DC resistance shall be <200m $\Omega$ . See Table 3 for recommended inductors and manufacturers. For most designs, the inductance value can be derived from the following equation:

$$L1 = \frac{V_{OUT} \times (V_{IN} - V_{OUT})}{V_{IN} \times \Delta I_{I} \times f_{OSC}}$$

Where  $\Delta_{IL}$  is the Inductor Ripple Current. Choose inductor ripple current approximately 30% of the maximum load current, 3A.

The maximum inductor peak current is:

$$I_{L(MAX)} = I_{LOAD} + \frac{\Delta I_{L}}{2}$$

Under light load conditions below 100mA, larger inductance is recommended for improved efficiency.

| Manufacturer | Part Number | Inductance (µH) | Max DCR (Ω) | Saturation<br>Current (A) | Dimensions<br>LxWxH (mm <sup>3</sup> ) |

|--------------|-------------|-----------------|-------------|---------------------------|----------------------------------------|

| Wurth        | 744777001   | 1               | 0.0084      | 9                         | 7.3X7.3X4.5                            |

| Toko         | DFE252012C  | 1               | 0.059       | 3                         | 2.5X2.0X1.2                            |

#### V<sub>SYSIN</sub> Input Capacitor Selection

The input capacitor (C1) reduces the surge current drawn from the input and switching noise from the device. The input capacitor impedance at the switching frequency must be less than input source impedance to prevent high frequency switching current passing to the input. Ceramic capacitors with X5R or X7R dielectrics are highly recommended because of their low ESR and small temperature coefficients. For most applications, a  $10\mu$ F capacitor is sufficient.

#### **V**<sub>REGIN</sub> Capacitor Selection

The  $V_{\text{REGIN}}$  capacitor is used to supply the Buck port and with the peak output current, such as during the TDM frame. That output peak current is about 3A. Use a large tantalum capacitor to avoid large voltage drops.

#### Selecting the Output Capacitor

The output capacitor (C3) is required to maintain the DC output voltage. Ceramic capacitors are recommended. Low ESR capacitors are preferred to keep the output voltage ripple low. The output voltage ripple can be estimated by:

$$\Delta V_{\text{OUT}} = \frac{V_{\text{OUT}}}{f_{\text{S}} \times L_{1}} \times \left(1 - \frac{V_{\text{OUT}}}{V_{\text{IN}}}\right) \times \left(R_{\text{ESR}} + \frac{1}{8 \times f_{\text{S}} \times C3}\right)$$

Where  $L_1$  is the inductor value and  $R_{ESR}$  is the equivalent series resistance (ESR) value of the output capacitor.

Using ceramic capacitors, the impedance at the switching frequency is dominated by the capacitance. The output voltage ripple is mainly caused by the capacitance. For simplification, the output voltage ripple can be estimated by:

$$\Delta V_{\text{OUT}} = \frac{V_{\text{OUT}}}{8 \times f_{\text{S}}^{2} \times L_{1} \times C3} \times \left(1 - \frac{V_{\text{OUT}}}{V_{\text{IN}}}\right)$$

In the case of tantalum or electrolytic capacitors, the ESR dominates the impedance at the switching frequency. For simplification, the output ripple can be approximated to:

$$\Delta V_{\text{out}} = \frac{V_{\text{out}}}{f_{\text{s}} \times L_{1}} \times \left(1 - \frac{V_{\text{out}}}{V_{\text{IN}}}\right) \times R_{\text{esr}}$$

The characteristics of the output capacitor also affect the stability of the regulation system.

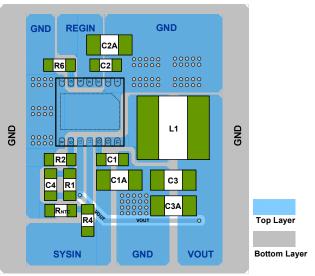

#### **PC Board Layout**

PCB layout is very important to achieve stable operation. For best results, follow these guidelines and use Figure 2 as reference:

- Use large ground plane directly connect to PGND pin. Add vias near the PGND pin if bottom layer is ground plane.

- Place the ceramic input capacitor close to SYSIN/REGIN and PGND pins. Keep the connection of input capacitor and SYSIN/REGIN pin as short and wide as possible.

- Route SW away from sensitive analog areas such as FB, OUT pins. It's not recommended to route SW trace under chip's bottom side.

4) Place the feedback resistors close to chip to ensure the trace which connects to FB pin as short as possible.

## Figure 2: PCB Layout

#### Design Example

Below is a design example following the application guidelines for the specifications:

Table 4—Design Example

| V <sub>IN</sub>  | 5V   |

|------------------|------|

| Vout             | 3.6V |

| Ι <sub>ουτ</sub> | 3A   |

The detailed application schematic is shown in Figure 3. The typical performance and circuit waveforms have been shown in the Typical Performance Characteristics section. For more device applications, please refer to the related Evaluation Board Datasheet.

# **TYPICAL APPLICATION CIRCUITS**

Figure 3: Typical Application, 3.6V Output Voltage

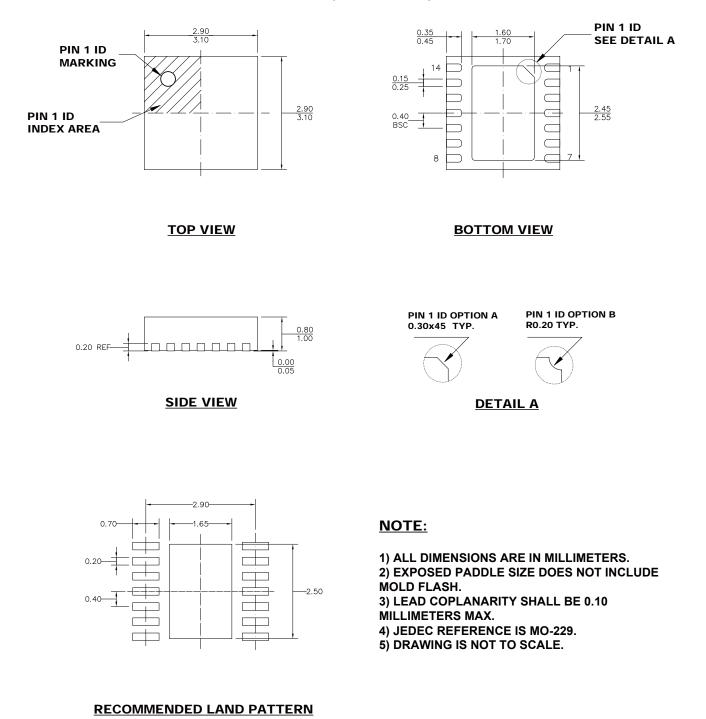

## PACKAGE INFORMATION

QFN-14 (3mm x 3mm)

**NOTICE:** The information in this document is subject to change without notice. Please contact MPS for current specifications. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.