Data Sheet February 22, 2008 FN6474.1

# Boost Regulator with Integrated Schottky and Input Disconnect Switch

The ISL97701 represents a high efficiency boost converter with integrated boost FET, boost diode and input disconnect FET.

With an input voltage of 2.3V to 5.5V the ISL97701 has an output capability of up to 50mA at 18V using integrated 500mA switches. Efficiencies are up to 87%. The integrated protection FET is used to disconnect the boost inductor from the input supply whenever an output fault condition is detected, or when the device is disabled. This gives 0 output current in the disabled mode, compared to standard boost converters where current can still flow when the device is disabled.

The ISL97701 comes in the 10 Ld 3x3 DFN package and is specified for operation over the -40°C to +85°C temperature range.

## **Ordering Information**

| PART<br>NUMBER<br>(Note) | PART<br>MARKING | PACKAGE<br>(Pb-free) | PKG.<br>DWG.# |

|--------------------------|-----------------|----------------------|---------------|

| ISL97701IRZ              | 977 01IRZ       | 10 Ld 3x3 DFN        | MDP0047       |

| ISL97701IRZ-T7*          | 977 01IRZ       | 10 Ld 3x3 DFN        | MDP0047       |

| ISL97701IRZ-T13*         | 977 01IRZ       | 10 Ld 3x3 DFN        | MDP0047       |

<sup>\*</sup>Please refer to TB347 for details on reel specifications.

NOTE: These Intersil Pb-free plastic packaged products employ special Pb-free material sets; molding compounds/die attach materials and 100% matte tin plate PLUS ANNEAL - e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

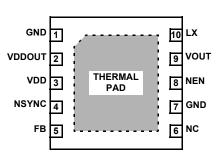

#### **Pinout**

#### **Features**

- Up to 87% efficiency

- · 2.3V to 5.5V input

- · Up to 28V output

- 50mA at 18V

- · Integrated boost Schottky diode

- · Input voltage disconnect switch

- · Synchronization input

- · Chip enable

- 10 Ld 3x3 DFN package

- · Pb-free (RoHS compliant)

## **Applications**

- · OLED display power

- · LED display power

- · Adjustable power supplies

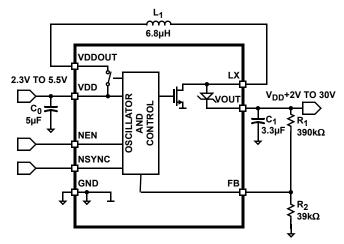

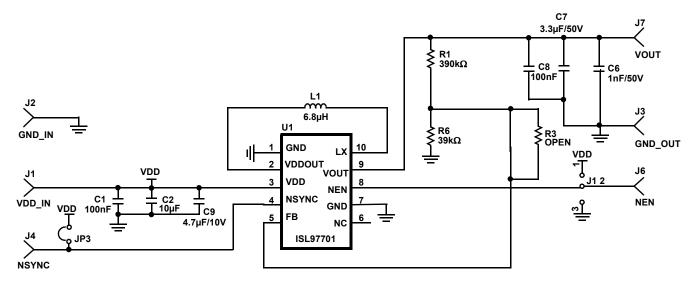

## Typical Application Diagram

NOTE: VOUT = (390k + 39k)/39k\*1.15V = 12.65V

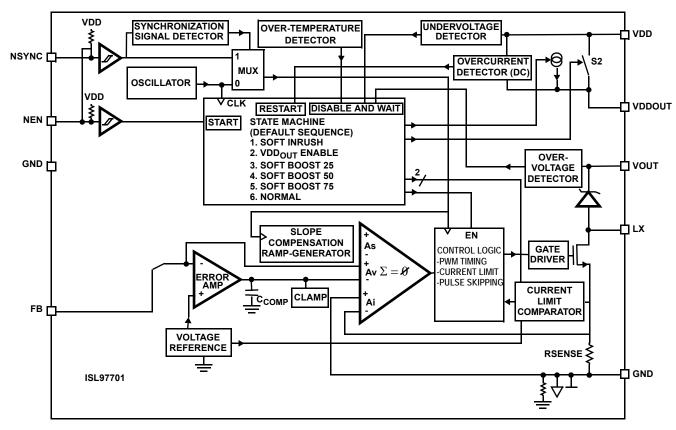

## **Block Diagram**

FIGURE 1. ISL97701 BLOCK DIAGRAM

## **Absolute Maximum Ratings** $(T_A = +25^{\circ}C)$

| VDD to GND                                       |

|--------------------------------------------------|

| V <sub>OUT</sub> to GND                          |

| LX to GND                                        |

| VDDOUT, NSYNC, FB, NEN                           |

| to GND0.3V to VDD + 0.3V                         |

| Continuous Current in VDD, GND, VDDOUT, LX 650mA |

| Continuous Current in NSYNC, FB, NEN 10mA        |

#### **Thermal Information**

| Thermal Resistance (Typical, Notes 1, 2)         | θ <sub>JA</sub> (°C/W) | θ <sub>JC</sub> (°C/W) |

|--------------------------------------------------|------------------------|------------------------|

| 10 Ld 3x3 DFN Package                            | 48                     | 7                      |

| Storage Temperature                              | 65'                    | °C to +150°C           |

| Ambient Operating Temperature (T <sub>A</sub> )  | 40                     | 0°C to +85°C           |

| Operating Junction Temperature (T <sub>J</sub> ) |                        | +125°C                 |

| Maximum Junction Temperature                     |                        | +130°C                 |

| Pb-free reflow profile                           |                        | ee link below          |

| http://www.intersil.com/pbfree/Pb-FreeR          | teflow.asp             |                        |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

- 1.  $\theta_{JA}$  is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief TB379.

- 2. For  $\theta_{\mbox{JC}}$ , the "case temp" location is the center of the exposed metal pad on the package underside.

$\begin{tabular}{ll} \textbf{Electrical Specifications} & V_{DD} = 3.6 V, \ GND = NEN = 0 V, \ NSYNC = V_{DD}, \ R_1 = 390 k\Omega, \ R_2 = 39 k\Omega, \ L = 10 \mu H, \ T_A = -40 ^{\circ} C \ to \ +85 ^{\circ} C \ unless \ otherwise \ stated. \end{tabular}$

| PARAMETER            | DESCRIPTION                                                  | CONDITION                                 | MIN      | TYP          | MAX | UNIT |

|----------------------|--------------------------------------------------------------|-------------------------------------------|----------|--------------|-----|------|

| SUPPLY               |                                                              |                                           |          |              |     |      |

| V <sub>DD</sub>      | Supply Operating Voltage Range                               |                                           | 2.3      |              | 5.5 | V    |

| I <sub>DIS</sub>     | Supply Current when Disabled                                 | NEN = VDD                                 |          | 0.1          | 3   | μA   |

| LOGIC INPUTS         | - NEN, NSYNC                                                 |                                           | <b>-</b> | 1            |     | J.   |

| R <sub>UP</sub>      | Pull-up Resistor                                             | Enabled, Input at GND                     | 150      | 250          | 350 | kΩ   |

| I <sub>IL</sub>      | Leakage Current when Disabled                                | Disabled, Input at GND                    | -1       |              | 1   | μA   |

| VHI                  | Logic High Threshold                                         |                                           | 1.8      |              |     | V    |

| VLO                  | Logic Low Threshold                                          |                                           |          |              | 0.7 | ٧    |

| POWER-ON RE          | SET – VDD                                                    |                                           | <b>-</b> | 1            |     | J.   |

| V <sub>RES_ON</sub>  | Power-On Reset Threshold                                     | V <sub>DD</sub> rising                    |          | 2.2          | 2.3 | V    |

| V <sub>RES_OFF</sub> | Power-Off Threshold                                          | V <sub>DD</sub> falling                   | 1.9      | 2            |     | ٧    |

| LX OUTPUT DE         | RIVER                                                        |                                           | <b>-</b> | 1            |     | J.   |

| fosc                 | LX Switching Frequency with Internal Oscillator              |                                           | 0.9      | 1            | 1.1 | MHz  |

| f <sub>SYNC</sub>    | LX Switching Frequency when Externally Synchronized at NSYNC |                                           |          | f<br>(NSYNC) |     |      |

| t <sub>ON-MIN</sub>  | Minimum On-Time                                              | FB = 0V, I(LX) > Ilim(LX)                 |          | 60           |     | ns   |

| t <sub>OFF-MIN</sub> | Minimum Off-time<br>(≥ Maximum Duty Cycle)                   | FB = 0V, I(LX) < Ilim(LX)                 |          | 60           |     | ns   |

| r <sub>ON</sub>      | LX ON-Resistance                                             | I(LX) = 100mA                             |          | 0.4          |     | Ω    |

| I <sub>LEAK</sub>    | LX Leakage Current                                           | NEN = VDD, V(LX) = 30V                    |          | 1            | 5   | μA   |

| I <sub>PEAK</sub>    | LX Peak Current Limit                                        | t > 8.32ms (end of soft-start)            |          | 1200         |     | mA   |

| SCHOTTKY DIG         | ODE – LX, V <sub>OUT</sub>                                   | +                                         | 1        |              |     | 1    |

| V <sub>DIODE</sub>   | Forward Voltage from LX to V <sub>OUT</sub>                  | I = 10mA, T <sub>A</sub> = +25°C          | 0.4      | 0.5          | 0.6 | V    |

|                      |                                                              | I = 10mA, T <sub>A</sub> = -40°C to +85°C | 0.3      | 0.5          | 0.7 | V    |

intersil FN6474.1 February 22, 2008

## ISL97701

$V_{DD}$  = 3.6V, GND = NEN = 0V, NSYNC =  $V_{DD}$ , R<sub>1</sub> = 390kΩ, R<sub>2</sub> = 39kΩ, L = 10μH, T<sub>A</sub> = -40°C to +85°C unless otherwise stated. **(Continued) Electrical Specifications**

| PARAMETER                       | DESCRIPTION                                   | CONDITION                                                              | MIN  | TYP  | MAX  | UNIT     |

|---------------------------------|-----------------------------------------------|------------------------------------------------------------------------|------|------|------|----------|

| FEEDBACK INI                    | PUTS                                          |                                                                        |      | l.   | l.   | <u>I</u> |

| Vref <sub>FB</sub>              | Input Reference Voltage on FB                 | T <sub>A</sub> = +25°C                                                 | 1.13 | 1.15 | 1.17 | V        |

|                                 |                                               | T <sub>A</sub> = -40°C to +85°C                                        | 1.12 | 1.15 | 1.18 | V        |

| I <sub>FB</sub>                 | Input Current in FB                           | FB = 1.3V                                                              | -0.2 |      | 0.2  | μΑ       |

| R <sub>FB</sub>                 | FB Pull-Down Switch Resistance                | I <sub>FB</sub> = 10mA                                                 |      | 15   | 25   | Ω        |

| SYNCHRONIZA                     | ATION INPUT - NSYNC                           |                                                                        |      |      |      |          |

| f <sub>NSYNC</sub>              | External Sync Frequency Range                 |                                                                        | 600  |      | 1400 | kHz      |

| td <sub>NSYNC</sub>             | NSYNC Falling Edge to LX Falling Edge Delay   | f <sub>NSYNC</sub> = 600kHz                                            |      | 80   | 100  | ns       |

| OVERVOLTAGI                     | DETECTOR - VOUT                               |                                                                        |      |      |      |          |

| V <sub>OUT</sub>                | Overvoltage Threshold                         | FB = GND                                                               | 31   | 35   |      | V        |

| OVERCURREN                      | T DETECTOR                                    |                                                                        |      | +    | +    | Į.       |

| IOCTVDDOUT                      | Overcurrent Threshold                         | t > 2.048ms, DC current                                                |      | 800  |      | mA       |

| OVER-TEMPER                     | RATURE DETECTOR                               |                                                                        |      | 11   | 11   | 1        |

| tOFF                            | Shut-Down Temperature Threshold               | T rising                                                               |      | 135  |      | °C       |

| t <sub>ON</sub>                 | Turn-On Temperature Threshold                 | T falling                                                              |      | 100  |      | °C       |

| FAULT SWITCH                    | I – VDD, VDDOUT                               |                                                                        |      | 1    | II.  | 1        |

| r <sub>ONFS</sub>               | ON-Resistance from VDD to VDDOUT              | I <sub>OUT</sub> = 50mA, t > 2.048ms                                   |      | 0.2  |      | Ω        |

| lleak <sub>VDDOUT</sub>         | Leakage Current                               | V <sub>DDOUT</sub> = 0V                                                |      | 0.01 | 3    | μA       |

| I <sub>SS_VDDOUT</sub>          | Soft Inrush Current Source at VDDOUT          | V <sub>DD</sub> - V <sub>DDOUT</sub> = 0.5V, t <sub>ON</sub> < 2.048ms |      | 50   |      | mA       |

| REGULATION                      |                                               |                                                                        |      | ı    | ı    |          |

| ACC                             | Output Voltage Accuracy, Assuming             | I <sub>OUT</sub> = 10mA, T <sub>A</sub> = +25°C                        | -1.5 |      | 1.5  | %        |

|                                 | Resistor Divider Tolerances of 0.1% or Better | I <sub>OUT</sub> = 10mA, T <sub>A</sub> = -40°C to +85°C               | -2.5 |      | 2.5  | %        |

| $\Delta V_{OUT}/\Delta I_{OUT}$ | Load Regulation                               | I <sub>OUT</sub> = 0mA to 50mA                                         |      | 0.05 |      | %        |

| $\Delta V_{OUT}/\Delta V_{DD}$  | Line Regulation                               | V <sub>DD</sub> = 3.6V to 2.6V, I <sub>OUT</sub> = 30mA                |      | 0.1  |      | %/V      |

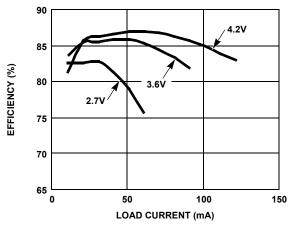

## **Typical Performance Curves**

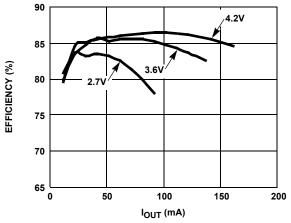

FIGURE 2. EFFICIENCY vs LOAD CURRENT (V $_{OUT}$  = 18.3V) L = 10 $\mu$ H (CDRH4D28C-100NC) C = 6.6 $\mu$ F

FIGURE 3. EFFICIENCY vs  $I_{OUT}$  ( $V_{OUT}$  = 18.3V) L = 6.8µH (TDK RLF7030) C = 6.6µF

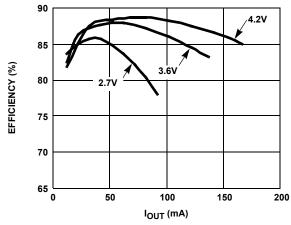

FIGURE 4. EFFICIENCY vs I $_{OUT}$  (V $_{OUT}$  = 12.6V) L = 6.8 $\mu$ H (TDK RLF7030) C = 6.6 $\mu$ F

FIGURE 5. EFFICIENCY vs  $I_{OUT}$  ( $V_{OUT}$  = 12.7V) L = 10 $\mu$ H (CDRH4D28C-100NC) C = 6.6 $\mu$ F

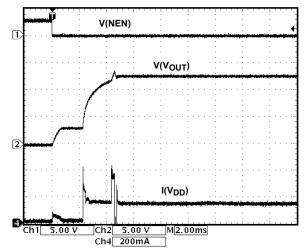

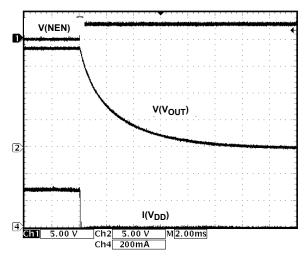

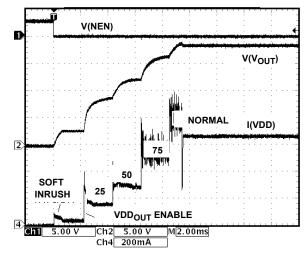

FIGURE 6. START-UP TO 12V ( $V_{DD}$  = 3.6V,  $R_L$  = 360 $\Omega$ )

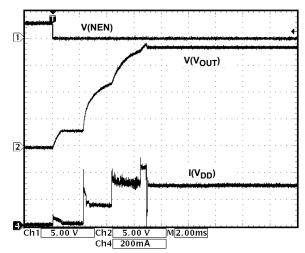

FIGURE 7. START-UP TO 18V ( $V_{DD}$  = 3.6V,  $R_L$  = 360 $\Omega$ )

## Typical Performance Curves (Continued)

FIGURE 8. SHUTDOWN ( $V_{DD} = 3.6V$ ,  $R_L = 360\Omega$ )

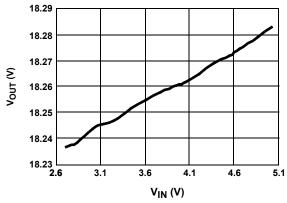

FIGURE 10. LINE REGULATION (I<sub>OUT</sub> = 30mA)

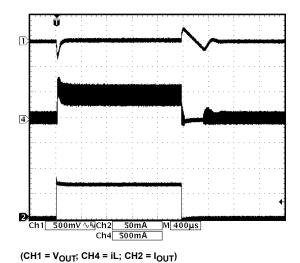

FIGURE 12. TRANSIENT RESPONSE ( $V_{IN}$  = 3.3V;  $V_{OUT}$  = 18.3V; STEP LOAD CURRENT FROM 2.6mA TO 70mA)

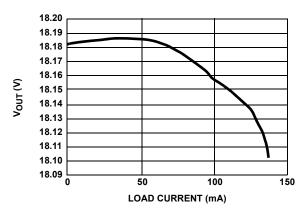

FIGURE 9. LOAD REGULATION ( $V_{IN} = 3.6V$ )

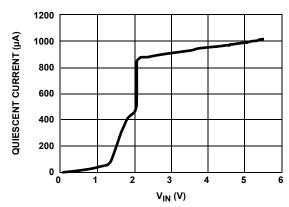

FIGURE 11. QUIESCENT CURRENT vs VIN

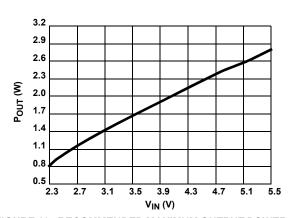

FIGURE 13. RECOMMENDED MAXIMUM OUTPUT POWER vs INPUT VOLTAGE

6

## Pin Descriptions

| PIN<br>NUMBER | PIN NAME         | PIN FUNCTION                         |

|---------------|------------------|--------------------------------------|

| 1             | GND              | Ground                               |

| 2             | VDDOUT           | Protection Switch Output             |

| 3             | VDD              | Supply Input                         |

| 4             | NSYNC            | Synchronization Input (Falling Edge) |

| 5             | FB               | Feedback Input                       |

| 6             | NC               | Do Not Connect                       |

| 7             | GND              | Ground                               |

| 8             | NEN              | Enable Input (Active Low)            |

| 9             | V <sub>OUT</sub> | Boost Output Voltage                 |

| 10            | LX               | Boost FET                            |

#### **Function Overview**

The ISL97701 is a high frequency, high efficiency boost regulator which operates in constant frequency PWM mode. The boost converter generates a stable, higher output voltage from a variable, low voltage input source (e.g. Li-ion battery). The output voltage level is defined from the feedback resistor network in Equation 1.

$$V_{OUT} = V_{refFB} \bullet (R_1 + R_2) / R_2$$

(EQ. 1)

The switching frequency is either generated from the fixed 1MHz internal oscillator or provided externally at the synchronization pin in the range from 600kHz to 1.4MHz. The compensation network and soft-start functions are built in with fixed parameters without any need for further external components.

To stop battery discharge into the output load when disabled, the inductor is disconnected from the input supply with a low ON-resistance power switch.

Built-in fault protection monitors inductor current and output voltage as well as junction temperature in order to interrupt the high current circuit path through the inductor and diode in the event of a load failure.

Low logic input thresholds allow the ISL97701 to interface directly to microcontrollers with lower supply voltage.

Alternatively, the internal pull-up resistors on all logic inputs provide level shifting when driven from open collector outputs.

## **Description of Operation**

#### Enable Pin (Active Low) - NEN

If NEN is high, the ISL97701 shuts down all its internal functions and deactivates its I/So. Only the internal pull-up resistor at NEN remains active. If NEN is high, the input disconnect switch between VDD and VDDOUT interrupts the circuit path from the input voltage VDD through inductor and diode to the output load at  $V_{OUT}$ . If shutdown, the total supply current in VDD is typically less than  $0.1\mu A$ .

When NEN is driven low the ISL97701 begins with the start-up sequence.

#### Start-Up Sequence

After pin NEN is pulled low or a restart is triggered from Fault Control during operation, the ISL97701 goes through a start-up sequence with the following six states: Soft Inrush -> VDDOUT Enable -> Soft Boost 25 -> Soft Boost 50 -> Soft Boost 75 -> Normal.

If the sequence has completed, the ISL97701 stays in the "Normal" state until NEN is high again or any fault is detected.

#### SOFT INRUSH: STATE DURATION ~2.048ms

The switch at VDDOUT is configured as current source and provides a limited current through the inductor to pre-charge the capacitor at V<sub>OUT</sub>.

#### **VDDOUT ENABLE: STATE DURATION ~128Ms**

The switch at VDDOUT is fully enabled and connects the inductor to VDD with a low ON-resistance.

## SOFT BOOST 25 -> 50 -> 75: STATE DURATION 3x ~2.048ms

The boost regulator begins to switch at LX.

The LX current limit increases in three steps representing 25%, 50% and 75% of its final value.

#### **NORMAL**

If no fault was detected Normal state is entered ~8.256ms after NEN is pulled low.

The LX current limit steps up to 100%.

In all states Fault Control can force the sequence to restart or even to shutdown (see Table 1).

FIGURE 14. FAULT CONTROL SEQUENCE

#### **Fault Control**

The input voltage at VDD, current in the VDD $_{OUT}$  switch, voltage at  $V_{OUT}$  and junction temperature  $T_J$  are continuously monitored and can either restart the start-up

sequence or in some cases disable the ISL97701 boost function as long as the fault is present.

**TABLE 1. FAULT PROTECTION**

| FAULT<br>DESCRIPTION                            | FAULT<br>CONDITION                                     | ISL97701 FAULT REACTION                                                                                                                                              |

|-------------------------------------------------|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Undervoltage at VDD                             | V(V <sub>DD</sub> ) <<br>V(V <sub>DD</sub> )off        | Disables I/Os and waits until $V(V_{DD})$ reaches $V(V_{DD})$ on to begin with the start-up sequence                                                                 |

| Overcurrent<br>drawn from<br>VDD <sub>OUT</sub> | I(VDD <sub>OUT</sub> ) ><br>It(VDD <sub>OUT</sub> )err | Disables VDD <sub>OUT</sub> switch and LX driver and immediately restarts the start-up sequence                                                                      |

| Overvoltage at VOUT                             | V(V <sub>OUT</sub> ) ><br>Vt(V <sub>OUT</sub> )err     | Disables VDD <sub>OUT</sub> switch and LX driver and waits until output voltage V(V <sub>OUT</sub> ) drops to Vt(V <sub>OUT</sub> ) to restart the start-up sequence |

| Over-Temperature on chip                        | Tj > Toff                                              | Disables VDD <sub>OUT</sub> switch and LX driver and waits until junction temp drops to "Ton" to restart the start-up sequence                                       |

#### Maximum Duty Cycle - LX

The maximum duty cycle Dmax, at which the power FET can operate defines the upper limit of the regulator output to input voltage ratio according to Equation 2:

$$\frac{V_{OUT}}{V_{IN}} = \frac{1}{1 - D_{MAX}}$$

(EQ. 2)

In the ISL97701,  $D_{\mbox{MAX}}$  is defined from the minimum off-time  $t_{\mbox{OFF}}(\mbox{LX})$ min and the switching frequency.

If NSYNC is tied to VDD the internal oscillator defines  $D_{\mbox{\scriptsize MAX}}$  according to Equation 3:

$$D_{MAX}(f_{OSC}) = 1 - t_{OFF}(LX)min \cdot f_{OSC}$$

(EQ. 3)

With external synchronization at pin NSYNC:

$$D_{MAX}(NSYNC) = 1 - t_{OFF}(LX)min \bullet f(NSYNC)$$

(EQ. 4)

The duty cycle at LX can be 0% (pulse skipping), if the output voltage exceeds the target voltage set with the feedback resistors.

#### Internal Schottky Diode - LX, VOUT

The inductor node LX internally connects to the power FET and to the anode of the integrated power Schottky diode. The cathode of the diode is pin  $V_{OUT}$ . An overvoltage detector at  $V_{OUT}$  continuously monitors the cathode voltage and immediately disables the boost regulator if the voltage exceeds the maximum allowable voltage.

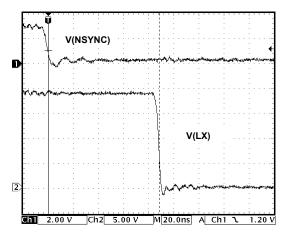

#### External Synchronization Pin - NSYNC

Pin NSYNC can be used to synchronize the LX output pin with an external clock signal in the range from 600kHz to 1.4MHz.

A frequency detector monitoring NSYNC enables external synchronization if f(NSYNC) is higher than ~300kHz. If the

pin is, for example, static high, the internal oscillator defines the LX output frequency and phase. When externally synchronized, all falling edges at LX are timed from the falling edge of the clock signal applied at NSYNC. The timing of the rising edge at LX is defined by the boost controller.

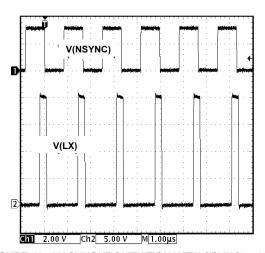

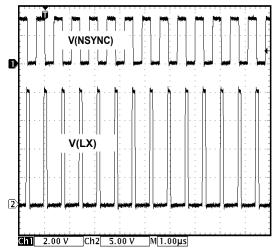

FIGURE 15. NSYNC TO LX SYNCHRONIZATION DELAY

FIGURE 16. LX SYNCHRONIZATION WITH f(SYNC) = 600kHz

FIGURE 17. LX SYNCHRONIZATION WITH f(SYNC) = 1.4MHz

FN6474.1

FIGURE 18. ISL97701 APPLICATION BOARD

## **Typical Application**

Typical applications are passive- or active-matrix organic light emitting diode displays (PMOLED, AMOLED) in handheld devices. Applications with low power or screen saver mode is directly supported.

#### **Components Selection**

The input capacitance is normally  $10\mu f\sim 15\mu F$  and the output capacitor is  $3.3\mu f$  to  $6.6\mu F$ . X5R or X7R type of ceramic capacitor with correct voltage rating is recommended. The output capacitor value will affect the output voltage ripple. The higher the value of the output capacitor, the lower the ripple of the output voltage.

When choosing an inductor, make sure the inductor can handle the average and peak currents given by Equations 5, 6 and 7 (80% efficiency assumed):

$$I_{LAVG} = \frac{I_{OUT} \cdot V_{OUT}}{0.8 \cdot V_{IN}}$$

(EQ. 5)

$$I_{LPK} = I_{LAVG} + \frac{1}{2} \cdot \Delta I_{L}$$

(EQ. 6)

$$\Delta I_{L} = \frac{V_{IN} \cdot (V_{OUT} - V_{IN})}{L \cdot V_{OUT} \cdot f_{OSC}}$$

(EQ. 7)

#### Where:

- ΔI<sub>I</sub> is the peak-to-peak inductor current ripple in Amperes

- · L is the inductance in H

- f<sub>OSC</sub> is the switching frequency, typically 1.0MHz

Optimal combinations of the boost inductor L and the output capacitor  $C_{\mbox{\scriptsize OUT}}$  are listed in Table 2:

TABLE 2. OPTIMAL COMBINATION OF BOOST INDUCTOR L AND OUTPUT CAPACITOR  $\mathbf{C}_{\text{OUT}}$

|               | CAPACITOR (µF) |     |  |

|---------------|----------------|-----|--|

| INDUCTOR (µH) | MIN            | MAX |  |

| 4.7           | 2.2            | 10  |  |

| 6.8           | 3.3            | 10  |  |

| 10            | 4.7            | 10  |  |

| 15            | 6.8            | 10  |  |

Recommended inductor and ceramic capacitor manufacturers are listed in Table 3:

TABLE 3. RECOMMENDED INDUCTOR AND CERAMIC CAPACITOR MANUFACTURERS

| INDUCTOR |                | CERAMIC CAPACITOR |                 |  |

|----------|----------------|-------------------|-----------------|--|

| Sumida:  | www.sumida.com | Taiyo Yuden:      | www.t-yuden.com |  |

| TDK:     | www.tdk.co.jp  | AVX:              | www.avxcorp.com |  |

| Toko:    | www.tokoam.com | Murata:           | www.murata.com  |  |

#### **PCB Layout Considerations**

The layout is very important for the converter to function properly. To ensure the high pulse current in the power ground does not interfere with the sensitive feedback signals, the current loops ( $V_{IN}$ -L1-LX-GND, and  $V_{IN}$ -L1- $V_{OUT}$ -C $_{OUT}$ -GND) should be as short as possible. For the DFN package, there is no separated GND. All return GNDs should be connected in GND pin but with no sharing branch.

The heat of the IC is mainly dissipated through the thermal pad. Maximizing the copper area connected to the thermal pad is preferable. In addition, a solid ground plane is helpful for the EMI performance.

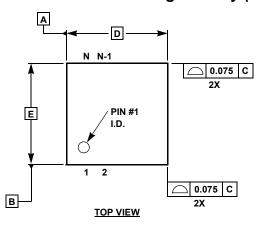

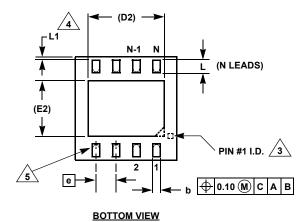

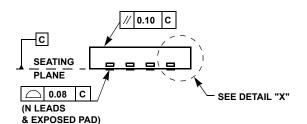

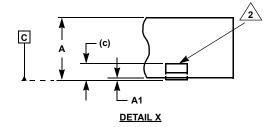

## Dual Flat No-Lead Package Family (DFN)

### MDP0047

DUAL FLAT NO-LEAD PACKAGE FAMILY (JEDEC REG: MO-229)

|        | MILLIMETERS |       |             |

|--------|-------------|-------|-------------|

| SYMBOL | DFN8        | DFN10 | TOLERANCE   |

| Α      | 0.85        | 0.90  | ±0.10       |

| A1     | 0.02        | 0.02  | +0.03/-0.02 |

| b      | 0.30        | 0.25  | ±0.05       |

| С      | 0.20        | 0.20  | Reference   |

| D      | 4.00        | 3.00  | Basic       |

| D2     | 3.00        | 2.25  | Reference   |

| E      | 4.00        | 3.00  | Basic       |

| E2     | 2.20        | 1.50  | Reference   |

| е      | 0.80        | 0.50  | Basic       |

| L      | 0.50        | 0.50  | ±0.10       |

| L1     | 0.10        | 0     | Maximum     |

Rev. 2 2/07

#### NOTES:

- 1. Dimensioning and tolerancing per ASME Y14.5M-1994.

- 2. Exposed lead at side of package is a non-functional feature.

- 3. Bottom-side pin #1 I.D. may be a diepad chamfer, an extended tiebar tab, or a small square as shown.

- 4. Exposed leads may extend to the edge of the package or be pulled back. See dimension "L1".

- Inward end of lead may be square or circular in shape with radius (b/2) as shown.

- 6. N is the total number of leads on the device.

All Intersil U.S. products are manufactured, assembled and tested utilizing ISO9001 quality systems. Intersil Corporation's quality certifications can be viewed at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com