Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## 512-Kbit serial SPI bus EEPROM - 105 °C operation

Datasheet - production data

#### **Features**

- Compatible with the Serial Peripheral Interface (SPI) bus

- Memory array

- 512 Kbit (64 Kbytes) of EEPROM

- Page size: 128 bytes

- Write protection by block: 1/4, 1/2 or whole memory

- Additional Write lockable Page (Identification page)

- Extended temperature and voltage range

- Up to 105 °C (V<sub>CC</sub> from 1.7 V to 5.5 V)

- · High speed clock frequency

- 16 MHz for  $V_{CC} \ge 4.5 \text{ V}$

- 10 MHz for  $V_{CC} \ge 2.5 \text{ V}$

- 5 MHz for  $V_{CC} \ge 1.7 \text{ V}$

- Schmitt trigger inputs for noise filtering

- Short Write cycle time

- Byte Write within 4 ms

- Page Write within 4 ms

- Write cycle endurance

- 4 million Write cycles at 25 °C

- 1.2 million Write cycles at 85 °C

- 900 k Write cycles at 105 °C

- Data retention

- more than 50 years at 105 °C

- 200 years at 55 °C

- ESD Protection (Human Body Model)

- 4000 V

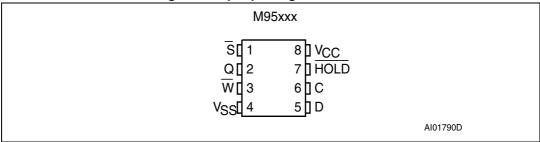

- Packages

- RoHS-compliant and halogen-free (ECOPACK2<sup>®</sup>)

Contents M95512-DRE

## **Contents**

| 1 | Desc  | cription                                  | . 6  |

|---|-------|-------------------------------------------|------|

| 2 | Sign  | al description                            | 8    |

|   | 2.1   | Serial Data output (Q)                    | 8    |

|   | 2.2   | Serial Data input (D)                     | 8    |

|   | 2.3   | Serial Clock (C)                          | 8    |

|   | 2.4   | Chip Select (S)                           | 8    |

|   | 2.5   | Hold (HOLD)                               | 8    |

|   | 2.6   | Write Protect ( $\overline{W}$ )          | 8    |

|   | 2.7   | V <sub>SS</sub> ground                    | 8    |

|   | 2.8   | V <sub>CC</sub> supply voltage            | . 9  |

| 3 | Oper  | rating features                           | . 10 |

|   | 3.1   | Active power and Standby power modes      | . 10 |

|   | 3.2   | SPI modes                                 | . 10 |

|   | 3.3   | Hold mode                                 | 11   |

|   | 3.4   | Protocol control and data protection      | 11   |

|   |       | 3.4.1 Protocol control                    |      |

|   |       | 3.4.2 Status Register and data protection |      |

|   | 3.5   | Identification page                       | . 13 |

| 4 | Instr | uctions                                   | . 15 |

|   | 4.1   | Write Enable (WREN)                       | . 16 |

|   | 4.2   | Write Disable (WRDI)                      | . 16 |

|   | 4.3   | Read Status Register (RDSR)               | . 17 |

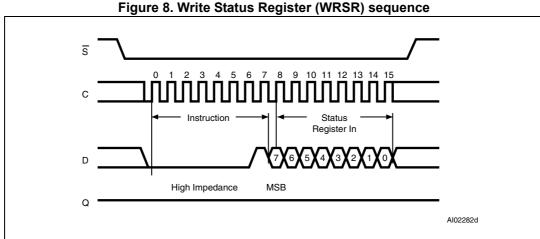

|   | 4.4   | Write Status Register (WRSR)              | . 18 |

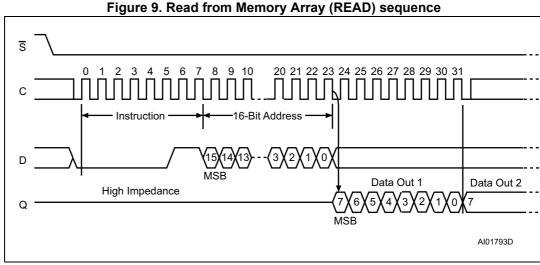

|   | 4.5   | Read from Memory Array (READ)             | . 19 |

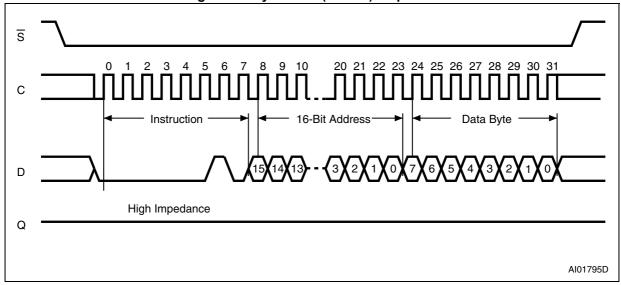

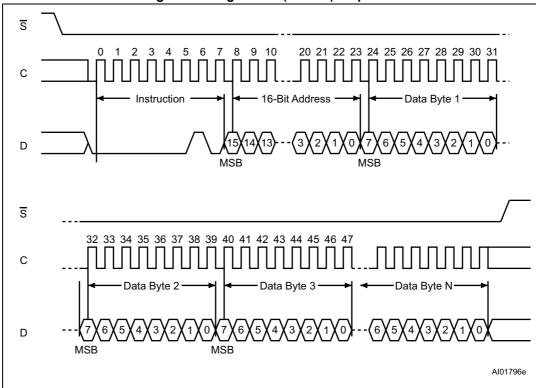

|   | 4.6   | Write to Memory Array (WRITE)             | . 20 |

|   | 4.7   | Read Identification Page (RDID)           | . 22 |

|   | 4.8   | Write Identification Page (WRID)          | . 23 |

|   | 4.9   | Read Lock Status (RDLS)                   | 23   |

|   | 4.10  | Lock Identification Page (LID)            | . 24 |

|   |       |                                           |      |

| 5  | App   | lication design recommendations                   | 6  |

|----|-------|---------------------------------------------------|----|

|    | 5.1   | Supply voltage (V <sub>CC</sub> )                 | 26 |

|    |       | 5.1.1 Operating supply voltage (V <sub>CC</sub> ) | 26 |

|    |       | 5.1.2 Power-up conditions                         | 26 |

|    |       | 5.1.3 Power-down                                  | 27 |

|    | 5.2   | Implementing devices on SPI bus                   | 27 |

|    | 5.3   | Cycling with Error Correction Code (ECC)          | :8 |

| 6  | Deliv | very state                                        | 9  |

| 7  | Abso  | olute maximum ratings2                            | 9  |

| 8  | DC a  | and AC parameters 3                               | 0  |

| 9  | Pack  | kage information                                  | 5  |

|    | 9.1   | SO8N package information                          | 5  |

|    | 9.2   | TSSOP8 package information                        | 6  |

|    | 9.3   | WFDFPN8 package information                       | 7  |

| 10 | Orde  | ering information                                 | 9  |

| 11 | Revi  | sion history                                      | .1 |

List of tables M95512-DRE

## List of tables

| Table 1.  | Signal names                                                                      | 7  |

|-----------|-----------------------------------------------------------------------------------|----|

| Table 2.  | Status Register format                                                            |    |

| Table 3.  | Write-protected block size                                                        |    |

| Table 4.  | Protection modes                                                                  |    |

| Table 5.  | Device identification bytes                                                       |    |

| Table 6.  | Instruction set                                                                   |    |

| Table 7.  | Significant bits within the two address bytes                                     | 15 |

| Table 8.  | Absolute maximum ratings                                                          | 29 |

| Table 9.  | Cycling performance by groups of 4 bytes                                          | 30 |

| Table 10. | Operating conditions (voltage range R, temperature range 8)                       |    |

| Table 11. | Operating conditions (voltage range R, temperature range 8)                       |    |

|           | for high-speed communications                                                     | 30 |

| Table 12. | DC characteristics (voltage range R, temperature range 8)                         | 31 |

| Table 13. | AC characteristics                                                                |    |

| Table 14. | SO8N – 8-lead plastic small outline, 150 mils body width, package mechanical data | 35 |

| Table 15. | TSSOP8 – 8-lead thin shrink small outline, 3 x 6.4 mm, 0.65 mm pitch,             |    |

|           | package mechanical data                                                           | 36 |

| Table 16. | WFDFPN8 (MLP8) – 8-lead very thin fine pitch dual flat package no lead            |    |

|           | 2 x 3 mm, 0.5 mm pitch, mechanical data                                           | 38 |

| Table 17. | Ordering information scheme                                                       |    |

| Table 18. | Document revision history                                                         |    |

M95512-DRE List of figures

# **List of figures**

| igure 1.  | Logic diagram                                                             | <br>. 6 |

|-----------|---------------------------------------------------------------------------|---------|

| igure 2.  | 8-pin package connections                                                 | <br>. 7 |

| igure 3.  | SPI modes supported                                                       | <br>10  |

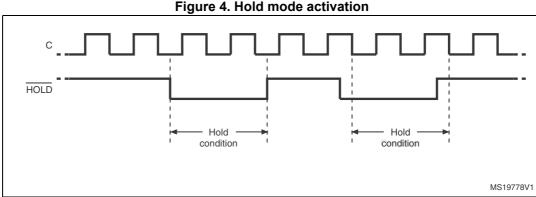

| igure 4.  | Hold mode activation                                                      | <br>11  |

| igure 5.  | Write Enable (WREN) sequence                                              | <br>16  |

| igure 6.  | Write Disable (WRDI) sequence                                             | <br>16  |

| igure 7.  | Read Status Register (RDSR) sequence                                      | <br>17  |

| igure 8.  | Write Status Register (WRSR) sequence                                     | <br>18  |

| igure 9.  | Read from Memory Array (READ) sequence                                    | <br>19  |

| igure 10. | Byte Write (WRITE) sequence                                               | <br>20  |

| igure 11. | Page Write (WRITE) sequence                                               | <br>21  |

| igure 12. | Read Identification Page sequence                                         | <br>22  |

| igure 13. | Write Identification Page sequence                                        | <br>23  |

| igure 14. | Read Lock Status sequence                                                 | <br>24  |

| igure 15. | Lock ID sequence                                                          | <br>24  |

| igure 16. | Bus master and memory devices on the SPI bus                              | <br>27  |

| igure 17. | AC measurement I/O waveform                                               | <br>33  |

| igure 18. | Serial input timing                                                       | <br>33  |

| igure 19. | Hold timing                                                               | <br>33  |

| igure 20. | Serial output timing                                                      | <br>34  |

| igure 21. | SO8N – 8-lead plastic small outline, 150 mils body width, package outline | <br>35  |

| igure 22. | TSSOP8 – 8-lead thin shrink small outline, 3 x 6.4 mm, 0.65 mm pitch,     |         |

|           | package outline                                                           | <br>36  |

| igure 23. | WFDFPN8 (MLP8) – 8-lead very thin fine pitch dual flat package no lead    |         |

|           | 2 x 3 mm, 0.5 mm, package outline                                         | <br>37  |

Description M95512-DRE

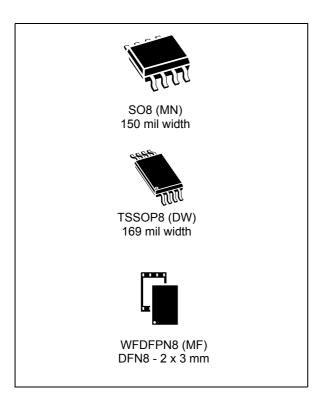

## 1 Description

The M95512-DRE is a 512-Kbit serial EEPROM device operating up to 105 °C. The M95512-DRE is compliant with the level of reliability defined by the AEC-Q100 grade 2.

The device is accessed by a simple serial SPI compatible interface running up to 16 MHz.

The memory array is based on advanced true EEPROM technology (Electrically Erasable PROgrammable Memory). The M95512-DRE is a byte-alterable memory (65536 × 8 bits) organized as 512 pages of 128 bytes in which the data integrity is significantly improved with an embedded Error Correction Code logic.

The M95512-DRE offers an additional Identification Page (128 bytes) in which the ST device identification can be read. This page can also be used to store sensitive application parameters which can be later permanently locked in read-only mode.

Figure 1. Logic diagram

M95512-DRE Description

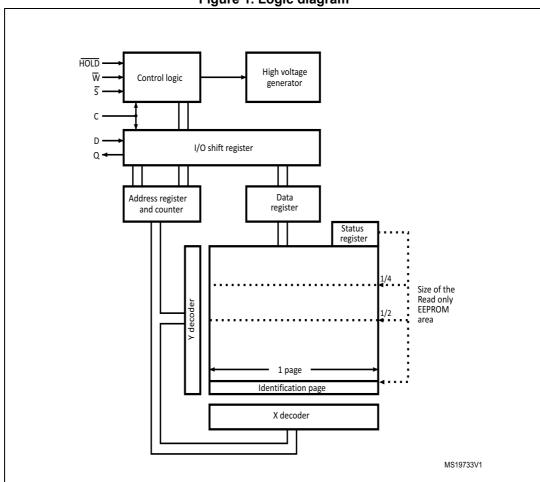

Figure 2. 8-pin package connections

1. See *Package information* section for package dimensions and how to identify pin-1.

Table 1. Signal names

| Signal name     | Description        |  |  |  |  |  |  |

|-----------------|--------------------|--|--|--|--|--|--|

| С               | Serial Clock       |  |  |  |  |  |  |

| D               | Serial data input  |  |  |  |  |  |  |

| Q               | Serial data output |  |  |  |  |  |  |

| S               | Chip Select        |  |  |  |  |  |  |

| W               | Write Protect      |  |  |  |  |  |  |

| HOLD            | Hold               |  |  |  |  |  |  |

| V <sub>CC</sub> | Supply voltage     |  |  |  |  |  |  |

| V <sub>SS</sub> | Ground             |  |  |  |  |  |  |

Signal description M95512-DRE

## 2 Signal description

All input signals must be held high or low (according to voltages of  $V_{IH}$  or  $V_{IL}$ , as specified in *Table 12*). These signals are described below.

### 2.1 Serial Data output (Q)

This output signal is used to transfer data serially out of the device during a Read operation. Data is shifted out on the falling edge of Serial Clock (C), most significant bit (MSB) first. In all other cases, the Serial Data output is in high impedance.

### 2.2 Serial Data input (D)

This input signal is used to transfer data serially into the device. D input receives instructions, addresses, and the data to be written. Values are latched on the rising edge of Serial Clock (C), most significant bit (MSB) first.

### 2.3 Serial Clock (C)

This input signal allows to synchronize the timing of the serial interface. Instructions, addresses, or data present at Serial Data Input (D) are latched on the rising edge of Serial Clock (C). Data on Serial Data Output (Q) changes after the falling edge of Serial Clock (C).

## 2.4 Chip Select (S)

Driving Chip Select  $(\overline{S})$  low selects the device in order to start communication. Driving Chip Select  $(\overline{S})$  high deselects the device and Serial Data output (Q) enters the high impedance state.

## 2.5 Hold (HOLD)

The Hold (HOLD) signal is used to pause any serial communications with the device without deselecting the device.

## 2.6 Write Protect $(\overline{W})$

This pin is used to write-protect the Status Register.

## 2.7 V<sub>SS</sub> ground

$V_{SS}$  is the reference for all signals, including the  $V_{CC}$  supply voltage.

57/

M95512-DRE Signal description

## 2.8 V<sub>CC</sub> supply voltage

$V_{CC}$  is the supply voltage pin. Refer to Section 3.1: Active power and Standby power modes and to Section 5.1: Supply voltage (VCC).

Operating features M95512-DRE

## 3 Operating features

### 3.1 Active power and Standby power modes

When Chip Select  $(\overline{S})$  is low, the device is selected and in the Active power mode.

When Chip Select  $(\overline{S})$  is high, the device is deselected. If a Write cycle is not currently in progress, the device then goes in to the Standby power mode, and the device consumption drops to  $I_{CC1}$ , as specified in *Table 12*.

#### 3.2 SPI modes

The device can be driven by a microcontroller with its SPI peripheral running in either of the two following modes:

- CPOL=0, CPHA=0

- CPOL=1, CPHA=1

For these two modes, input data is latched in on the rising edge of Serial Clock (C), and output data is available from the falling edge of Serial Clock (C).

The difference between the two modes, as shown in *Figure 3*, is the clock polarity when the bus master is in Stand-by mode and not transferring data:

- C remains at 0 for (CPOL=0, CPHA=0)

- C remains at 1 for (CPOL=1, CPHA=1)

Figure 3. SPI modes supported

10/42 DocID027432 Rev 2

M95512-DRE Operating features

#### 3.3 Hold mode

The Hold (HOLD) signal is used to pause any serial communications with the device without resetting the clocking sequence.

The Hold mode starts when the Hold (HOLD) signal is driven low and the Serial Clock (C) is low (as shown in *Figure 4*). During the Hold mode, the Serial Data output (Q) is high impedance, and the signals present on Serial Data input (D) and Serial Clock (C) are not decoded. The Hold mode ends when the Hold (HOLD) signal is driven high and the Serial Clock (C) is or becomes low.

Deselecting the device while it is in Hold mode resets the paused communication.

### 3.4 Protocol control and data protection

#### 3.4.1 Protocol control

The Chip Select  $(\overline{S})$  input offers a built-in safety feature, as the  $\overline{S}$  input is edge-sensitive as well as level-sensitive: after power-up, the device is not selected until a falling edge has first been detected on Chip Select  $(\overline{S})$ . This ensures that Chip Select  $(\overline{S})$  must have been high prior to going low, in order to start the first operation.

For Write commands (WRITE, WRSR, WRID, LID) to be accepted and executed:

- the Write Enable Latch (WEL) bit must be set by a Write Enable (WREN) instruction

- a falling edge and a low state on Chip Select (S) during the whole command must be decoded

- instruction, address and input data must be sent as multiple of eight bits

- the command must include at least one data byte

- Chip Select (S) must be driven high exactly after a data byte boundary

Write command can be discarded at any time by a rising edge on Chip Select  $(\overline{S})$  outside of a byte boundary.

To execute Read commands (READ, RDSR, RDID, RDLS), the device must decode:

- a falling edge and a low level on Chip Select  $(\overline{S})$  during the whole command

- instruction and address as multiples of eight bits (bytes)

From this step, data bits are shifted out until the rising edge on Chip Select  $(\overline{S})$ .

Operating features M95512-DRE

#### 3.4.2 Status Register and data protection

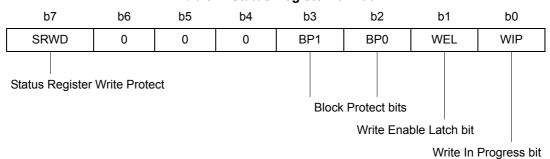

The Status Register format is shown in *Table 2* and the status and control bits of the Status Register are as follows:

Table 2. Status Register format

Note: Bits b6, b5, b4 are always read as 0.

#### **WIP** bit

The WIP bit (Write In Progress) is a read-only flag that indicates the Ready/Busy state of the device. When a Write command (WRITE, WRSR, WRID, LID) has been decoded and a Write cycle  $(t_W)$  is in progress, the device is busy and the WIP bit is set to 1. When WIP=0, the device is ready to decode a new command.

During a Write cycle, reading continuously the WIP bit allows to detect when the device becomes ready (WIP=0) to decode a new command.

#### **WEL** bit

The WEL bit (Write Enable Latch) bit is a flag that indicates the status of the internal Write Enable Latch. When WEL is set to 1, the Write instructions (WRITE, WRSR, WRID, LID) are executed; when WEL is set to 0, any decoded Write instruction is not executed.

The WEL bit is set to 1 with the WREN instruction. The WEL bit is reset to 0 after the following events:

- Write Disable (WRDI) instruction completion

- $\hbox{ Write instructions (WRITE, WRSR, WRID, LID) completion including the write cycle time $t_W$ } \\$

- Power-up

#### BP1, BP0 bits

The Block Protect bits (BP1, BP0) are non-volatile. BP1,BP0 bits define the size of the memory block to be protected against write instructions, as defined in *Table 2*. These bits are written with the Write Status Register (WRSR) instruction, provided that the Status Register is not protected (refer to "SRWD bit and W input signal", on page 13).

12/42 DocID027432 Rev 2

M95512-DRE Operating features

Status Register bits **Protected block** Protected array addresses BP1 BP0 0 0 None None 0 1 Upper quarter C000h - FFFFh 1 0 Upper half 8000h - FFFFh 1 1 Whole memory 0000h - FFFFh plus Identification page

Table 3. Write-protected block size

### SRWD bit and $\overline{W}$ input signal

The Status Register Write Disable (SRWD) bit is operated in conjunction with the Write Protect pin  $(\overline{W})$  signal. When the SRWD bit is written to 0, it is possible to write the Status Register, regardless of whether the pin Write Protect  $(\overline{W})$  is driven high or low.

When the SRWD bit is written to 1, two cases have to be considered, depending on the state of the  $\overline{W}$  input pin:

- Case 1: if pin  $\overline{W}$  is driven high, it is possible to write the Status Register.

- Case 2: if pin W is driven low, it is not possible to write the Status Register (WRSR is discarded) and therefore SRWD,BP1,BP0 bits cannot be changed (the size of the protected memory block defined by BP1,BP0 bits is frozen).

Case 2 can be entered in either sequence:

- Writing SRWD bit to 1 after driving pin W low, or

- Driving pin W low after writing SRWD bit to 1.

The only way to exit Case 2 is to pull pin  $\overline{W}$  high.

Note: if pin W is permanently tied high, the Status Register cannot be write-protected.

The protection features of the device are summarized in Table 4.

SRWD bit

W signal

Status

0

X

Status Register is writable.

1

1

0

Status Register is write-protected.

Table 4. Protection modes

## 3.5 Identification page

The M95512-DRE offers an Identification page (128 bytes) in addition to the 512 Kbit memory. The Identification page contains two fields:

- Device identification: the three first bytes are programmed by STMicroelectronics with the Device identification code, as shown in *Table 5*.

- Application parameters: the bytes after the Device identification code are available for application specific data.

Operating features M95512-DRE

Note:

If the end application does not need to read the Device identification code, this field can be overwritten and used to store application-specific data. Once the application-specific data are written in the Identification page, the whole Identification page should be permanently locked in Read-only mode.

The Read, Write, Lock Identification Page instructions are detailed in Section 4: Instructions.

Table 5. Device identification bytes

| Address in Identification page | Content              | Value          |  |  |  |  |

|--------------------------------|----------------------|----------------|--|--|--|--|

| 00h                            | ST Manufacturer code | 20h            |  |  |  |  |

| 01h                            | SPI Family code      | 00h            |  |  |  |  |

| 02h                            | Memory Density code  | 10h (512 Kbit) |  |  |  |  |

### 4 Instructions

Each command is composed of bytes (MSBit transmitted first), initiated with the instruction byte, as summarized in *Table 6*.

If an invalid instruction is sent (one not contained in *Table 6*), the device automatically enters a Wait state until deselected.

Table 6. Instruction set

| Instruction | Description                                      | Instruction format |  |  |

|-------------|--------------------------------------------------|--------------------|--|--|

| WREN        | Write Enable                                     | 0000 0110          |  |  |

| WRDI        | Write Disable                                    | 0000 0100          |  |  |

| RDSR        | Read Status Register                             | 0000 0101          |  |  |

| WRSR        | Write Status Register                            | 0000 0001          |  |  |

| READ        | Read from Memory Array                           | 0000 0011          |  |  |

| WRITE       | Write to Memory Array                            | 0000 0010          |  |  |

| RDID        | Read Identification Page                         | 1000 0011          |  |  |

| WRID        | Write Identification Page                        | 1000 0010          |  |  |

| RDLS        | Reads the Identification Page lock status.       | 1000 0011          |  |  |

| LID         | Locks the Identification page in read-only mode. | 1000 0010          |  |  |

For read and write commands to memory array and Identification Page, the address is defined by two bytes as explained in *Table 7*.

Table 7. Significant bits within the two address bytes<sup>(1)</sup>

| Instructions     | MSB Address byte |     |     |     |     |     |    | LSB Address byte |    |    |    |    |    |    |    |    |

|------------------|------------------|-----|-----|-----|-----|-----|----|------------------|----|----|----|----|----|----|----|----|

| ilistructions    | b15              | b14 | b13 | b12 | b11 | b10 | b9 | b8               | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 |

| READ or<br>WRITE | A15              | A14 | A13 | A12 | A11 | A10 | A9 | A8               | A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 |

| RDID or<br>WRID  | 0                | 0   | 0   | 0   | 0   | 0   | 0  | 0                | 0  | A6 | A5 | A4 | A3 | A2 | A1 | A0 |

| RDLS or<br>LID   | 0                | 0   | 0   | 0   | 0   | 1   | 0  | 0                | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

<sup>1.</sup> A: Significant address bit.

Instructions M95512-DRE

### 4.1 Write Enable (WREN)

The WREN instruction must be decoded by the device before a write instruction (WRITE, WRSR, WRID or LID).

As shown in *Figure 5*, to send this instruction to the device, Chip Select  $(\overline{S})$  is driven low, the bits of the instruction byte are shifted in (MSB first) on Serial Data Input (D) after what the Chip Select  $(\overline{S})$  input is driven high and the WEL bit is set (Status Register bit).

c Instruction

D High Impedance

aiv02281g

Figure 5. Write Enable (WREN) sequence

### 4.2 Write Disable (WRDI)

One way of resetting the WEL bit (in the Status Register) is to send a Write Disable instruction to the device.

As shown in *Figure 6*, to send this instruction to the device, Chip Select  $(\overline{S})$  is driven low, and the bits of the instruction byte are shifted in (MSB first), on Serial Data Input (D), after what the Chip Select  $(\overline{S})$  input is driven high and the WEL bit is reset (Status Register bit).

If a Write cycle is currently in progress, the WRDI instruction is decoded and executed and the WEL bit is reset to 0 with no effect on the ongoing Write cycle.

Figure 6. Write Disable (WRDI) sequence

577

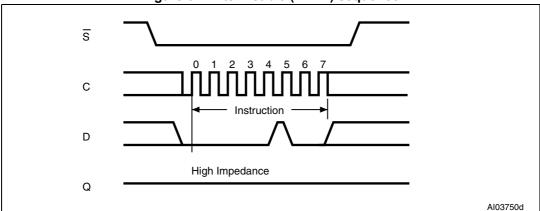

### 4.3 Read Status Register (RDSR)

The Read Status Register (RDSR) instruction is used to read the content of the Status Register.

As shown in *Figure 7*, to send this instruction to the device, Chip Select  $(\overline{S})$  is first driven low. The bits of the instruction byte are shifted in (MSB first) on Serial Data Input (D), the Status Register content is then shifted out (MSB first) on Serial Data Output (Q).

If Chip Select  $(\overline{S})$  continues to be driven low, the Status Register content is continuously shifted out.

The Status Register can always be read, even if a Write cycle (t<sub>W</sub>) is in progress. The Status Register functionality is detailed in *Section 3.4.2: Status Register and data protection*.

Figure 7. Read Status Register (RDSR) sequence

Instructions M95512-DRE

### 4.4 Write Status Register (WRSR)

The Write Status Register (WRSR) instruction allows new values to be written to the Status Register. Before it can be accepted, a Write Enable (WREN) instruction must previously have been executed.

The Write Status Register (WRSR) instruction is entered (MSB first) by driving Chip Select  $(\overline{S})$  low, sending the instruction code followed by the data byte on Serial Data input (D), and driving the Chip Select  $(\overline{S})$  signal high.

The contents of the SRWD and BP1, BP0 bits are updated after the completion of the WRSR instruction, including the Write cycle  $(t_W)$ .

The Write Status Register (WRSR) instruction has no effect on the b6, b5, b4, b1 and b0 bits in the Status Register (see *Table 2: Status Register format*).

The Status Register functionality is detailed in *Section 3.4.2: Status Register and data protection*.

The instruction is not accepted, and is not executed, if a Write cycle is currently in progress.

### 4.5 Read from Memory Array (READ)

The READ instruction is used to read the content of the memory.

As shown in *Figure 9*, to send this instruction to the device, Chip Select  $(\overline{S})$  is first driven low.

The bits of the instruction byte and address bytes are shifted in (MSB first) on Serial Data Input (D) and the addressed data byte is then shifted out (MSB first) on Serial Data Output (Q). The first addressed byte can be any byte within any page.

If Chip Select (S) continues to be driven low, the internal address register is automatically incremented, and the next byte of data is shifted out. The whole memory can therefore be read with a single READ instruction.

When the highest address is reached, the address counter rolls over to zero, allowing the Read cycle to be continued indefinitely.

The Read cycle is terminated by driving Chip Select  $(\overline{S})$  high at any time when the data bits are shifted out on Serial Data Output (Q).

The instruction is not accepted, and is not executed, if a Write cycle is currently in progress.

Depending on the memory size, as shown in *Table* 7, the most significant address bits are Don't Care.

Instructions M95512-DRE

### 4.6 Write to Memory Array (WRITE)

The WRITE instruction is used to write new data in the memory.

As shown in *Figure 10*, to send this instruction to the device, Chip Select  $(\overline{S})$  is first driven low. The bits of the instruction byte, address bytes, and at least one data byte are then shifted in (MSB first), on Serial Data Input (D). The instruction is terminated by driving Chip Select  $(\overline{S})$  high at a data byte boundary. *Figure 10* shows a single byte write.

Figure 10. Byte Write (WRITE) sequence

1. Depending on the memory size, as shown in Table 7, the most significant address bits are Don't Care.

A Page write is used to write several bytes inside a page, with a single internal Write cycle.

For a Page write, Chip Select  $(\overline{S})$  has to remain low, as shown in *Figure 11*, so that the next data bytes are shifted in. Each time a new data byte is shifted in, the least significant bits of the internal address counter are incremented. If the address counter exceeds the page boundary (the page size is 128 bytes), the internal address pointer rolls over to the beginning of the same page where next data bytes will be written. If more than 128 bytes are received, only the last 128 bytes are written.

For both Byte write and Page write, the self-timed Write cycle starts from the rising edge of Chip Select (S), and continues for a period  $t_W$  (as specified in *Table 13*).

The instruction is discarded, and is not executed, under the following conditions:

- if a Write cycle is already in progress

- if the addressed page is in the region protected by the Block Protect (BP1 and BP0) bits

- if one of the conditions defined in Section 3.4.1 is not satisfied

Note:

The self-timed Write cycle  $t_W$  is internally executed as a sequence of two consecutive events: [Erase addressed byte(s)], followed by [Program addressed byte(s)]. An erased bit is read as "0" and a programmed bit is read as "1".

20/42 DocID027432 Rev 2

Figure 11. Page Write (WRITE) sequence

1. Depending on the memory size, as shown in *Table 7*, the most significant address bits are Don't Care.

Instructions M95512-DRE

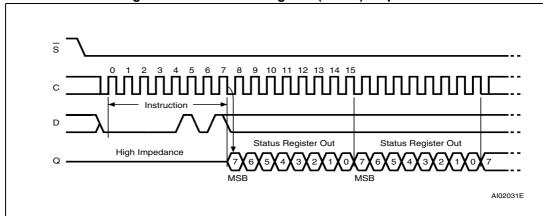

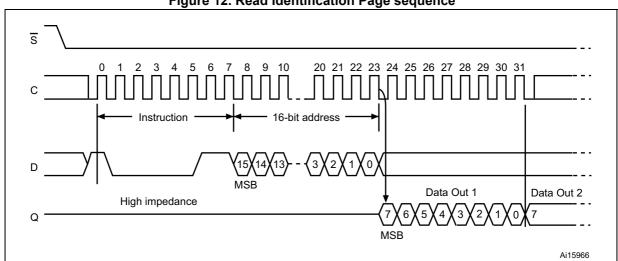

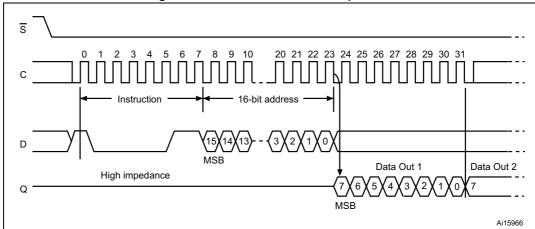

#### Read Identification Page (RDID) 4.7

The Read Identification Page instruction is used to read the Identification Page (additional page of 128 bytes which can be written and later permanently locked in Read-only mode).

The Chip Select  $(\overline{S})$  signal is first driven low, the bits of the instruction byte and address bytes are then shifted in (MSB first) on Serial Data input (D). Address bit A10 must be 0 and the other upper address bits are Don't Care (it might be easier to define these bits as 0, as shown in Table 7). The data byte pointed to by the lower address bits [A6:A0] is shifted out (MSB first) on Serial Data output (Q).

The first byte addressed can be any byte within the identification page.

If Chip Select (S) continues to be driven low, the internal address register is automatically incremented and the byte of data at the new address is shifted out.

Note that there is no roll over feature in the Identification Page. The address of bytes to read must not exceed the page boundary.

The read cycle is terminated by driving Chip Select  $(\overline{S})$  high. The rising edge of the Chip Select  $(\overline{S})$  signal can occur at any time when the data bits are shifted out.

The instruction is not accepted, and is not executed, if a Write cycle is currently in progress.

Figure 12. Read Identification Page sequence

The first three bytes of the Identification page offer information about the device itself. Please refer to Section 3.5: Identification page for more information.

DocID027432 Rev 2

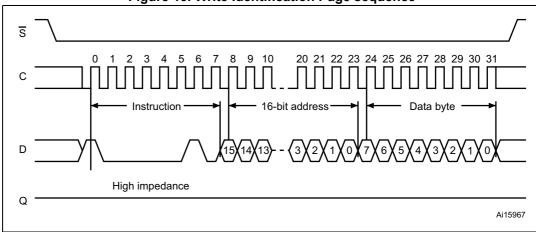

## 4.8 Write Identification Page (WRID)

The Write Identification Page instruction is used to write the Identification Page (additional page of 128 bytes which can also be permanently locked in Read-only mode).

The Chip Select signal  $\overline{(S)}$  is first driven low, and then the bits of the instruction byte, address bytes, and at least one data byte are shifted in (MSB first) on Serial Data input (D). Address bit A10 must be 0 and the other upper address bits are Don't Care (it might be easier to define these bits as 0, as shown in *Table 7*). The lower address bits [A6:A0] define the byte address inside the identification page.

The self-timed Write cycle starts from the rising edge of Chip Select  $(\overline{S})$ , and continues for a period  $t_W$  (as specified in *Table 13*).

Figure 13. Write Identification Page sequence

Note:

The first three bytes of the Identification page offer the Device Identification code (Please refer to Section 3.5: Identification page for more information). Using the WRID command on these first three bytes overwrites the Device Identification code.

The instruction is discarded, and is not executed, under the following conditions:

- If a Write cycle is already in progress

- If the Block Protect bits (BP1,BP0) = (1,1)

- If one of the conditions defined in Section 3.4.1: Protocol control is not satisfied.

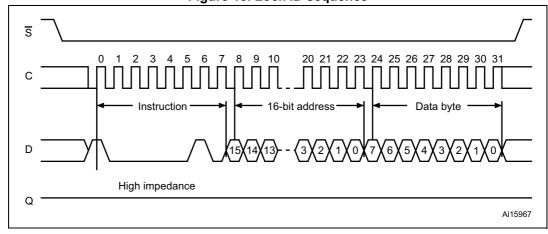

## 4.9 Read Lock Status (RDLS)

The Read Lock Status instruction is used to read the lock status.

To send this instruction to the device, Chip Select  $(\overline{S})$  first has to be driven low. The bits of the instruction byte and address bytes are then shifted in (MSB first) on Serial Data input (D). Address bit A10 must be 1; all other address bits are Don't Care (it might be easier to define these bits as 0, as shown in *Table 7*). The Lock bit is the LSB (Least Significant Bit) of the byte read on Serial Data output (Q). It is at '1' when the lock is active and at '0' when the lock is not active. If Chip Select  $(\overline{S})$  continues to be driven low, the same data byte is shifted out.

The read cycle is terminated by driving Chip Select  $(\overline{S})$  high. The instruction sequence is shown in *Figure 14*.

Instructions M95512-DRE

The Read Lock Status instruction is not accepted and not executed if a Write cycle is currently in progress.

Figure 14. Read Lock Status sequence

### 4.10 Lock Identification Page (LID)

The Lock Identification Page (LID) command is used to permanently lock the Identification Page in Read-only mode.

The LID instruction is issued by driving Chip Select (S) low, sending (MSB first) the instruction code, the address and a data byte on Serial Data input (D), and driving Chip Select (S) high. In the address sent, A10 must be equal to 1. All other address bits are Don't Care (it might be easier to define these bits as 0, as shown in Table 7). The data byte sent must be equal to the binary value xxxx xx1x, where x = Don't Care. The LID instruction is terminated by driving Chip Select (S) high at a data byte boundary, otherwise, the instruction is not executed.

Figure 15. Lock ID sequence

Driving Chip Select (S) high at a byte boundary of the input data triggers the self-timed Write cycle which duration is t<sub>W</sub> (specified in *Table 13*). The instruction sequence is shown in *Figure 15*.

57

The instruction is discarded, and is not executed, under the following conditions:

- If a Write cycle is already in progress

- If the Block Protect bits (BP1,BP0) = (1,1)

- If one of the conditions defined in Section 3.4.1: Protocol control is not satisfied.