Der M73XX

Parameters of the DM73XX are programmable via the I<sup>2</sup>C bus and can be changed by a user at any time during product development and deployment.

- RoHS compliant for all six substances

- Compatible with both lead-free and standard reflow processes

- Programs, controls, and manages up to 32 independent dPOL converters via an industry standard I<sup>2</sup>C interface (both 100 kHz and 400 kHz)

- JTAG IEEE 1149.1 compliant programming interface

- Controls and monitors industry standard power supplies and other peripheral devices (fans, etc)

- Programs output voltage, protections, optimal voltage positioning, turnon and turn-off delays and slew rates, switching frequency, interleave (phase shift), and feedback loop compensation of the d-pwer<sup>™</sup> POL converters

- User friendly GUI interface for programming, monitoring, and performance simulation

- Four independent OK lines for flexible fault management and fast fault propagation

- Four interrupt inputs with programmable hot swap support capabilities

- Intermediate bus voltage monitoring and protection

- AC Fail input

- Non-volatile system configuration data memory

- 1K Byte of user accessible non-volatile memory

- Control of industry standard DC-DC front ends

- Crowbar output to trigger the optional crowbar protection

- Run-time counter

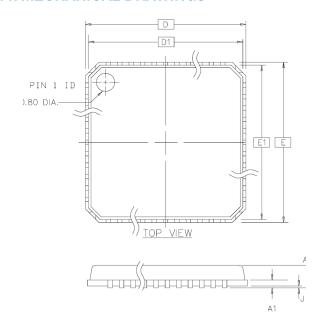

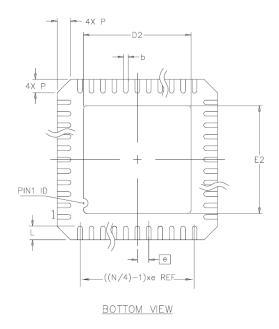

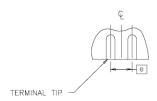

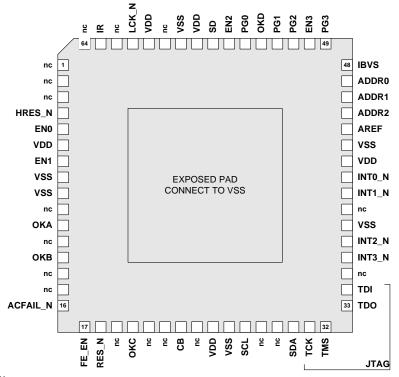

- Small footprint semiconductor industry standard QFN64 package: 9x9 mm

- Wide industrial operating temperature range

**Asia-Pacific** +86 755 298 85888 **Europe, Middle East** +353 61 225 977

North America +1 866 513 2839

### 1. MODEL SELECTION

| DPM TYPE | NUMBER OF D-PWER <sup>™</sup> POLS<br>AND AUXILIARY DEVICES<br>THAT CAN BE CONTROLLED | ACTIVE<br>ADDRESSES | NUMBER OF<br>GROUPS | NUMBER OF<br>INTERRUPTS | NUMBER OF<br>PARALLEL<br>BUSES | NUMBER OF<br>AUXILIARY<br>DEVICES |

|----------|---------------------------------------------------------------------------------------|---------------------|---------------------|-------------------------|--------------------------------|-----------------------------------|

| DM7304G  | 4                                                                                     | 0003                | 2                   | 2                       | 2                              | 4                                 |

| DM7308G  | 8                                                                                     | 0007                | 2                   | 2                       | 4                              | 4                                 |

| DM7316G  | 16                                                                                    | 0015                | 3                   | 3                       | 4                              | 4                                 |

| DM7332G  | 32                                                                                    | 0031                | 4                   | 4                       | 8                              | 4                                 |

### 2. STANDARD 5-DIGIT IDENTIFIERS

| DPM TYPE | DPM PRELOADED WITH DEFAULT CONFIGURATION FILE | DPM CONFIGURED FOR JTAG PROGRAMMING | PACKAGING<br>OPTIONS |

|----------|-----------------------------------------------|-------------------------------------|----------------------|

| DM7304G  | 65511                                         | 65515                               | B1, R100             |

| DM7308G  | 65512                                         | 65516                               | B1, R100             |

| DM7316G  | 65513                                         | 65517                               | B1, R100             |

| DM7332G  | 65514                                         | 65518                               | B1, R100             |

### 3. ABSOLUTE MAXIMUM RATINGS

Stresses beyond those listed may cause permanent damage to the DPM. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Functional operation of the DPM at absolute maximum ratings or conditions beyond those indicated in the operational sections of this specification is not implied.

| PARAMETER                              | CONDITIONS / DESCRIPTION | MIN  | MAX     | UNITS |

|----------------------------------------|--------------------------|------|---------|-------|

| Ambient Temperature Range              |                          | -40  | 85      | °C    |

| Storage Temperature (Ts)               |                          | -55  | 150     | °C    |

| Junction Temperature (T <sub>J</sub> ) |                          |      | 125     | °C    |

| Input Voltage                          | VDD pin                  | -0.3 | 3.6     | VDC   |

| Input Voltage                          | Any pin other than VDD   | -0.5 | VDD+0.5 | VDC   |

| Pin Current                            | DC                       |      | 40      | mA    |

### 4. MECHANICAL SPECIFICATIONS

| PARAMETER                  | CONDITIONS/DESCRIPTION  | MIN | NOM          | MAX | UNITS |

|----------------------------|-------------------------|-----|--------------|-----|-------|

| Peak Reflow Temperature    | 40 sec maximum duration |     |              | 260 | °C    |

| Lead Plating               |                         | 11  | 00% matte ti | n   |       |

| Moisture Sensitivity Level | JEDEC J-STD-020C        |     | 3            |     |       |

### 5. RELIABILITY SPECIFICATIONS

| PARAMETER                     | CONDITIONS/DESCRIPTION                     | MIN   | NOM | MAX | UNITS                    |

|-------------------------------|--------------------------------------------|-------|-----|-----|--------------------------|

| Failure Rate                  | Demonstrated at 55°C, 60% Confidence Level | 2.26  |     |     | FIT                      |

| Non-Volatile Memory Endurance | -40°C to 85°C ambient                      | 10000 |     |     | Read-<br>Write<br>cycles |

### 6. ELECTRICAL SPECIFICATIONS

Specifications apply at VDD from 3 V to 3.6 V, ambient temperature from -40°C to 85°C, and utilizing proper decoupling as shown in Figure 3 unless otherwise noted.

### **6.1 POWER SPECIFICATIONS**

| PARAMETER                | CONDITIONS / DESCRIPTION                         | MIN | NOM  | MAX  | UNITS |

|--------------------------|--------------------------------------------------|-----|------|------|-------|

| Input Supply Voltage     | VDD pin                                          | 3.0 |      | 3.6  | VDC   |

| Undervoltage Lockout     | Hardware reset is triggered below this threshold | 2.3 | 2.5  | 2.7  | VDC   |

| Input Supply Current     | VDD pin = $3.3 \text{ V}$                        |     | 12   | 20   | mA    |

| VREF voltage             | AREF pin                                         | 2.3 | 2.56 | 2.7  | VDC   |

| IBVS input voltage range |                                                  | GND |      | VREF | VDC   |

| IBVS input resistance    |                                                  |     | 100  |      | ΜΩ    |

### **6.2 FEATURE SPECIFICATIONS**

| PARAMETER                           | CONDITIONS/DESCRIPTION                                                               | MIN | NOM  | MAX  | UNITS            |

|-------------------------------------|--------------------------------------------------------------------------------------|-----|------|------|------------------|

| Intermediate Voltage Bus Protection | s                                                                                    |     |      |      |                  |

| Overvoltage Protection Threshold    | With external 5.7:1 ratio divider                                                    | IBV |      | 14.6 | V                |

| Undervoltage Protection Threshold   | With external 5.7:1 ratio divider                                                    | 0   |      | IBV  | V                |

| Threshold Hysteresis                | With external 5.7; 1 ratio divider.  Symmetrical relative to average threshold value |     | ±114 |      | mV               |

| Accuracy of Protection Thresholds   | Internal voltage reference, 1% resistive divider                                     | -10 |      | 10   | %V <sub>TH</sub> |

| Internal ADC Conversion Error       | With external 5.7:1 ratio divider                                                    | -43 |      | 43   | mV               |

| Front End Enable (FE_EN)            |                                                                                      |     |      |      |                  |

| V <sub>FE_EN</sub>                  | Front End logic level enabled                                                        |     | High |      |                  |

| V <sub>FE_EN</sub>                  | Front End logic level disabled                                                       |     | Low  |      |                  |

| Isrc                                | Source Current, $V_{FE\_EN} = V_{DD}$ -0.5 V                                         | 5   |      |      | mA               |

| Isink                               | Sink Current, V <sub>FE_EN</sub> = 0.5V                                              | 5   |      |      | mA               |

| Crowbar (CB)                        |                                                                                      |     |      |      |                  |

| V <sub>CB</sub>                     | Crowbar Enable                                                                       |     | High |      |                  |

| $V_{CB}$                            | Crowbar Disable                                                                      |     | Low  |      |                  |

| Isrc                                | Source Current, $V_{CB} = V_{DD}$ -0.5 V                                             | 5   |      |      | mA               |

| Isink                               | Sink Current, $V_{CB} = 0.5 \text{ V}$                                               | 5   |      |      | mA               |

| Тсв                                 | Duration of Enabling Pulse                                                           |     | 1    |      | ms               |

|                                     |                                                                                      |     |      |      |                  |

### **6.3 SIGNAL SPECIFICATIONS**

| PARAMETER SYNC/DATA Line      | CONDITIONS / DESCRIPTION                               | MIN      | NOM  | MAX      | UNITS            |

|-------------------------------|--------------------------------------------------------|----------|------|----------|------------------|

| SDpu                          | SD pull up resistor                                    |          | 5    |          | kΩ               |

| SDthrL                        | SD input low voltage threshold                         | 0.31·VDD |      | 0.52·VDD | V                |

| SDthrH                        | SD input high voltage threshold                        | 0.45·VDD |      | 0.81·VDD | V                |

| SDhys                         | SD input hysteresis                                    | 0.37     |      | 1.1      | V                |

| SDsink                        | SD sink capability (V <sub>SD</sub> = 0.5 V)           |          |      | 30       | mA               |

| Freq_sd                       | Clock frequency                                        | 450      |      | 550      | kHz              |

| Tsynq                         | Sync pulse duration                                    | 22       |      | 28       | % of clock cycle |

| ТО                            | Data = 0 pulse duration                                | 72       |      | 78       | % of clock cycle |

| Interrupt Inputs (INT_N[3:0]) |                                                        |          |      |          | Cycle            |

| Rpu3                          | Pull up resistor                                       |          | 30   |          | kΩ               |

| VthrL3                        | Input low voltage threshold                            | 0.31·VDD |      | 0.52·VDD | V                |

| VthrH3                        | Input high voltage threshold                           | 0.45·VDD |      | 0.81·VDD | V                |

| Vhys3                         | Input hysteresis                                       | 0.37     |      | 1.1      | V                |

| ADDR[3:0], ACFAIL_N, RES_N, L | LCK_N, PG[3:0] Inputs                                  |          |      |          |                  |

| Rpu1                          | Pull up resistor                                       | 20       |      | 50       | kΩ               |

| VthrL1                        | Input low voltage                                      | -0.5     |      | 0.2·VDD  | V                |

| VthrH1                        | Input high voltage                                     | 0.7·VDD  |      | VDD+0.5  | V                |

| HRES_N Input                  |                                                        |          |      |          |                  |

| Rpu2                          | HRES_N pull up resistor (with series diode, see note1) | 30       |      | 60       | kΩ               |

| VthrL2                        | HRES_N input low voltage                               | -0.5     |      | 0.2·VDD  | V                |

| VthrH2                        | HRES_N input high voltage                              | 0.9·VDD  |      | VDD+0.5  | V                |

| Inputs/Outputs (OK_A, OK_B, O | K_C, OK_D)                                             |          |      |          |                  |

| OKpu                          | OK pull up resistor                                    |          | 5    |          | kΩ               |

| OKthrL                        | OK input low voltage threshold                         | 0.31·VDD |      | 0.52·VDD | V                |

| OKthrH                        | OK input high voltage threshold                        | 0.45·VDD |      | 0.81·VDD | V                |

| OKhys                         | OK input hysteresis                                    | 0.37     |      | 1.1      | V                |

| OKsink                        | OK sink capability (V <sub>OK</sub> = 0.5 V)           |          |      | 30       | mA               |

| Enable Outputs (EN[3:0])      |                                                        |          |      |          |                  |

| V <sub>EN</sub>               | EN logic level enabled                                 |          | High |          |                  |

| V <sub>EN</sub>               | EN logic level disabled                                |          | Low  |          |                  |

| V <sub>EN</sub> H             | EN output high voltage ( $I_{OH} = -10 \text{ mA}$ )   | VDD-0.6  |      |          | V                |

| V <sub>EN</sub> L             | EN output low voltage (I <sub>OL</sub> = 5 mA)         |          |      | 0.5      | V                |

|                               |                                                        |          |      |          |                  |

$<sup>^{1}</sup>$  HRES\_N Input - Because the input does not have an internal ESD protection diode connected to VDD, the user needs to add an external diode between the HRES\_N and VDD pins as shown in Figure .

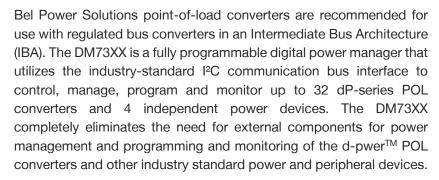

### 6.4 I<sup>2</sup>C INTERFACE

| PARAMETER                            | CONDITIONS/DESCRIPTION                                     | MIN                               | NOM | MAX                              | UNITS |

|--------------------------------------|------------------------------------------------------------|-----------------------------------|-----|----------------------------------|-------|

| ViL                                  | Input low voltage                                          | -0.5                              |     | 0.3·VDD                          | V     |

| ViH                                  | Input high voltage                                         | 0.7·VDD                           |     | VDD+0.5                          | V     |

| Vhys                                 | Input hysteresis                                           | 0.05·VDD                          |     |                                  | V     |

| VoL                                  | Output low voltage, Isink=3mA                              | 0                                 |     | 0.4                              | V     |

| t <sub>r</sub>                       | Rise time for SDA and SCL                                  | 20+0.1C <sub>b</sub> <sup>2</sup> |     | 300                              | ns    |

| t <sub>of</sub>                      | Output fall time from ViHmin to ViLmax                     | 20+0.1C <sub>b</sub> <sup>2</sup> |     | 250                              | ns    |

| li                                   | Input current each I/O pin, $0.1V_{DD} < V_i < 0.9 V_{DD}$ | -10                               |     | 10                               | μΑ    |

| Ci                                   | Capacitance for each I/O pin                               |                                   |     | 10                               | pF    |

| fscL                                 | SCL clock frequency                                        | 0                                 |     | 400                              | kHz   |

| Standard-Mode I²C (fscl ≤ 100kHz)    |                                                            |                                   |     |                                  |       |

| R <sub>PU</sub>                      | External pull-up resistor                                  | 1                                 |     | 1000/C <sub>b</sub> <sup>2</sup> | kΩ    |

| thdsta                               | Hold time (repeated) START condition                       | 4.0                               |     |                                  | μS    |

| t <sub>LOW</sub>                     | Low period of the SCL clock                                | 4.7                               |     |                                  | μS    |

| t <sub>ніGН</sub>                    | High period of the SCL clock                               | 4.0                               |     |                                  | μs    |

| tsusta                               | Setup time for a repeated START condition                  | 4.7                               |     |                                  | μs    |

| thddat                               | Data hold time                                             | 0                                 |     | 3.45                             | μs    |

| tsudat                               | Data setup time                                            | 250                               |     |                                  | ns    |

| tsustd                               | Setup time for STOP condition                              | 4.0                               |     |                                  | μS    |

| tsuf                                 | Bus free time between a STOP and START condition           | 4.7                               |     |                                  | μs    |

| Fast-Mode I²C (100kHz < fscL≤ 400kHz | <del>;</del> )                                             |                                   |     |                                  |       |

| R <sub>PU</sub>                      | External pull-up resistor                                  | 1                                 |     | 300/C <sub>b</sub> <sup>2</sup>  | kΩ    |

| thdsta                               | Hold time (repeated) START condition                       | 0.6                               |     |                                  | μs    |

| t <sub>LOW</sub>                     | Low period of the SCL clock                                | 1.3                               |     |                                  | μs    |

| tнıан                                | High period of the SCL clock                               | 0.6                               |     |                                  | μs    |

| tsusta                               | Setup time for a repeated START condition                  | 0.6                               |     |                                  | μs    |

| thddat                               | Data hold time                                             | 0                                 |     | 0.9                              | μs    |

| t <sub>SUDAT</sub>                   | Data setup time                                            | 100                               |     |                                  | ns    |

| tsustd                               | Setup time for STOP condition                              | 0.6                               |     |                                  | μs    |

| tsur                                 | Bus free time between a STOP and START condition           | 1.3                               |     |                                  | μs    |

$<sup>^2\,\</sup>mbox{C}_{\mbox{\scriptsize b}}$  – bus capacitance in pF, typically from 10 pF to 400 pF

Figure 1. I<sup>2</sup>C Timing Parameters

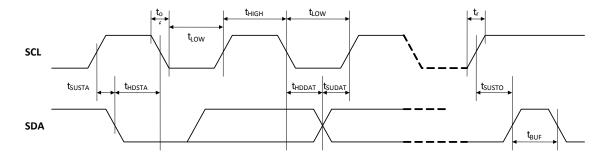

### 7. TYPICAL APPLICATION

Figure 2. Typical Application Schematic of Multiple Output System with Digital Power Manager and I<sup>2</sup>C Interface

The schematic of a typical application of a DM73XX digital power manager (DPM) is shown in Figure 3. The system includes four groups of d-pwer Point Of Load converters (POLs). A group is defined as one or more POL converters interconnected via OK pins. Grouping of the POLs enables users to program advanced fault management schemes and define margining functions, monitoring, start-up behavior, and reporting conventions.

All d-pwer POL converters are connected to the DPM and to each other via a single-wire synchronization/data (SD) line. The line provides synchronization of all POL converters to the master clock generated by the DPM and simultaneously carries bidirectional data transfer between POL converters and the DPM. The DPM communicates via the I<sup>2</sup>C bus with the host system and/or the Graphical User Interface.

In this application, besides POL converters, the DPM also controls and monitors two auxiliary devices – a Voltage Regulation Module (VRM) and a Low Dropout Regulator (LDO). While these devices are not d-pwer compliant and may not even be manufactured by Bel Power Solutions, they are integrated into the system by communicating with the DPM via their Enable pins connected to ENX outputs of the DPM. In addition, the DPM monitors status of the auxiliary devices via its PGX inputs connected to Power Good and Error Flag outputs of the auxiliary devices. The DPM can control and monitor four or more independent auxiliary devices. The DPM can also trigger an optional crowbar circuit and provide undervoltage and overvoltage protections of the intermediate bus voltage. In addition, the DPM can be controlled by a host system via the interrupt inputs, RES\_N and the ACFAIL\_N inputs.

### 8. DESCRIPTION

The DM73XX series DPMs perform translation between the I<sup>2</sup>C interface connected to a host system or the Graphical User Interface and the SD communication bus connected to dPOL converters. In addition, DPMs carry out programming, monitoring, data storage, POL group management, hot-swap control, protection, and control and monitoring of auxiliary devices. The DPMs can be controlled via the GUI or directly via the I<sup>2</sup>C bus by using specific commands described in the "DPM Programming Manual".

### **8.1 DPM MEMORY**

The DPM memory consists of RAM and non-volatile memory (Flash). The RAM is used for programming operations and manipulation of the various blocks of configuration, setup, status, and monitoring registers. Non-volatile memory is used to store programming and configuration data. Flash memory holds DPM set-up registers, POL set-up registers, monitoring data, and user memory data. Setup registers for the DPM and the POL converters are protected by CRCs that are checked during programming of POL converters and at the power-up of the DPM.

The LCK\_N pin and the write protection register WP limit the write access to the memory blocks in the DPM and POL converters. The WP register content is defaulted to write protect upon powering up the DPM.

### 8.1.1 WRITE PROTECTION

There are hardware-based and software-based memory write protections. The hardware protection takes precedence over the software protection.

### 8.1.1.1 HARDWARE PROTECTION

The LCK\_N pin enables the hardware memory write protection. If the pin is pulled low, the hardware lock is active and the memory blocks are then read-only. I<sup>2</sup>C write commands to the DPM return an error code (0x00). The write commands to the POL converters bypassing the DPM are also disabled. If the pin is left floating, the hardware lock is disabled and the software write protection is active.

### 8.1.1.2 SOFTWARE PROTECTION

Software write protection allows users to protect the various memory blocks from being overwritten through the I<sup>2</sup>C bus. At the power-up the WP register is defaulted to write protect.

Software write protection can be disabled by checking appropriate boxes in the Write Protection subsection of the DPM/Program/Advanced dialog shown in Figure 4 or via the I<sup>2</sup>C bus by writing directly into the register. Write protections are automatically restored when the DPM's input power is recycled.

Figure 3. GUI DPM Advanced Programming Dialog

### 8.1.2 DPM REGISTERS

The DPM setup registers occupy 70 bytes and contain all necessary information to set up the DPM functionality, define POL converters and Auxiliary Devices, group membership and behavior, margining, interrupt configurations, etc. they DPM registers are listed in. The table relates to the DPM model number DM7332 capable of supporting up to 32 POL converters. For other DPM models some of the registers and/or bits in the registers are not activated depending on the number of supported POLs/Groups/Interrupts/Parallel Buses for the specific DPM. Writing into an unsupported register or bit will have no effect, reading from an unsupported register or bit will return an error code (0x00).

| ADDRESS<br>OFFSET <sup>3</sup> | REGISTER<br>NAME | CONTENT                           | REGISTER TYPE | USER<br>ACCESS | WRITE<br>PROTECT | INITIAL<br>VALUE         |

|--------------------------------|------------------|-----------------------------------|---------------|----------------|------------------|--------------------------|

| 0x00                           | GD1[3:0]         | Group Definition Register 1       | Static        | R/W            | yes              | 0x00000000               |

| 0x04                           | GD2[3:0]         | Group Definition Register 2       | Static        | R/W            | yes              | 0x00000000               |

| 0x08                           | GAC              | Group A Configuration             | Static        | R/W            | yes              | 0x00                     |

| 0x09                           | GBC              | Group B Configuration             | Static        | R/W            | yes              | 0x00                     |

| 0x0A                           | GCC              | Group C Configuration             | Static        | R/W            | yes              | 0x00                     |

| 0x0B                           | GDC              | Group D Configuration             | Static        | R/W            | yes              | 0x00                     |

| 0x0C                           | FPC1             | Fault Propagation Configuration 1 | Static        | R/W            | yes              | 0x00                     |

| 0x0D                           | FPC2             | Fault Propagation Configuration 2 | Static        | R/W            | yes              | 0x00                     |

| 0x0E                           | EPC              | Error Propagation Configuration   | Static        | R/W            | yes              | 0x00                     |

| 0x0F                           | IC1              | Interrupt Configuration 1         | Static        | R/W            | yes              | 0x00                     |

| 0x10                           | IC2              | Interrupt Configuration 2         | Static        | R/W            | yes              | 0x00                     |

| 0x11                           | IBL[1:0]         | IBV Low threshold                 | Static        | R/W            | yes              | 0x00                     |

| 0x13                           | IBH[1:0]         | IBV high threshold                | Static        | R/W            | yes              | 0xFF                     |

| 0x15                           | ID[1:0]          | DPM Customer Identification       | Static        | OTP            | N/A              | 0xFFFF                   |

| 0x17                           | PB1[3:0]         | Parallel Bus Register 1           | Static        | R/W            | yes              | 0x00000000               |

| 0x1B                           | PB2[3:0]         | Parallel Bus Register 2           | Static        | R/W            | yes              | 0x00000000               |

| 0x1F                           | PB3[3:0]         | Parallel Bus Register 3           | Static        | R/W            | yes              | 0x00000000               |

| 0x23                           | PB4[3:0]         | Parallel Bus Register 4           | Static        | R/W            | yes              | 0x00000000               |

| 0x27                           | PMC              | Power Manager Configuration       | Static        | R/W            | yes              | 0x00                     |

| 0x28                           | PID[31:0]        | POL Identification Register       | Static        | R/W            | yes              | 0x00                     |

| 0x80                           | RTC[3:0]         | Run Time Counter                  | Run time      | R              | Read only        | value at last shut-down  |

| 0x84                           | PPS[3:0]         | POL Programming Status            | Run time      | R              |                  | (4x) 0x00                |

| 0x88                           | EST              | Event Status                      | Run time      | R              |                  | 0x00                     |

| 0x89                           | IBV[1:0]         | IB Voltage                        | Run time      | R              |                  | 0x00                     |

| 0x8B                           | STA              | Status of Group A                 | Run time      | R              |                  | 0x00                     |

| 0x8C                           | STB              | Status of Group B                 | Run time      | R              |                  | 0x00                     |

| 0x8D                           | STC              | Status of Group C                 | Run time      | R              |                  | 0x00                     |

| 0x8E                           | STD              | Status of Group D                 | Run time      | R              |                  | 0x00                     |

| 0x8F                           | REL[1:0]         | DPM Software Release              | Static        | R              |                  | According to<br>DPM type |

| 0x91                           | PSS[3:0]         | POL Status Summary                | Run time      | R              |                  | 0x00                     |

| 0x95                           | DPMS             | DPM Status                        | Run time      | R              |                  | 0x01                     |

| 0x96                           | WP               | Write Protection                  | Volatile      | R/W            |                  | 0x00                     |

Table 1. DPM Setup Registers

The static registers are saved in the non-volatile memory and used to store the system configuration data. The run-time registers contain status information and are evaluated during run-time. The Write Protection register WP is a volatile register that defaults to write protect at power-up.

<sup>&</sup>lt;sup>3</sup> Writing into memory locations beyond address offset 0x96 must be avoided

### 8.1.3 POL SETUP REGISTERS

Since the POL converters contain only RAM, the data defining performance parameters for each POL and Auxiliary Device, such as the output voltage, protection thresholds, feedback loop compensation, turn-on and turn-off delays, fault management settings, etc., is stored in the POL setup registers in the DPM. The POL setup registers consist of 23 data bytes and 2 CRC bytes. The Auxiliary Device setup registers occupy the same amount of bytes as a POL converter, but only 3 registers have meaningful data. The other registers should be filled with 0x00. The POL setup registers are listed in Table 2. Register significance is different in some cases between the new DP and older ZY series POLs which are still supported. Differences are in **bold** for the DP series devices.

| ADDRESS<br>OFFSET | REGISTER+)            | CONTENT                                          | ADDRESS<br>OFFSET | REGIS               | STER          | CONTENT                                                           |

|-------------------|-----------------------|--------------------------------------------------|-------------------|---------------------|---------------|-------------------------------------------------------------------|

| OFFSET            | DP7000/<br>DP8000 POL |                                                  | OFFSEI            | Z7000/<br>Z8000 POL | AUX<br>DEVICE |                                                                   |

| 00h               | PC1_x                 | Protection Configuration 1                       | 00h               | PC1_x               | EC_x          | Protection Configuration 1                                        |

| 01h               | PC2_x                 | Protection Configuration 2                       | 01h               | PC2_x               | reserved      | Protection Configuration 2                                        |

| 02h               | PC3_x                 | Protection Configuration 3                       | 02h               | PC3_x               | reserved      | Protection Configuration 3                                        |

| 03h               | TC_x                  | Tracking Configuration                           | 03h               | TC_x                | reserved      | Tracking Configuration                                            |

| 04h               | INT_x                 | Interleave Configuration and Frequency Selection | 04h               | INT_x               | reserved      | Interleave Configuration and<br>Frequency Selection               |

| 05h               | DON_x                 | Turn-On Delay                                    | 05h               | DON_x               | EON_x         | Turn-On Delay                                                     |

| 06h               | DOF_x                 | Turn-Off Delay                                   | 06h               | DOF_x               | EOF_x         | Turn-Off Delay                                                    |

| 07h               | VLC                   | Voltage Loop<br>Configuration                    | 07h               | VOS_x               | reserved      | Output Voltage Set-point                                          |

| 08h               | CLS_x                 | Current Limit Set-point                          | 08h               | CLS_x               | reserved      | Current Limit Set-point                                           |

| 09h               | DCL_x                 | Duty Cycle Limit                                 | 09h               | DCL_x               | reserved      | Duty Cycle Limit                                                  |

| 0Ah               | PC4                   | Protection Configuration<br>Register 4           | 0Ah               | B1_x                | reserved      | Dig Controller Denominator z <sup>-1</sup> Coefficient            |

| 0Bh               | V1H                   | Output Voltage Setpoint<br>1 High                | 0Bh               | B2_x                | reserved      | Dig Controller Denominator z <sup>-2</sup> Coefficient            |

| 0Ch               | V1L                   | Output Voltage Setpoint<br>1 Low                 | 0Ch               | B3_x                | reserved      | Dig Controller Denominator z <sup>-3</sup> Coefficient            |

| 0Dh               | V2H                   | Output Voltage Setpoint 2 High                   | 0Dh               | C0L_x               | reserved      | Dig Controller Numerator z <sup>0</sup> Coefficient Low Byte      |

| 0Eh               | V2L                   | Output Voltage Setpoint 2 Low                    | 0Eh               | C0H_x               | reserved      | Dig Controller Numerator z <sup>0</sup><br>Coefficient High Byte  |

| 0Fh               | V3H                   | Output Voltage Setpoint 3 High                   | 0Fh               | C1L_x               | reserved      | Dig Controller Numerator z <sup>-1</sup> Coefficient Low Byte     |

| 10h               | V3L                   | Output Voltage Setpoint<br>3 Low                 | 10h               | C1H_x               | reserved      | Dig Controller Numerator z <sup>-1</sup> Coefficient High Byte    |

| 11h               | СР                    | Controller Proportional<br>Coefficient           | 11h               | C2L_x               | reserved      | Dig Controller Numerator z <sup>-2</sup> Coefficient Low Byte     |

| 12h               | CI                    | Controller Integral<br>Coefficient               | 12h               | C2H_x               | reserved      | Dig Controller Numerator z <sup>-2</sup><br>Coefficient High Byte |

| 13h               | CD                    | Controller Derivative<br>Coefficient             | 13h               | C3L_x               | reserved      | Dig Controller Numerator z <sup>-3</sup><br>Coefficient Low Byte  |

| 14h               | CV                    | Controller Derivative<br>Roll-Off Coefficient    | 14h               | C3H_x               | reserved      | Dig Controller Numerator z <sup>-3</sup><br>Coefficient High Byte |

| 15h               | reserved              |                                                  | 15h               | reserved            | reserved      |                                                                   |

| 16h               | reserved              |                                                  | 16h               | reserved            | reserved      |                                                                   |

| 17h               | reserved              |                                                  | 17h               | reserved            | reserved      |                                                                   |

| 18h               | reserved              |                                                  | 18h               | reserved            | reserved      |                                                                   |

| 19h               | reserved              |                                                  | 19h               | reserved            | reserved      |                                                                   |

| 1Ah | reserved  |                                       | 1Ah | reserved  | reserved  |                                       |

|-----|-----------|---------------------------------------|-----|-----------|-----------|---------------------------------------|

| 1Bh | reserved  |                                       | 1Bh | reserved  | reserved  |                                       |

| 1Ch | MRH       | Margining High<br>Selection           | 1Ch | VOML_x #) | reserved  | Output Voltage Margining Low Value    |

| 1Dh | MRL       | Margining Low<br>Selection            | 1Dh | VOMH_x #) | reserved  | Output Voltage Margining High Value   |

| 1Eh | CRC0_x #) | Cyclic Redundancy<br>Check Register 0 | 1Eh | CRC0_x #) | CRC0_x #) | Cyclic Redundancy Check<br>Register 0 |

| 1Fh | CRC1_x #) | Cyclic Redundancy<br>Check Register 1 | 1Fh | CRC1_x #) | CRC1_x #) | Cyclic Redundancy Check<br>Register 1 |

#### Notes

Table 2. POL Setup Registers

### 8.1.4 MONITORING DATA

The DPMs can retrieve current, temperature, output voltage, and status information from each of the POL converters and status information only from Auxiliary Devices. Monitoring data is stored in RAM and can be accessed via the I<sup>2</sup>C bus. Monitoring registers are read only.

The monitoring data consists of 5 Bytes for each POL converter and Auxiliary Device as shown in Table 3. When the status monitoring is enabled, the ST registers get continuously updated. When the parametric monitoring is enabled, the VOH, VOL, IO, and TMP registers get continuously updated. Scaling data from the registers is specific to each DP and ZY series POL. Refer to the DM73XX Programming manual for calculation information.

| POL (    | CONVERTER                | AUXILIARY DEVICE |                 |  |  |

|----------|--------------------------|------------------|-----------------|--|--|

| Register | Content                  | Register         | Content         |  |  |

| ST       | Status Register          | ST               | Status Register |  |  |

| VOH      | Output Voltage High Byte | reserved         |                 |  |  |

| VOL      | Output Voltage Low Byte  | reserved         |                 |  |  |

| Ю        | Output Current           | reserved         |                 |  |  |

| TMP      | Temperature              | reserved         |                 |  |  |

Table 3. Monitoring Data Registers

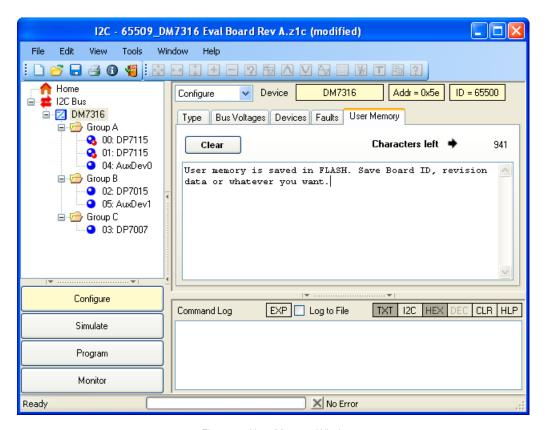

### 8.1.5 USER MEMORY

This non-volatile memory block is reserved for users' notes and not related to other functions in the DPM. It can be used to save user-specific information such as manufacturing data and location, serial number, application code, configuration file version, warranty or repair information, etc. A total of 1024 Bytes organized in 4 pages is provided. The user memory can be accessed via the GUI System Configuration window shown in Figure 8 or directly via the I<sup>2</sup>C bus using specific commands. Content of the user memory is saved into the configuration file when the file is saved. Note that this does not change the current DPM contents until the DPM is programmed with the file currently in memory.

<sup>+)</sup> x denotes the POL address [0..31]

<sup>#)</sup> not downloaded to the POL during programming

Figure 4. User Memory Window

### **8.2 AUXILIARY DEVICES**

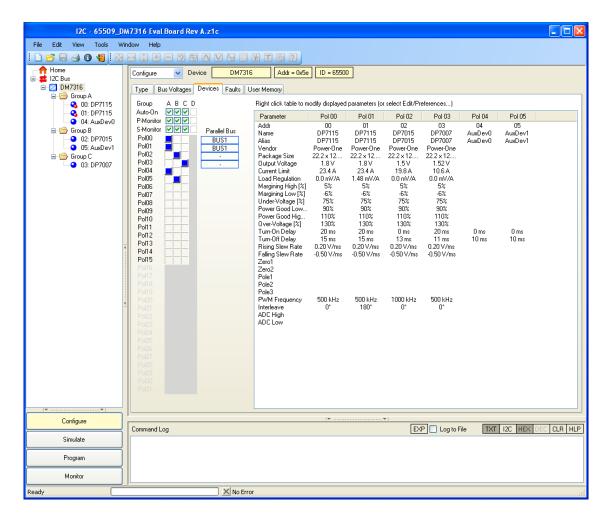

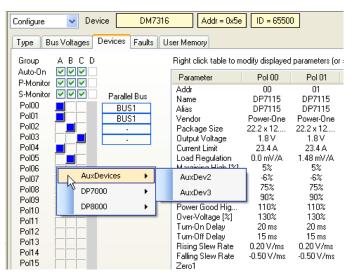

The DM73XX DPM includes all necessary circuitry to control and monitor four Auxiliary Devices. Virtually any device which has an on/off input and a monitoring output can be an Auxiliary Device. Typical examples of Auxiliary Devices include analog POL converters, linear regulators, and fans. Auxiliary Devices are controlled and monitored via the Graphical User Interface.

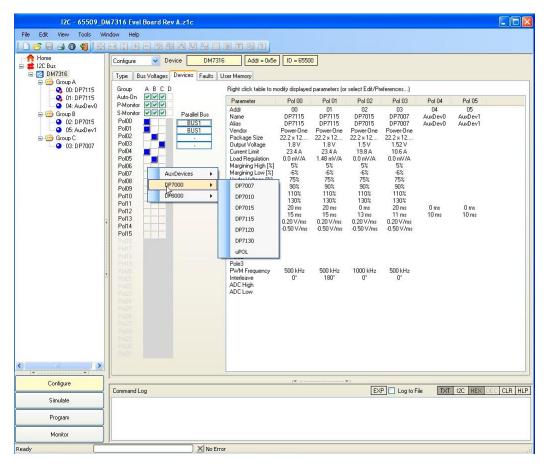

The DPM treats Auxiliary Devices as d-pwer™ POL converters: each Auxiliary Device has an address and is assigned to one of the groups as shown in Figure 8 (device at addresses 03). Turn-on and off delays can be programmed, and faults can be propagated from POL converters to the devices. Auxiliary Devices are controlled through standard group turn-on and off commands and are fully synchronized with turn-on/off timing of POL converters.

Four enable outputs EN0...EN3 control the Auxiliary Devices. Four monitoring inputs PG0...PG3 read status of the Auxiliary Devices. The enable outputs and monitoring inputs are paired together and permanently assigned to specific pins of the DPM as shown in Figure 6. Adding an AUX device is done the same way as adding a POL, select an uncommitted address and then the AUX device desired. In this example two AUX devices are already present.

Figure 5. Auxiliary Device Type Window

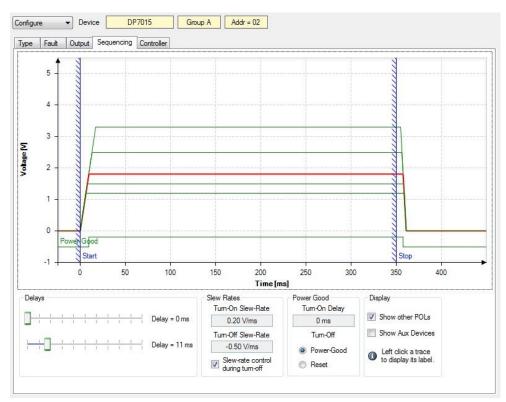

Turn-on and turn-off delays can be programmed for each Auxiliary Device as shown in Figure 7. Timing of turn-on and turn-off events can be synchronized between Auxiliary Devices and POL converters by programming appropriate delays for specific types of devices.

Figure 6. Sequencing Tracking Window

### **8.3 DPM FUNCTIONS**

### 8.3.1 POL PROGRAMMING

POL programming is the process of downloading the content of POL setup registers stored in DPM's non-volatile memory via the SD bus to the POL converters.

Programming of POL converters is performed upon power-up, or when the Program button is pressed in the GUI System Configuration window shown in Figure 8, or when the specific command is sent directly via the I<sup>2</sup>C bus.

Figure 7. System Configuration Window

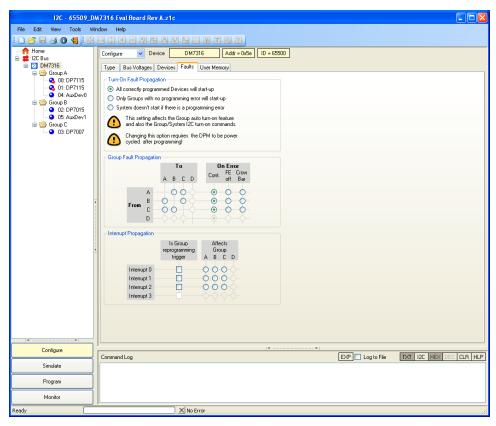

The programming is performed in several steps. Once the supply voltage on the VDD pins of the DPM exceeds the UVLO protection threshold, the DPM will start copying setup registers from its non-volatile memory into RAM and execute the cyclic redundancy check (CRC) to ensure integrity of the programming data. When the voltage on the IBVS pin exceeds the IBV undervoltage protection threshold, the DPM will download POL setup registers to the respective POL converter via the SD line. Every data transfer is protected by parity check and followed by the POL acknowledgement and read data back procedure. If both acknowledgement and readback operations are successful, the POL-specific bit in the POL Programming Status registers will be set. The DPM considers the POL converter to be programmed, and continues programming the next POL converter. Upon completion of the programming, the DPM will turn-on the POL converters, if the Auto Turn-On is enabled in the POL Group configuration window shown in Figure 9 (topmost group of square buttons just below "Bus Voltages" tab. Otherwise, the user will need to send the turn-on command via the I<sup>2</sup>C bus.

Figure 8. POL Configuration Window

### 8.3.2 PROGRAMMING TIME

Total system programming time can be determined from the following equation: Where:

- TPROGR time interval from the instant when the DPM supply voltage exceeds DPM's UVLO threshold until the DPM issues the turn-on command. If the Auto Power-Up is enabled, and the turn-on delay is set to zero, the output voltages start ramping up at the end of TPROGR interval

- TINIT DPM initialization interval after the DPM supply voltage exceeds the UVLO threshold. TINIT = 11.5ms.

- TPOL Time required for programming and verifying of one POL converter. TPOL=26.5ms.

- TAD Time required for programming and verifying of one Auxiliary Device. TAD = 7.5ms.

- nPOL Number of POL converters in the system.

- nAD Number of Auxiliary Devices in the system.

The programming data (DPM and POL setup registers and the user memory) can be preloaded into DPMs by Bel Power Solutions or the DPMs can be programmed by the user via the GUI, I<sup>2</sup>C bus, or JTAG programming interface. The DPMs can be programmed either before or after installation on a host board.

To modify POL converter settings, the user can directly access the registers of a POL converter via the I<sup>2</sup>C bus, bypassing DPM's POL setup registers. The I<sup>2</sup>C commands are translated by the DPM and converted into appropriate SD commands to read / write from / into the registers of a POL converter. Writing into these registers is limited by the hardware (LCK\_N) and/or software write protections. Since POL converters do not have non-volatile memory, data written directly into POL converter registers will be lost when the input voltage is removed.

### **8.4 MONITORING**

#### 8.4.1 POL MONITORING

d-pwer<sup>™</sup> and Z-one<sup>™</sup> POL converters continuously monitor their own performance parameters such as output voltage, output current, and temperature. The monitored parameters are stored locally in the POL converters and updated every 1ms. If monitoring feature is enabled, the DPM will be continuously copying status and parametric data from POL converters into DPM's monitoring data registers.

The monitoring is enabled by checking the appropriate Retrieve Monitoring bits in the GUI Group Configuration window shown in Figure 9 or directly via the I<sup>2</sup>C bus by specific commands.

If the status monitoring is enabled, the status of each protection (overcurrent, overvoltage, etc.) is being reported. If the parametric monitoring is enabled, then real-time values of voltage, current, and temperature are being reported.

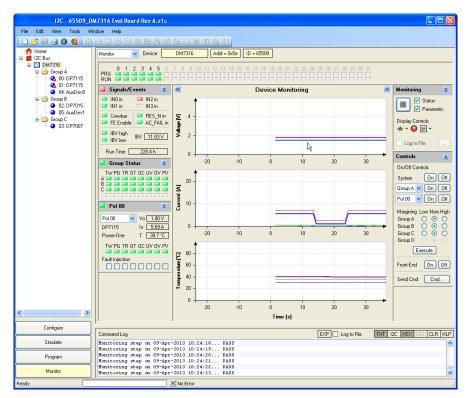

Status and parametric monitoring data of a single POL converter and groups of POL converters can be examined in the GUI IBS Monitoring Window shown in Figure 10 or directly via the I<sup>2</sup>C bus using specific commands. Status data for each group of POL converters is presented in the Group Status block in the left top corner of the window. Parametric data for individual POL converters is shown in Voltage [V], Current [A], and Temp [T] screens.

DPMs also monitor and report programming status of each POL converter and results of CRC operations.

### 8.4.2 MONITORING OF AUXILIARY DEVICES

The DPM can read status information of the Auxiliary Devices via the PG0...PG3 inputs. The PG0...PG3 are digital 3.3V compliant inputs with internal pull-up resistors. Logic high input on a PGX pin should correspond to normal operation of an Auxiliary Device.

Status monitoring data of Auxiliary Devices is stored in the DPM and displayed in the IBS Monitoring Window shown in Figure 10.

Figure 9. IBS Monitoring Window

### 8.4.3 RUN TIME COUNTER

The DPM also monitors the duration of time that it has been in operation. The 4 bytes Run Time Counter is active whenever the DPM is powered up. The count rate is 1 second. The counter is loaded into RAM upon power-up and the new count state is periodically saved to the non-volatile memory. Contents of the counter can be examined in the GUI IBS Monitoring Window shown in Figure 10 or directly via the I<sup>2</sup>C bus using specific commands.

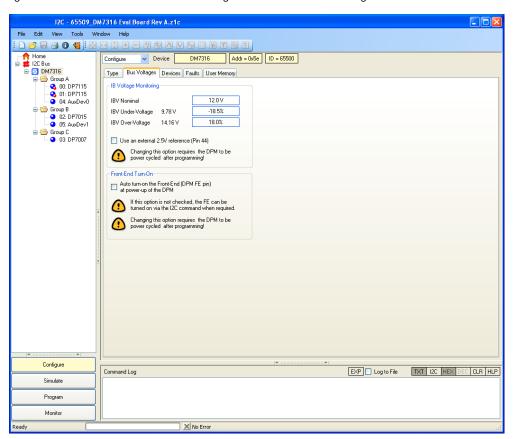

### 8.4.4 IBV MONITORING

The DPM continuously monitors the intermediate bus voltage via the IBVS input and the built-in 10-bit ADC. The digital representation of the bus voltage is stored in RAM and reported in the IBS Monitoring window shown in Figure 10. In addition, the DPM continuously compares the value of IBV to the Undervoltage and Overvoltage thresholds programmed in the GUI Intermediate Bus Configuration Window shown in Figure 11.

Figure 10. Intermediate Bus Configuration Window

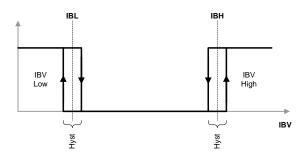

The thresholds have a symmetric, fixed size hysteresis as shown in Figure 12.

Figure 11. Undervoltage (IBL) and Overvoltage (IBH) Protections Hysteresis

When the IBV decreases below the IBL threshold minus the hysteresis, the DPM will pull OK lines low turning off all POL converters. The POL converters will execute regular turn-off ramping their output voltages down according to the turn-off delay and falling slew rate settings. In addition, the DPM will clear all bits in the POL Programming Status registers and save the content of the Run Time Counter into the non-volatile memory. The IBV Low bit in the IBS Monitoring Window will change to red. When the IBV recovers above the IBL threshold plus the hysteresis, the DPM will first program all POL converters and then turn them on, if the Auto Turn-On is enabled in the POL Group configuration window shown in Figure 9. Otherwise, the user will need to send the turn-on command via the I²C bus.

When the IBV exceeds the IBH threshold plus the hysteresis, the DPM will pull OK lines low turning off all POL converters. The POL converters will execute regular turn-off ramping their output voltages down according to the turn-off delay and falling slew rate settings. In addition, the DPM will save the contents of the Run Time Counter into the non-volatile memory. If the IBV does not decrease below the IBH threshold minus the hysteresis within the next 50ms, the DPM will pull low the FE\_EN output and clear all bits in the POL Programming Status registers. The IBV High bit in the IBS Monitoring Window will change to red. If the IBV still does not change, in 50ms the DPM will pull the CB pin high for 1ms to trigger an optional crowbar protection.

One second after the IBV decreases below the IBH threshold minus the hysteresis, the DPM will pull the FE\_EN high and program all POL converters. Upon completion of the programming process, the DPM will turn on the POL converters, if the Auto Turn-On is enabled in the POL Group configuration window shown in Figure 9.

The propagation delay between the IBV increasing/decreasing above/below corresponding thresholds and the DPM pulling down OK lines and triggering the turn-off process is approximately 1ms.

### 8.4.4.1 VOLTAGE REFERENCE

For the purposes of IBV monitoring the user can select either the DPM's internal voltage reference or an external 2.5V voltage reference. The selection is made by clicking an appropriate radio button in the DPM Configuration/Bus Voltages dialog as shown previously in Figure 11.

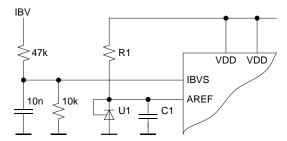

The DPM's internal 2.56V voltage reference is effective accuracy of the IBV protection thresholds to 15%. If the accuracy is sufficient, the user does not need to make any changes to the schematic shown in Figure 3. If higher accuracy of the IBV monitoring is desired, then a 2.5V external reference can be added as shown in Figure 13. The GUI automatically changes values of the IBL and IBH thresholds when the reference selection is changed.

**Note:** If the Reference Voltage setting is changed during operation of the DPM, then the power to the DPM needs to be cycled or the HRES\_N pin needs to be pulled low and released.

Figure 12. External Voltage Reference Connections

U1 and R1 are additional components. U1 is an industry standard 2.5V voltage reference such as TL431 or similar. C1 is an existing component but its value changes depending on the type of voltage reference. Common voltage reference part numbers and values of associated components are shown in Table 4.

| U1 Part Number | TL431     | ZR431     |

|----------------|-----------|-----------|

| Manufacturer   | TI        | Zetex     |

| Accuracy, %    | 0.5, 1, 2 | 0.5, 1, 2 |

| R1, Ohms       | 100-620   | 510-2000  |

| C1, μF         | ≥ 10      | ≥ 0.01    |

Table 4. Component Values for External Reference

Accuracy of the protection thresholds in the case of external reference is determined by the sum of accuracy of the voltage reference, accuracy of the 10k/47k resistive divider shown in Figure 13, and conversion error of the internal ADC specified in 7.2.

### **8.5 POL GROUP MANAGEMENT**

POL converters and Auxiliary Devices can be arranged in up to four groups. A group of POL converters is defined as a number of POL converters with interconnected OK pins. Auxiliary Devices are added to a group in the GUI, without any external connections. A group can include from 1 to 32 POL converters, but a POL converter can be a member of only one group. In addition, the OK lines can be connected to the DPM to facilitate propagation of faults and errors between groups. One DPM can manage up to four independent groups: A, B, C, and D, depending on model of the DPM.

Group management includes fault and error propagation, margining, turn-on and turn-off, monitoring setup, and interrupt configuration.

### 8.5.1 FAULT AND ERROR PROPAGATION

dP-series POL converters protect outputs by triggering either a fault or an error depending on the severity of the problem (see POL converter datasheets). Fault propagation between POL converters belonging to the same group is a programmable function of POL converters. The DPM allows propagating faults and errors between groups of POL converters and, in case of an error, to a DC/DC front-end and an optional crowbar. The propagation delay for fault/error propagations is less than  $10\mu s$ .

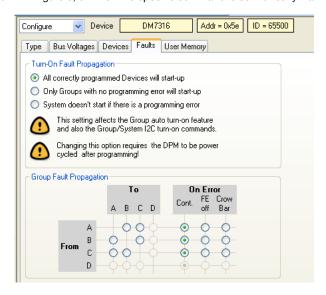

To enable fault and error propagation, the respective bits needs to be checked in the GUI Fault and Error Propagation window shown in Figure 14. Note that cross propagation of faults/errors (means fault in Group X propagates to Y and vice versa) should be avoided.

Figure 13. Fault and Error Propagation Window

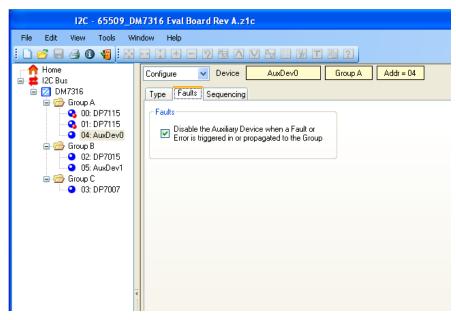

The fault propagation from POL converters to the auxiliary devices can be disabled by checking the bit in the Auxiliary Device Fault Management window as shown in Figure 15. It is not possible to propagate a fault from an Auxiliary Device to POL converters.

Figure 14. Auxiliary Device Fault Management Window

| Protection<br>Triggered    | Propagation<br>Between<br>POLs | Propagation To Auxiliary Devices in the Same Group as the Faulty POL | Propagation<br>To Auxiliary<br>Devices in<br>Other<br>Groups | Propagation<br>Between<br>Groups of<br>POLs | Faulty POL                              | POLs in the<br>Same Group<br>as the Faulty<br>POL | Auxiliary Devices in the Same Group as the Faulty POL | POLs in<br>Other<br>Groups | Auxiliary<br>Devices in<br>Other<br>Groups |

|----------------------------|--------------------------------|----------------------------------------------------------------------|--------------------------------------------------------------|---------------------------------------------|-----------------------------------------|---------------------------------------------------|-------------------------------------------------------|----------------------------|--------------------------------------------|

| UVP or<br>OTP              | Enabled                        | Disabled                                                             | Any                                                          | Disabled                                    | Regular turn-<br>off                    | Regular turn-off                                  | Continue operating                                    | Continue operating         | Continue operating                         |

| UVP or<br>OTP              | Enabled                        | Enabled                                                              | Any                                                          | Disabled                                    | Regular turn-<br>off                    | Regular turn-off                                  | Turn-off with turn-off delay                          | Continue operating         | Continue operating                         |

| UVP or<br>OTP              | Enabled                        | Enabled                                                              | Disabled                                                     | Enabled                                     | Regular turn-<br>off                    | Regular turn-off                                  | Turn-off with turn-off delay                          | Regular<br>turn-off        | Continue operating                         |

| UVP or<br>OTP              | Enabled                        | Enabled                                                              | Enabled                                                      | Enabled                                     | Regular turn-<br>off                    | Regular turn-off                                  | Turn-off with turn-off delay                          | Regular<br>turn-off        | Turn-off with turn-off delay               |

| Tracking<br>or OCP         | Enabled                        | Disabled                                                             | Any                                                          | Disabled                                    | Fast turn-off                           | Regular turn-off                                  | Continue<br>operating                                 | Continue operating         | Continue operating                         |

| Tracking or OCP            | Enabled                        | Enabled                                                              | Any                                                          | Disabled                                    | Fast turn-off                           | Regular turn-off                                  | Turn-off with<br>turn-off delay                       | Continue operating         | Continue operating                         |

| Tracking<br>or OCP         | Enabled                        | Enabled                                                              | Disabled                                                     | Enabled                                     | Fast turn-off                           | Regular turn-off                                  | Turn-off with<br>turn-off delay                       | Regular<br>turn-off        | Continue operating                         |

| Tracking or OCP            | Enabled                        | Enabled                                                              | Enabled                                                      | Enabled                                     | Fast turn-off                           | Regular turn-off                                  | Turn-off with<br>turn-off delay                       | Regular<br>turn-off        | Turn-off with<br>turn-off delay            |

| OVP or<br>Phase<br>Voltage | Enabled                        | Disabled                                                             | Any                                                          | Disabled                                    | Fast turn-off,<br>low side FET<br>is ON | Fast turn-off                                     | Continue operating                                    | Continue operating         | Continue operating                         |

| OVP or<br>Phase<br>Voltage | Enabled                        | Enabled                                                              | Any                                                          | Disabled                                    | Fast turn-off,<br>low side FET<br>is ON | Fast turn-off                                     | Turn-off<br>without turn-off<br>delay                 | Continue operating         | Continue operating                         |

| OVP or<br>Phase<br>Voltage | Enabled                        | Enabled                                                              | Disabled                                                     | Enabled                                     | Fast turn-off,<br>low side FET<br>is ON | Fast turn-off                                     | Turn-off<br>without turn-off<br>delay                 | Regular<br>turn-off        | Continue operating                         |

| OVP or<br>Phase<br>Voltage | Enabled                        | Enabled                                                              | Enabled                                                      | Enabled                                     | Fast turn-off,<br>low side FET<br>is ON | Fast turn-off                                     | Turn-off<br>without turn-off<br>delay                 | Regular<br>turn-off        | Turn-off with turn-off delay               |

Table 5. Fault and Error Propagation Scenarios

When propagation is enabled, the faulty POL converter pulls its OK pin low. A low OK line initiates turn-off of other POL converters in the group and signals the DPM to pull other OK lines low to initiate turn-off of other POL converters as programmed.

The regular turn-off of a POL converter means that the output voltage is ramping down according to its turn-off delay and falling slew rate settings. If a POL converter triggers an undervoltage or overtemperature fault, it will initiate the regular turn-off. In the case of an overcurrent or tracking fault, the POL converter initiates the fast turn-off by opening both high and low side switches instantaneously. If either output overvoltage or phase voltage errors are triggered, the faulty POL converter initiates the fast turn-off and turns on its low side switch. In addition, when an error is propagated, the DPM can generate commands to turn off a front end (a DC-DC converter generating the intermediate bus voltage) and trigger an optional crowbar protection to accelerate removal of the intermediate bus voltage (IBV).

Once the fault has recovered in the faulty POL converter, the other POL converters will turn on in a controlled manner according to their turn-on delay and rising slew rate settings.

### 8.5.2 MARGINING

Margining can be executed separately for each group by clicking an appropriate radio button in the GUI IBS monitoring window shown in Figure 10 or directly via the I<sup>2</sup>C bus by the margining command. All POL converters in a group are margined in the same direction (up or down) by the percentage programmed individually for each POL converter.

### 8.5.3 TURN-ON AND TURN-OFF

Automatic turn-on upon application of the input voltage is enabled by checking the Auto Turn-On bit in the GUI Group Configuration window shown in Figure 9. Turn-on and turn-off of various groups during the operation is controlled from the GUI IBS Monitoring window or directly via the I<sup>2</sup>C bus by specific commands.

### 8.5.4 INTERRUPT CONFIGURATIONS

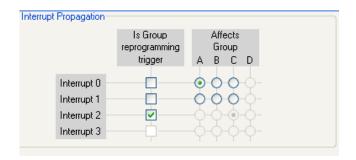

The DPM has four interrupt inputs that can be programmed to:

- Inhibit the operation of one or several Groups of POL converters when pulled low or

- Act as a Group Reprogramming Trigger.

The two functions are mutually exclusive – an interrupt can be either programmed as an Inhibit or as a Group Reprogramming Trigger.

The interrupts are programmed in the GUI Interrupt Configuration window shown in Figure 16 or directly via the I<sup>2</sup>C bus by specific commands. In Figure 16 the Interrupt 0 is programmed as the inhibit for group A and the Interrupt 2 is programmed as the group C reprogramming trigger.

### 8.5.4.1 GROUP INHIBIT

An interrupt input can be programmed to act as an inhibit on a single or multiple groups of POL converters. When the interrupt input is pulled low, the DPM will pull the appropriate OK lines low. The affected POL converters will execute regular turn-off ramping their output voltages down according to the turn-off delay and falling slew rate settings. Once the interrupt is released, the POL converters will automatically turn-on according to their turn-on delay and rising slew rates settings.

The inhibit function can be used for a variety of applications, such as

- Hardware-based control of groups of POL converters and Auxiliary Devices

- Delayed turn-on at power-up (Automatic Turn-On is enabled but the interrupts are held low during power-up.

Note that POL converters can be programmed even when an interrupt is held low.)

The interrupt inputs should be controlled with open collector devices. The propagation delay between the external device pulling the interrupt input low and the DPM pulling down OK lines and triggering the turn-off process is approximately 10µs. This option is set as part of DPM/Configure/Faults dialogs.

Figure 15. Interrupt Configuration Dialog

#### 8.5.4.2 GROUP REPROGRAMMING TRIGGER

An interrupt that is programmed as a group reprogramming trigger always acts only on one group of POL converters. Interrupt 0 acts on Group A, Interrupt 1 acts on Group B and so on. The assignment is fixed and cannot be changed by the user.

When the interrupt is pulled low, the DPM will program the group of POL converters. Upon completion of the programming, the DPM will turn-on the POL converters, if the Auto Turn-On is enabled. When the interrupt input is released, the DPM will pull the appropriate OK line low. The POL converters in the group will execute regular turn-off ramping their output voltages down according to the turn-off delay and falling slew rate settings. In addition, the DPM will clear all bits in the POL Programming Status registers.

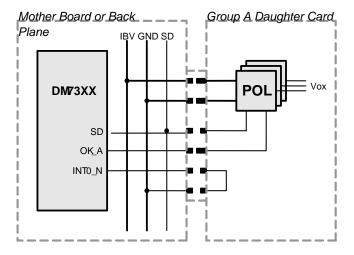

The group reprogramming trigger is mostly used to support hot swap of boards and daughter cards that do not have a DPM installed on them as shown in Figure 17.

Figure 16. INTO Configured as Group A Reprogramming Trigger

In this configuration the Interrupt 0 (INTO\_N) is configured as the group A reprogramming trigger. The DPM is installed on a mother board or a backplane. A daughter card with a group of POL converters is being inserted in the system during normal operation. At first, the long pins carrying power and the OK\_A line signal make contact. Then the short pins carrying the SD and interrupt signals make contact. Once the interrupt senses low input voltage, it will command the DPM to program all POL converters in the group A. Upon completion of the programming, the DPM will turn-on the POL converters, if the Auto Turn-On is enabled.

When the daughter card is being removed, the interrupt input is released as soon as the short pins break the contact. The DPM will immediately pull the OK\_A line low turning off all POL converters in the group A according to the turn-off delay and falling slew rate settings.

### **8.6 CONTROLS**

#### 8.6.1 ACFAIL N AND RES N

The ACFAIL\_N and RES\_N are active low digital inputs. When one of the inputs is pulled low, the DPM will pull all OK lines low turning off all the POL converters and the Auxiliary Devices in all groups. The POL converters will execute regular turn-off ramping their output voltages down according to the turn-off delay and falling slew rate settings. In addition, the DPM will clear all bits in the POL Programming Status Registers and save the contents of the Run Time Counter into the non-volatile memory. The AC\_FAIL in or RES\_N in bit in the IBS Monitoring Window will change to red. When the input is released, the DPM will first program all POL converters and then turn them on, if the Auto Turn-On is enabled. Otherwise, the user will need to send the turn-on command via the I²C bus.

The ACFAIL\_N is typically connected to an AC-DC front end. Whenever the AC voltage disappears, the ACFAIL\_N signal will be set low. If there is no battery backup, it usually means the DC output will disappear after 20ms. If the turn-off delays and falling slew rates of each POL converter are set to the values such that all POL converters will have fully turned off within the hold time of the AC-DC front end, then output voltage tracking during turn-off is guaranteed.

The RES\_N input has the same functionality as the ACFAIL\_N input and can be connected to a simple turn on/off switch or to a sensor that shuts the entire system down when it is activated.

The ACFAIL\_N and RES\_N inputs should be controlled with open collector devices. The propagation delay between the external device pulling the input low and the DPM pulling down OK lines and triggering the turn-off process is approximately 1ms.

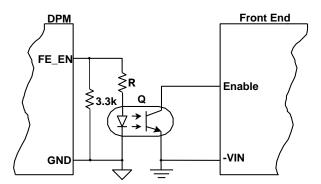

### 8.6.2 FRONT END ENABLE

The FE\_EN pin is dedicated to the control of a DC-DC Front End. The Front End is typically used to convert the 48V into the intermediate bus voltage (IBV). If the DPM is powered from an auxiliary source, not from the IBV, it can control the DC-DC Front End.

When FE\_EN is internally pulled up to 3.3V, the Front End is enabled. The FE\_EN output can provide up to 5mA of current. When the FE\_EN goes low, the Front End is disabled. The Front End can be enabled and disabled via the GUI IBS Monitoring Window or directly via the I<sup>2</sup>C bus using specific commands.

The FE\_EN pin should not be directly connected to the Enable pin of the DC-DC Front End. Typically, the Enable pin is referenced to the primary side of the Front End that is isolated from the low voltage secondary side. In addition, the Enable pin can be pulled up internally to a voltage potentially damaging to the DPM FE\_EN output. The best method is to interface the DPM with the Front End through an optocoupler as shown in Figure 18. This configuration provides interface for negative logic front ends.

Figure 17. Interface between DPM and DC-DC Front End

### 8.6.3 CROWBAR

When the crowbar protection is enabled, the CB pin is internally pulled up to 3.3V for 1ms. It is capable of supplying 5mA to turn on a crowbar circuit.

#### 8.6.4 HRES N

The HRES\_N is an active low digital input. When it is pulled low, the DPM will perform full hardware reset including processor, memory, and communication interface. The POL converters and auxiliary devices will be turned off although sequencing and tracking during the turn-off are not guaranteed. Communication with a host processor or GUI (if established) will be lost. When the input is released, the DPM will first program all POL converters and then turn them on, if the Auto Turn-On is enabled.

Unlike all other I/O pins on the DM73XX DPM, the HRES\_N does not have an internal ESD protection diode connected to VDD. Therefore, it is necessary to add the diode externally as shown in Figure 3.

The HRES\_N function is intended as an emergency reset and except as indicated below, should not be used in normal system operation.

It is **necessary** to use an external reset circuit (see Fig. 3) to hold the HRES\_N line low until the VDD supply reaches steady state conditions. Bel Power Solutions Inc. successfully tested the On-Semi voltage detector p/n NCP303LSN27T1 although other similar devices can also be utilized. Alternatively, the HW\_RES pin can be connected to the output of a CPLD (or similar device) and controlled via the system supervisory circuitry.

### 8.7 COMMUNICATION INTERFACES

### 8.7.1 I<sup>2</sup>C INTERFACE

The DM73XX series DPMs have the industry standard I<sup>2</sup>C interface fully meeting the requirements of the I<sup>2</sup>C -Bus Specification Version 2.1 from Philips Semiconductors. The I<sup>2</sup>C interface is working in the following configurations:

- standard (100kbs) and fast (400kbs) data transfer rates

- 7-bit addressing: 4 MSBs fixed, 3 LSBs programmable by ADDR [2:0]. The address prefix of the DM73XX is 0x50.

This allows encoding DPM addresses 0x50, 0x52, ..., 0x5E (Bit0 is the read/write bit)

The DPM always acts as the I<sup>2</sup>C slave while the host processor always acts as the I<sup>2</sup>C master. Refer to the "DPM Programming Manual" for the detailed description of the I<sup>2</sup>C communications.

**Note:** It is recommended to use Bel Power Solutions ZM00056-KIT USB to I<sup>2</sup>C Adapter kit for the communication between a DPM and a computer with the Bel Power Solutions I<sup>2</sup>C Graphical User Interface.

### 8.7.1.1 WATCHDOG TIMER

In order to prevent occasional hanging of the I<sup>2</sup>C bus, a watchdog timer is started whenever an I<sup>2</sup>C command is initiated. If the command is not executed before the watchdog times out, the DPM will assume that the I<sup>2</sup>C bus is in an error condition (e.g. the SCL or SDA lines are pulled low continuously) and it will reset the I<sup>2</sup>C bus. The watchdog timeout is 1000ms. Since the watchdog function is not a part of the standard I<sup>2</sup>C specifications, it can be disabled by the user.

### 8.7.2 JTAG INTERFACE

The DM73XX series DPMs feature the JTAG interface that can be used for programming the DPM with user-specific configuration settings. JTAG boundary-scan capabilities are not currently supported.

JTAG-programmable DPMs have unique 5-digit identifiers listed in Table 6.

| BASE PART NUMBER | 5- DIGIT IDENTIFIER |

|------------------|---------------------|

| DM7304G          | 65515               |

| DM7308G          | 65516               |

| DM7316G          | 65517               |

| DM7332G          | 65518               |

Table 6. JTAG Programmable DPM Part Numbers

Only the DPM part numbers listed in the table can be programmed via the JTAG interface.

**Note:** The DPMs can be programmed via the JTAG only once. After initial programming via the JTAG, the DPMs may be reprogrammed via I<sup>2</sup>C as necessary.

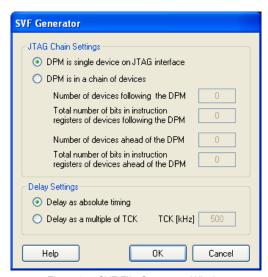

#### 8.7.2.1 SVF FILE

In order to program a DPM via the JTAG interface, the Serial Vector Format (SVF) file needs to be generated. Click Generate SVF button in the System Configuration window shown in Figure 8. It will open the SVF Generator window shown in Figure 19.

The window allows specifying the location of the target DPM in the JTAG chain and setting delays to generate the appropriate Serial Vector Format file. The resulting file is used to program the DPMs through the JTAG interface.

Refer to "Programming DM73XX DPMs via JTAG Interface" Application Note for more details.

Figure 18. SVF File Generator Window

### 8.7.2.2 JTAG INSTRUCTIONS

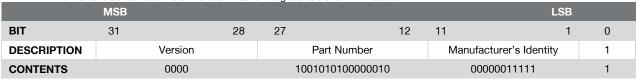

DM73XX series DPMs support only BYPASS and IDCODE instructions defined by IEEE 1149.1. SAMPLE/PRELOAD and EXTEST instructions are not currently supported. Summary of the supported instructions is shown in Table 7.

| INSTRUCTION | OPCODE | REGISTER | FUNCTION                                                                                                                                                          |