# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### **Features and Benefits**

- High-current 3-phase gate drive for N-channel MOSFETs

- 3-phase current sense amplifiers

- SPI-compatible serial or direct parallel control

- Cross-conduction protection

- Programmable dead time

- Top-off charge pump for 100% PWM

- Uncommitted buffer amplifier

- 5.5 to 50 V supply voltage range

- CMOS inputs, 3.3 to 5 V logic supply

- Extensive diagnostics output

- Low-current sleep mode

### PACKAGE:

48-pin LQFP with exposed thermal pad (suffix JP)

Not to scale

### Description

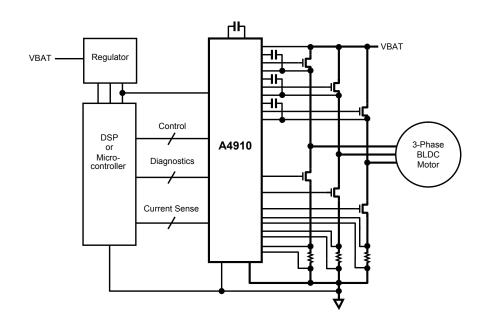

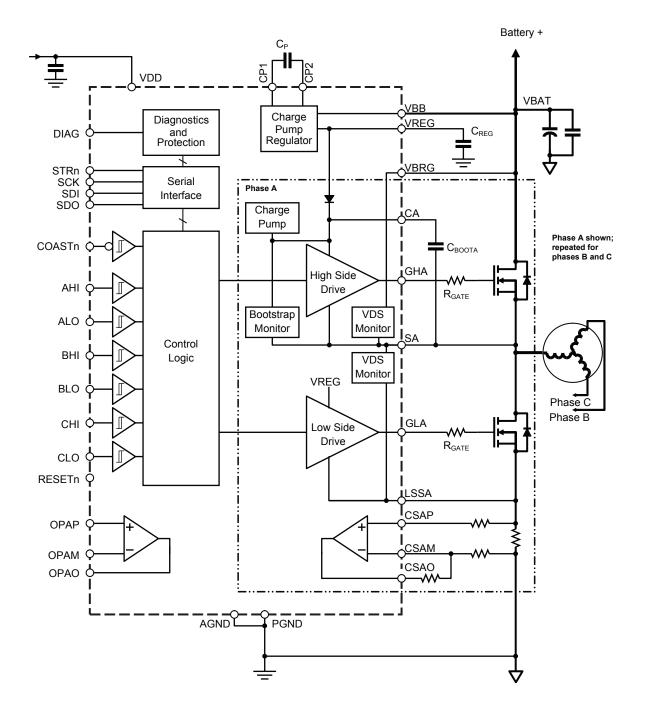

The A4910 is a three-phase controller for use with N-channel external power MOSFETs and is specifically designed for automotive applications.

A unique charge-pump regulator provides full (>10 V) gate drive for battery voltages down to 7 V, and allows the A4910 to operate with a reduced gate drive down to 5.5 V.

A bootstrap capacitor is used to provide the above battery supply voltage required for N-channel MOSFETs. An internal charge pump for the high-side drive allows DC (100% duty cycle) operation.

Full control over all six power MOSFETs in the 3-phase bridge is provided, allowing motors to be driven with block commutation or sinusoidal excitation. The power MOSFETs are protected from shoot-through by integrated crossover control and programmable dead time.

Continued on the next page ...

### Applications

- Electronic power steering (EPS, EHPS, EAS)

- Hydraulic pumps

- Engine cooling fan

- Gearbox actuator

# **Typical Application Drawing**

### **Description (continued)**

Current in each half bridge can be measured using integrated current sense amplifiers. These are three user-configurable differential amplifiers, with below-ground common-mode range and excellent transient response and settling time, allowing them to be used in low-side current-sense applications.

Integrated diagnostics provide indication of undervoltage,

overtemperature, and power bridge faults, and can be configured to protect the power MOSFETs under most short-circuit conditions. Detailed diagnostics are available as a serial data word.

The A4910 is supplied in a small footprint (81 mm<sup>2</sup>) 48-pin LQFP with exposed thermal pad (suffix JP). It is lead (Pb) free, with 100% matte-tin leadframe plating.

#### SELECTION GUIDE

| Part Number  | Package                     | Packing*                                                            |  |

|--------------|-----------------------------|---------------------------------------------------------------------|--|

| A4910KJPTR-T | 1500 pieces per 13-in. reel | 7 mm × 7 mm, 1.6 mm nominal height LQFP<br>with exposed thermal pad |  |

\*Contact Allegro<sup>TM</sup> for additional packing options.

#### ABSOLUTE MAXIMUM RATINGS with respect to AGND, PGND connected directly to AGND

| Characteristic                           | Symbol               | Notes                                                                                                                           | Rating                                              | Unit |

|------------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|------|

| Load Supply Voltage                      | V <sub>BB</sub>      |                                                                                                                                 | -0.3 to 50                                          | V    |

| Logic Supply Voltage                     | V <sub>DD</sub>      |                                                                                                                                 | -0.3 to 6                                           | V    |

| Terminal VREG                            | V <sub>REG</sub>     |                                                                                                                                 | -0.3 to 16                                          | V    |

| Terminal CP1                             | V <sub>CP1</sub>     |                                                                                                                                 | -0.3 to 16                                          | V    |

| Terminal CP2                             | V <sub>CP2</sub>     |                                                                                                                                 | V <sub>CP1</sub> – 0.3 to<br>V <sub>REG</sub> + 0.3 | V    |

| Logic Inputs                             |                      | STRn, SDI, SCK, RESETn, COASTn, xHI, and xLO terminals                                                                          | -0.3 to 6                                           | V    |

| Logic Outputs                            |                      | SDO, and DIAG terminals                                                                                                         | -0.3 to V <sub>DD</sub> + 0.3                       | V    |

| Sense Amplifier Inputs                   |                      | CSAP, CSAM, CSBP, CSBM, CSCP, and CSCM terminals                                                                                | -4 to 6.5                                           | V    |

| Sense Amplifier Outputs                  |                      | CSAO, CSBO, and CSCO terminals                                                                                                  | -0.3 to V <sub>DD</sub> + 0.3                       | V    |

| Operational Amplifier Inputs             |                      | OPAP and OPAM terminals                                                                                                         | -0.3 to 6.5                                         | V    |

| Operational Amplifier Outputs            |                      | OPAO terminals                                                                                                                  | -0.3 to V <sub>DD</sub> + 0.3                       | V    |

| Terminal VBRG                            | V <sub>BRG</sub>     |                                                                                                                                 | -5 to 55                                            | V    |

| Terminals CA, CB, and CC <sup>1</sup>    | V <sub>Cx</sub>      |                                                                                                                                 | –0.3 to V <sub>REG</sub> + 50                       | V    |

| Terminals GHA, GHB, and GHC <sup>2</sup> | V <sub>GHx</sub>     |                                                                                                                                 | $V_{Cx}$ - 16 to<br>$V_{Cx}$ + 0.3                  | V    |

| Terminals SA, SB, and SC <sup>2</sup>    | V <sub>Sx</sub>      |                                                                                                                                 | $V_{Cx}$ – 16 to<br>$V_{Cx}$ + 0.3                  | V    |

| Terminals GLA, GLB, and GLC              | V <sub>GLx</sub>     |                                                                                                                                 | V <sub>REG</sub> – 16 to 18                         | V    |

| Terminals LSSA, LSSB, and LSSC           | V <sub>LSSx</sub>    |                                                                                                                                 | V <sub>REG</sub> – 16 to 18                         | V    |

| Ambient Operating Temperature<br>Range   | T <sub>A</sub>       | Limited by power dissipation                                                                                                    | -40 to 150                                          | °C   |

|                                          |                      | Continuous                                                                                                                      | 150                                                 | °C   |

| Maximum Junction Temperature             | T <sub>J</sub> (max) | Overtemperature event not exceeding 10 seconds, lifetime duration not exceeding 10 hours, determined by design characterization | 175                                                 | °C   |

| Storage Temperature Range                | T <sub>stg</sub>     |                                                                                                                                 | -55 to 150                                          | °C   |

<sup>1</sup> For example, at  $V_{REG}$  = 13 V the most positive rating is 13 V + 50 V = 63 V, while at  $V_{REG}$  = 8 V the most positive rating is 8 V + 50 V = 58 V. <sup>2</sup> For example, at  $V_{REG}$  = 13 V the most negative rating is  $V_{Cx}$  - 16 V = -0.3 V - 16 V = -16.3 V, and the most positive rating is  $V_{Cx}$  + 0.3 V =  $V_{REG}$  + 50 V + 0.3 V = 13 V + 50 V + 0.3 V = 63.3 V. If  $V_{REG}$  = 8 V, the most negative rating remains at -16.3 V, and the most positive rating is 58.3 V.

# A4910

# Automotive 3-Phase MOSFET Driver

#### **Table of Contents**

| Features and Benefits1DIAG Output20Description1System Faults20Applications1MOSFET Faults21Typical Application Drawing1Fault Actions23Selection Guide2Fault States23Absolute Maximum Ratings2Fault Masking23Thermal Characteristics3Serial Interface24Pinout Diagram and Terminal List4Configuration and Control Registers25Electrical Characteristics6Serial Register Definition27Supply and Reference6Configuration Register 10 (Config)27Gate Output Drive6Configuration Register 10 (Config)27Logic Inputs and Outputs7Diagnostic Register28Uncommitted Operational Amplifier9Run Register29Protection10Application Information30Character Stic Definitions11Dead Time Selection30Serial Interface Timing12Bootstrap Charge Management31Ordate Drive Timing, Phase12Bootstrap Charge Management31Propagation Delay Timing13VREG Capacitor Selection31Ordate Drive Timing, COASTn12Bootstrap Charge Management31Propagation Delay Timing13VREG Capacitor Selection31Input and Output Terminal Functions16Current Sense Amplifier32Input and Drive Timing13VREG Capacitor Selection31 <t< th=""><th>Specifications</th><th>1</th><th>Diagnostics</th><th>20</th></t<> | Specifications                    | 1  | Diagnostics             | 20  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|----|-------------------------|-----|

| Description1System Faults20Applications1MOSFET Faults21Typical Application Drawing1Fault Actions23Selection Guide2Fault Actions23Absolute Maximum Ratings2Fault Masking23Thermal Characteristics3Serial Interface24Pinout Diagram and Terminal List4Configuration and Control Registers25Functional Block Diagram5Diagnostic Register Definition27Supply and Reference6Configuration Register 0 (Config0)27Gate Output Drive6Configuration Register 1 (Config1)27Logic Inputs and Outputs7Diagnostic Register28Uncommitted Operational Amplifier9Run Register 1 (Config1)27Protection10Application Information30Otharacteristic Definitions11Dead Time Selection30Serial Interface12Bootstrap Characteristic30Gate Drive Timing, Phase12Bootstrap Characteristic Selection30Gate Drive Timing, Phase12Bootstrap Charagement31Propagation Delay Timing13VREG Capacitor Selection31Logic Truth Tables14Supply Decoupling31Logic Truth Tables14Supply Decoupling31Characteristic Performance15Braking31Characteristic Performance16Input Adupt Timing32Input and Output Terminal Fu                                                                                       | Features and Benefits             | 1  |                         | 20  |

| Applications1MOSFET Faults21Typical Application Drawing1Fault Actions23Selection Guide2Fault Making23Absolute Maximum Ratings2Fault Making23Thermal Characteristics3Serial Interface24Pirout Diagram and Terminal List4Configuration and Control Registers25Electrical Characteristics6Serial Register Definition27Supply and Reference6Genfiguration Register 0 (Configo)27Gate Output Drive6Configuration Register 1 (Config1)27Logic Inputs and Outputs7Diagnostic Register28Uncommitted Operational Amplifier9Run Register28Protection10Application Information30Characteristic Definitions11Dead Time Selection30Serial Interface Timing12Bootstrap Charactor Selection30Serial Interface Timing12Bootstrap Characteristic Selection30Gate Drive Timing, Phase12Bootstrap Character Selection31Characteristic Derion Timing13VREG Capacitor Selection31Characteristic Performance16Current Sense Amplifier32Probagation Delay Timing13VREG Capacitor Selection31Logic Control Inputs16Current Sense Amplifier32Input and Output Terminal Functions16Current Sense Amplifier32Power Supplies17Layout Re                                                            | Description                       | 1  |                         | 20  |

| Typical Application Drawing1Fault Actions23Selection Guide2Fault States23Absolute Maximum Ratings2Fault Masking23Thermal Characteristics3Serial Interface24Pinout Diagram and Terminal List4Configuration and Control Registers25Functional Block Diagram5Diagnostic Register25Electrical Characteristics6Serial Register Definition27Supply and Reference6Configuration Register 0 (Config0)27Cate Output Drive6Configuration Register 1 (Config1)27Logic Inputs and Outputs7Diagnostic Register28Output Drive7Diagnostic Register29Protection10Application Information30Characteristic Definitions11Dead Time Selection30Serial Interface Timing12Bootstrap Chapiding30Serial Interface Timing12Bootstrap Chapiding30Gate Drive Timing, Phase12Bootstrap Chapiding31Characteristic Definitions11Dead Time Selection31Logic Truth Tables14Supply Decoupling31Logic Truth Tables14Supply Decoupling31Logic Truth Tables14Supply Decoupling31Logic Control Inputs16Input 4034Gate Drive Timing Functions16Input 4033Power Supplies17Layout Recommendations                                                                                                              | Applications                      | 1  | •                       | 21  |

| Selection Guide2Fault States23Absolute Maximum Ratings2Fault Masking23Thermal Characteristics3Serial Interface24Pinout Diagram and Terminal List4Configuration and Control Registers25Functional Block Diagram5Diagnostic Register25Electrical Characteristics6Serial Register Definition27Supply and Reference6Configuration Register 0 (Config0)27Cate Output Drive6Configuration Register 1 (Config1)27Logic Inputs and Outputs7Diagnostic Register28Current Sense Amplifier9Run Register29Protection10Application Information30Characteristic Definitions11Dead Time Selection30Timing Diagrams12Fault Blanking Time Selection30Serial Interface Timing12Bootstrap Charging30Gate Drive Timing, Phase12Bootstrap Charging30Gate Drive Timing, COASTn12Bootstrap Charging31Propagation Delay Timing13VREG Capacitor Selection31Logic Truth Tables14Supply Decoupling31Characteristic Derformance15Braking31Functional Description16Current Sense Amplifier32Power Supplies17Layout Recommendations34Gate Drives17Layout Recommendations34Gate Drives17Layou                                                                                                         | Typical Application Drawing       | 1  |                         |     |

| Absolute Maximum Ratings2Fault Masking23Thermal Characteristics3Serial Interface24Pinout Diagram and Terminal List4Configuration and Control Registers25Functional Block Diagram5Diagnostic Register25Electrical Characteristics6Serial Register Definition27Supply and Reference6Configuration Register 0 (Config0)27Cate Output Drive6Configuration Register 1 (Config1)27Logic Inputs and Outputs, Dynamic7Mask Register28Current Sense Amplifiers8Run Register29Uncommitted Operational Amplifier9Run Register29Protection10Application Information30Characteristic Definitions11Dead Time Selection30Serial Interface Timing12Bootstrap Charge Management31Serial Interface Timing, Phase12Bootstrap Charge Management31Propagation Delay Timing, COASTn12Bootstrap Charge Management31Propagation Delay Timing13VREG Capacitor Selection31Logic Chruth Tables14Supply Decoupling31Functional Description16Current Sense Amplifier32Input and Output Terminal Functions16Input/Output Structures33Power Supplies17Layout Recommendations34Gate Drives17Layout Recommendations34Gate Drives17Layout Rec                                                            | Selection Guide                   | 2  | Fault States            |     |

| Thermal Characteristics3Serial Interface24Pinout Diagram and Terminal List4Configuration and Control Registers25Functional Block Diagram5Diagnostic Register25Electrical Characteristics6Serial Register Definition27Gate Output Drive6Configuration Register 0 (Config0)27Logic Inputs and Outputs7Diagnostic Register28Current Sense Amplifiers8Mask Register28Uncommitted Operational Amplifier9Run Register28Uncommitted Definitions11Dead Time Selection30Thring Diagrams12Fault Blanking Time Selection30Serial Interface Timing12Bootstrap Charge Management31Protection10Application Information30Gate Drive Timing, Phase12Bootstrap Charge Management31Propagation Delay Timing13VREG Capacitor Selection31Logic Truth Tables14Supply Decoupling31Logic Truth Tables14Supply Decoupling31Functional Description16Current Sense Amplifier32Input and Output Terminal Functions16Input/Output Structures33Power Supplies17Layout Recommendations34Gate Drives17Layout Recommendations34Gate Drives17Layout Recommendations34Gate Drives17Layout Recommendations34Gate Dr                                                                                       | Absolute Maximum Ratings          | 2  | Fault Masking           |     |

| Prinout Diagram and Terminal List4Configuration and Control Registers25Functional Block Diagram5Diagnostic Register25Electrical Characteristics6Serial Register Definition27Supply and Reference6Configuration Register 0 (Config0)27Gate Output Drive6Configuration Register 1 (Config1)27Logic Inputs and Outputs7Diagnostic Register28Current Sense Amplifiers8Run Register29Protection10Application Information30Characteristic Definitions11Dead Time Selection30Serial Interface Timing12Bootstrap Charging30Gate Drive Timing, Phase12Bootstrap Charging30Gate Drive Timing, COASTn12Bootstrap Charging31Propagation Delay Timing13VREG Capacitor Selection31Logic Truth Tables14Supply Decoupling31Characteristic Performance15Braking31Functional Description16Current Sense Amplifier32Input and Output Terminal Functions16Input/Output Structures33Power Supplies17Layout Recommendations34Gate Drives17Layout Recommendations34Gate Drives17Layout Recommendations34Gate Drives17Layout Recommendations34Gate Drives17Layout Recommendations34Gate Drives1                                                                                                | Thermal Characteristics           | 3  | Ŭ                       |     |

| Functional Block Diagram5Diagnostic Register25Electrical Characteristics6Serial Register Definition27Supply and Reference6Configuration Register 0 (Config0)27Logic Inputs and Outputs7Diagnostic Register28Logic Inputs and Outputs, Dynamic7Mask Register28Uncommitted Operational Amplifier9Run Register29Protection10Application Information30Characteristic Definitions11Dead Time Selection30Gate Drive Timing, Phase12Bootstrap Charging30Gate Drive Timing, CASTn12Bootstrap Charging30Gate Drive Timing, CASTn12Bootstrap Charging31Propagation Delay Timing13VREG Capacitor Selection31Logic Truth Tables14Supply Decoupling31Characteristic Performance15Braking31Functional Description16Current Sense Amplifier32Input and Output Terminal Functions16Input/Output Structures33Power Supplies17Layout Recommendations34Gate Drives17Layout Recommendations34Gate Drives17Package Outline Drawing35Logic Control Inputs19Current Sense Amplifiers32                                                                                                                                                                                                        | Pinout Diagram and Terminal List  | 4  |                         |     |

| Electrical Characteristics6Serial Register Definition27Supply and Reference6Configuration Register 0 (Config0)27Gate Output Drive6Configuration Register 1 (Config1)27Logic Inputs and Outputs7Diagnostic Register28Current Sense Amplifiers8Run Register29Uncommitted Operational Amplifier9Run Register29Protection10Application Information30Characteristic Definitions11Dead Time Selection30Timing Diagrams12Fault Blanking Time Selection30Gate Drive Timing, Phase12Bootstrap Charging30Gate Drive Timing, COASTn12Bootstrap Charge Management31Propagation Delay Timing13VREG Capacitor Selection31Logic Truth Tables14Supply Decoupling31Functional Description16Current Sense Amplifier32Input and Output Terminal Functions17Layout Recommendations34Gate Drives17Layout Recommendations34Gate Drives17Package Outline Drawing35Logic Control Inputs19Package Outline Drawing35                                                                                                                                                                                                                                                                             | Functional Block Diagram          | 5  |                         |     |

| Supply and Reference6Configuration Register 0 (Config0)27Gate Output Drive6Configuration Register 1 (Config1)27Logic Inputs and Outputs7Diagnostic Register28Current Sense Amplifiers8Run Register29Uncommitted Operational Amplifier9Run Register29Protection10Application Information30Characteristic Definitions11Dead Time Selection30Serial Interface Timing12Bootstrap Capacitor Selection30Gate Drive Timing, Phase12Bootstrap Capacitor Selection30Gate Drive Timing, COASTn12Bootstrap Capacitor Selection31Propagation Delay Timing13VREG Capacitor Selection31Logic Truth Tables14Supply Decoupling31Functional Description16Current Sense Amplifier32Input and Output Terminal Functions16Input/Output Structures33Power Supplies17Layout Recommendations34Gate Drives17Package Outline Drawing35Logic Control Inputs19Current Sense Amplifier32Logic Control Inputs19Package Outline Drawing35                                                                                                                                                                                                                                                            | Electrical Characteristics        | 6  | <b>o o</b>              |     |

| Gate Output Drive6Configuration Register 1 (Config1)27Logic Inputs and Outputs7Diagnostic Register28Logic Inputs and Outputs, Dynamic7Mask Register28Current Sense Amplifiers8Run Register29Protection10Application Information30Characteristic Definitions11Dead Time Selection30Timing Diagrams12Fault Blanking Time Selection30Serial Interface Timing12Bootstrap Capacitor Selection30Gate Drive Timing, COASTn12Bootstrap Charging30Gate Drive Timing, COASTn12Bootstrap Charge Management31Propagation Delay Timing13VREG Capacitor Selection31Logic Truth Tables14Supply Decoupling31Functional Description16Current Sense Amplifier32Input and Output Terminal Functions16Input/Output Structures33Power Supplies17Layout Recommendations34Gate Drives17Package Outline Drawing35Logic Control Inputs19Package Outline Drawing35                                                                                                                                                                                                                                                                                                                               | Supply and Reference              | 6  | •                       |     |

| Logic Inputs and Outputs7Diagnostic Register28Logic Inputs and Outputs, Dynamic7Mask Register28Current Sense Amplifiers8Run Register29Uncommitted Operational Amplifier9Application Information30Protection10Application Information30Characteristic Definitions11Dead Time Selection30Timing Diagrams12Fault Blanking Time Selection30Serial Interface Timing12Bootstrap Charging30Gate Drive Timing, Phase12Bootstrap Charge Management31Propagation Delay Timing13VREG Capacitor Selection31Logic Truth Tables14Supply Decoupling31Characteristic Performance15Braking31Functional Description16Current Sense Amplifier32Input and Output Terminal Functions16Input/Output Structures33Power Supplies17Layout Recommendations34Gate Drives17Package Outline Drawing35Logic Control Inputs19Current Sense Amplifiers20                                                                                                                                                                                                                                                                                                                                               | Gate Output Drive                 | 6  |                         |     |

| Logic Inputs and Outputs, Dynamic7Mask Register28Current Sense Amplifiers8Run Register29Uncommitted Operational Amplifier9Run Register29Protection10Application Information30Characteristic Definitions11Dead Time Selection30Timing Diagrams12Fault Blanking Time Selection30Serial Interface Timing12Bootstrap Capacitor Selection30Gate Drive Timing, CASTn12Bootstrap Charging30Gate Drive Timing, COASTn12Bootstrap Charge Management31Propagation Delay Timing13VREG Capacitor Selection31Logic Truth Tables14Supply Decoupling31Functional Description16Current Sense Amplifier32Input and Output Terminal Functions16Input/Output Structures33Power Supplies17Layout Recommendations34Gate Drives17Package Outline Drawing35Logic Control Inputs19202020                                                                                                                                                                                                                                                                                                                                                                                                       | Logic Inputs and Outputs          | 7  |                         |     |

| Current Sense Amplifiers8Run Register29Uncommitted Operational Amplifier9Application Information30Protection10Application Information30Characteristic Definitions11Dead Time Selection30Timing Diagrams12Fault Blanking Time Selection30Serial Interface Timing12Bootstrap Capacitor Selection30Gate Drive Timing, Phase12Bootstrap Charge Management31Propagation Delay Timing13VREG Capacitor Selection31Logic Truth Tables14Supply Decoupling31Functional Description16Current Sense Amplifier32Input and Output Terminal Functions16Input/Output Structures33Gate Drives17Layout Recommendations34Power Supplies17Layout Recommendations34Logic Control Inputs192020                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Logic Inputs and Outputs, Dynamic | 7  |                         |     |

| Discontinited Operational Amplifier90Application Information30Protection10Application Information30Characteristic Definitions11Dead Time Selection30Timing Diagrams12Fault Blanking Time Selection30Serial Interface Timing12Bootstrap Capacitor Selection30Gate Drive Timing, Phase12Bootstrap Charge Management31Gate Drive Timing, COASTn12Bootstrap Charge Management31Logic Truth Tables14Supply Decoupling31Characteristic Performance15Braking31Functional Description16Current Sense Amplifier32Input and Output Terminal Functions16Input/Output Structures33Gate Drives17Layout Recommendations34Gate Drives17Package Outline Drawing35Logic Control Inputs192035                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Current Sense Amplifiers          | 8  | 5                       |     |

| IndicatorIndicatorIndicatorIndicatorIndicatorCharacteristic Definitions11Dead Time Selection30Timing Diagrams12Fault Blanking Time Selection30Serial Interface Timing12Bootstrap Capacitor Selection30Gate Drive Timing, Phase12Bootstrap Charging30Gate Drive Timing, COASTn12Bootstrap Charge Management31Propagation Delay Timing13VREG Capacitor Selection31Logic Truth Tables14Supply Decoupling31Characteristic Performance15Braking31Functional Description16Current Sense Amplifier32Input and Output Terminal Functions16Input/Output Structures33Power Supplies17Layout Recommendations34Gate Drives17Package Outline Drawing35Logic Control Inputs192035                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Uncommitted Operational Amplifier | 9  | •                       |     |

| Characteristic Definitions11Fault Blanking Time Selection30Timing Diagrams12Bootstrap Capacitor Selection30Serial Interface Timing12Bootstrap Capacitor Selection30Gate Drive Timing, Phase12Bootstrap Charging30Gate Drive Timing, COASTn12Bootstrap Charge Management31Propagation Delay Timing13VREG Capacitor Selection31Logic Truth Tables14Supply Decoupling31Characteristic Performance15Braking31Functional Description16Current Sense Amplifier32Input and Output Terminal Functions16Input/Output Structures33Power Supplies17Layout Recommendations34Gate Drives17Package Outline Drawing35Logic Control Inputs202035                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Protection                        | 10 |                         |     |

| Initial plagrams12Bootstrap Capacitor Selection30Serial Interface Timing, Phase12Bootstrap Capacitor Selection30Gate Drive Timing, COASTn12Bootstrap Charge Management31Propagation Delay Timing13VREG Capacitor Selection31Logic Truth Tables14Supply Decoupling31Characteristic Performance15Braking31Functional Description16Current Sense Amplifier32Input and Output Terminal Functions16Input/Output Structures33Power Supplies17Layout Recommendations34Gate Drives19202035                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Characteristic Definitions        | 11 |                         |     |

| Gate Drive Timing, Phase12Bootstrap Charging30Gate Drive Timing, COASTn12Bootstrap Charge Management31Propagation Delay Timing13VREG Capacitor Selection31Logic Truth Tables14Supply Decoupling31Characteristic Performance15Braking31Functional Description16Current Sense Amplifier32Input and Output Terminal Functions16Input/Output Structures33Power Supplies17Layout Recommendations34Gate Drives17Package Outline Drawing35Logic Control Inputs192011                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Timing Diagrams                   | 12 | 5                       |     |

| Gate Drive Timing, Friase12Bootstrap Charge Management31Gate Drive Timing, COASTn12Bootstrap Charge Management31Propagation Delay Timing13VREG Capacitor Selection31Logic Truth Tables14Supply Decoupling31Characteristic Performance15Braking31Functional Description16Current Sense Amplifier32Input and Output Terminal Functions16Input/Output Structures33Power Supplies17Layout Recommendations34Gate Drives17Package Outline Drawing35Logic Control Inputs192011                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Serial Interface Timing           | 12 |                         |     |

| Propagation Delay Timing12VREG Capacitor Selection31Logic Truth Tables14Supply Decoupling31Characteristic Performance15Power Dissipation31Functional Description16Current Sense Amplifier32Input and Output Terminal Functions16Input/Output Structures33Power Supplies17Layout Recommendations34Gate Drives17Package Outline Drawing35Logic Control Inputs192010                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Gate Drive Timing, Phase          | 12 |                         |     |

| Logic Truth Tables14Supply Decoupling31Logic Truth Tables14Power Dissipation31Characteristic Performance15Braking31Functional Description16Current Sense Amplifier32Input and Output Terminal Functions16Input/Output Structures33Power Supplies17Layout Recommendations34Gate Drives17Package Outline Drawing35Logic Control Inputs192010                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Gate Drive Timing, COASTn         | 12 |                         |     |

| Logic Hult Tables14Power Dissipation31Characteristic Performance15Braking31Functional Description16Current Sense Amplifier32Input and Output Terminal Functions16Input/Output Structures33Power Supplies17Layout Recommendations34Gate Drives17Package Outline Drawing35Logic Control Inputs192011                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Propagation Delay Timing          | 13 |                         | ÷ · |

| Characteristic Performance15Braking31Functional Description16Current Sense Amplifier32Input and Output Terminal Functions16Input/Output Structures33Power Supplies17Layout Recommendations34Gate Drives17Package Outline Drawing35Logic Control Inputs192010                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Logic Truth Tables                | 14 |                         | • · |

| Functional Description16Current Sense Amplifier31Input and Output Terminal Functions16Input/Output Structures33Power Supplies17Layout Recommendations34Gate Drives17Package Outline Drawing35Logic Control Inputs1920                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Characteristic Performance        | 15 |                         | ÷ · |

| Input and Output Terminal Functions16Input/Output Structures33Power Supplies17Layout Recommendations34Gate Drives17Package Outline Drawing35Logic Control Inputs1920                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                   |    | 0                       | • • |

| Power Supplies17Layout Recommendations34Gate Drives17Package Outline Drawing35Logic Control Inputs1920                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | •                                 |    |                         |     |

| Gate Drives17Package Outline Drawing35Logic Control Inputs19Current Sense Amplifiers20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                   |    |                         |     |

| Logic Control Inputs 19<br>Current Sense Amplifiers 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                   |    | •                       |     |

| Current Sense Amplifiers 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                   |    | Package Outline Drawing | 35  |

| ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | •                                 |    |                         |     |

| Uncommitted Operational Amplifier 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | •                                 |    |                         |     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                   | 20 |                         |     |

#### THERMAL CHARACTERISTICS: May require derating at maximum conditions; see Power Dissipation section

| Characteristic Symbol Test Conditions*          |                       |                                                                 | Value | Unit |

|-------------------------------------------------|-----------------------|-----------------------------------------------------------------|-------|------|

| Package Thermal Resistance                      | D                     | On 4-layer PCB based on JEDEC standard                          | 23    | °C/W |

| (Junction to Ambient)                           | $R_{	extsf{	heta}JA}$ | On 2-layer PCB with 3 in. <sup>2</sup> of copper area each side | 44    | °C/W |

| Package Thermal Resistance<br>(Junction to Pad) | R <sub>θJP</sub>      |                                                                 | 2     | °C/W |

\*Additional thermal information available on the Allegro website.

3

# A4910

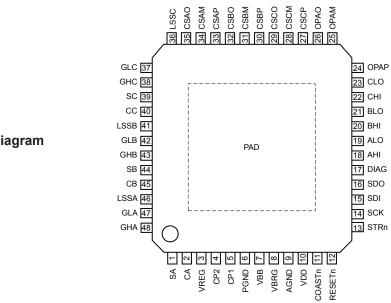

**Pinout Diagram**

#### **Terminal List Table**

| Name   | Number | Function                         | Name   | Number | Function                          |

|--------|--------|----------------------------------|--------|--------|-----------------------------------|

| AGND   | 9      | Analog ground                    | GHC    | 38     | High-side gate drive, phase C     |

| AHI    | 18     | Control input high side, phase A | GLA    | 47     | Low-side gate drive, phase A      |

| ALO    | 19     | Control input low side, phase A  | GLB    | 42     | Low-side gate drive, phase B      |

| BHI    | 20     | Control input high side, phase B | GLC    | 37     | Low-side gate drive, phase C      |

| BLO    | 21     | Control input low side, phase B  | LSSA   | 46     | Low-side source, phase A          |

| CA     | 2      | Bootstrap capacitor, phase A     | LSSB   | 41     | Low-side source, phase B          |

| СВ     | 45     | Bootstrap capacitor, phase B     | LSSC   | 36     | Low-side source, phase C          |

| CC     | 40     | Bootstrap capacitor, phase C     | OPAM   | 25     | Operational amplifier input –     |

| CHI    | 22     | Control input high side, phase C | OPAO   | 26     | Operational amplifier output      |

| CLO    | 23     | Control input low side, phase C  | OPAP   | 24     | Operational amplifier input +     |

| COASTn | 11     | Coast input                      | PAD    | -      | Exposed thermal pad               |

| CP1    | 5      | Pump capacitor                   | PGND   | 6      | Power ground                      |

| CP2    | 4      | Pump capacitor                   | RESETn | 12     | Standby mode control              |

| CSAM   | 34     | Current sense input –, phase A   | SA     | 1      | Motor connection, phase A         |

| CSAO   | 35     | Current sense output, phase A    | SB     | 44     | Motor connection, phase B         |

| CSAP   | 33     | Current sense input +, phase A   | SC     | 39     | Motor connection, phase C         |

| CSBM   | 31     | Current sense input –, phase B   | SCK    | 14     | Serial clock input                |

| CSBO   | 32     | Current sense output, phase B    | SDI    | 15     | Serial data input                 |

| CSBP   | 30     | Current sense input +, phase B   | SDO    | 16     | Serial data output                |

| CSCM   | 28     | Current sense input –, phase C   | STRn   | 13     | Serial strobe (chip select) input |

| CSCO   | 29     | Current sense output, phase C    | VBB    | 7      | Main power supply                 |

| CSCP   | 27     | Current sense input +, phase C   | VBRG   | 8      | High-side drain voltage sense     |

| DIAG   | 17     | Programmable diagnostic output   | VDD    | 10     | Logic supply                      |

| GHA    | 48     | High-side gate drive, phase A    | VREG   | 3      | Gate drive supply output          |

| GHB    | 43     | High-side gate drive, phase B    |        |        |                                   |

**Functional Block Diagram**

### **ELECTRICAL CHARACTERISTICS:** Valid at $T_J = -40^{\circ}$ C to 150°C, $V_{DD} = 5$ V, $V_{BB} = 5.5$ to 50 V, unless otherwise specified

| Characteristic                                 | Symbol                | Test Conditions                                                                                              | Min.                   | Тур. | Max.                   | Unit |

|------------------------------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------|------------------------|------|------------------------|------|

| SUPPLY AND REFERENCE                           |                       | ·                                                                                                            |                        |      |                        |      |

| VBB Functional Operating Range                 | V <sub>BB</sub>       |                                                                                                              | 5.5                    | _    | 50                     | V    |

|                                                | I <sub>BBQ</sub>      | RESETn = high, outputs low, V <sub>BB</sub> = 12 V                                                           | _                      | 10   | 14                     | mA   |

| VBB Quiescent Current                          | I <sub>BBS</sub>      | RESETn = low, sleep mode, V <sub>BB</sub> = 12 V                                                             | _                      | _    | 10                     | μA   |

| VDD Logic Supply                               | V <sub>DD</sub>       |                                                                                                              | 3.0                    | _    | 5.5                    | V    |

| VIDD Outlessent Ourset                         | I <sub>DDQ</sub>      | RESETn = high, outputs low                                                                                   | _                      | 10   | 13                     | mA   |

| VDD Quiescent Current                          | I <sub>DDS</sub>      | RESETn = low, sleep mode                                                                                     | _                      | _    | 10                     | μA   |

|                                                |                       | V <sub>BB</sub> > 9 V, I <sub>REG</sub> = 0 to 30 mA                                                         | 9                      | 13   | 13.8                   | V    |

|                                                |                       | 7.5 V < V <sub>BB</sub> $\leq$ 9 V, I <sub>REG</sub> = 0 to 20 mA                                            | 9                      | 13   | 13.8                   | V    |

| VREG Output Voltage                            | V <sub>REG</sub>      | $6 \text{ V} < \text{V}_{\text{BB}} \le 7.5 \text{ V}, \text{ I}_{\text{REG}} = 0 \text{ to } 15 \text{ mA}$ | 7.9                    | _    | _                      | V    |

|                                                |                       | 5.5 V < V <sub>BB</sub> ≤ 6 V, I <sub>REG</sub> < 9 mA                                                       | 7.9                    | 9.5  | _                      | V    |

|                                                |                       | I <sub>D</sub> = 10 mA                                                                                       | 0.4                    | 0.7  | 1.0                    | V    |

| Bootstrap Diode Forward Voltage                | V <sub>fBOOT</sub>    | I <sub>D</sub> = 100 mA                                                                                      | 1.5                    | 2.2  | 2.8                    | V    |

| Bootstrap Diode Resistance                     | r <sub>D</sub>        | $r_{D(100 \text{ mA})} = (V_{fBOOT(150 \text{ mA})} - V_{fBOOT(50 \text{ mA})})/$<br>100 mA                  | 6                      | 11   | 22                     | Ω    |

| Bootstrap Diode Current Limit                  | I <sub>DBOOT</sub>    |                                                                                                              | 250                    | 500  | 750                    | mA   |

| Top-Off Charge Pump Current Limit              | I <sub>TOCPM</sub>    |                                                                                                              | _                      | 100  | _                      | μA   |

| High-Side Gate Drive Static Load<br>Resistance | R <sub>GSH</sub>      |                                                                                                              | 250                    | _    | -                      | kΩ   |

| System Clock Period                            | t <sub>osc</sub>      |                                                                                                              | 45                     | 50   | 55                     | ns   |

| GATE OUTPUT DRIVE                              |                       |                                                                                                              | `                      |      |                        |      |

| Turn-On Time                                   | t <sub>r</sub>        | C <sub>LOAD</sub> = 10 nF, 20% to 80% points                                                                 | _                      | 190  | _                      | ns   |

| Turn-Off Time                                  | t <sub>f</sub>        | $C_{LOAD} = 10 \text{ nF}, 80\% \text{ to } 20\% \text{ points}$                                             | _                      | 120  | _                      | ns   |

|                                                | _                     | $T_{\rm J} = 25^{\circ}$ C, $I_{\rm GHx} = -150$ mA                                                          | 5                      | 8    | 11                     | Ω    |

| Pull-Up On-Resistance                          | R <sub>DS(on)UP</sub> | T <sub>J</sub> = 150°C, I <sub>GHx</sub> = –150 mA                                                           | 10                     | 15   | 20                     | Ω    |

|                                                | _                     | T <sub>J</sub> = 25°C, I <sub>GLx</sub> = 150 mA                                                             | 1.7                    | 2.5  | 3.1                    | Ω    |

| Pull-Down On-Resistance                        | R <sub>DS(on)DN</sub> | T <sub>J</sub> = 150°C, I <sub>GLx</sub> = 150 mA                                                            | 2.9                    | 4    | 5                      | Ω    |

| GHx Output Voltage (High)                      | V <sub>GHH</sub>      | Bootstrap capacitor fully charged                                                                            | V <sub>Cx</sub> - 0.2  | _    | _                      | V    |

| GHx Output Voltage (Low)                       | V <sub>GHL</sub>      | –10 μA < I <sub>GHx</sub> < 10 μA                                                                            | _                      | _    | V <sub>Sx</sub> + 0.3  | V    |

| GLx Output Voltage (High)                      | V <sub>GLH</sub>      |                                                                                                              | V <sub>REG</sub> – 0.2 | _    | -                      | V    |

| GLx Output Voltage (Low)                       | V <sub>GLL</sub>      | –10 μA < I <sub>GLx</sub> < 10 μA                                                                            | -                      | _    | V <sub>LSSx</sub> +0.3 | V    |

|                                                |                       | $V_{BB} = 0 V, V_{GHx} - V_{Sx} < 0.1 V$                                                                     | _                      | 950  | -                      | kΩ   |

| GHx Passive Pull-Down                          | R <sub>GHPD</sub>     | $V_{BB} = 0 \text{ V}, I_{GHx} = 500 \mu\text{A}$                                                            | _                      | 4    | _                      | kΩ   |

|                                                |                       | $V_{BB} = 0 V, V_{GLx} - V_{LSSx} < 0.1 V$                                                                   | _                      | 950  | _                      | kΩ   |

| GLx Passive Pull-Down                          | R <sub>GLPD</sub>     | $V_{BB} = 0 V, I_{GLx} = 500 \mu A$                                                                          |                        | 4    | _                      | kΩ   |

### **ELECTRICAL CHARACTERISTICS** (continued): Valid at $T_J = -40^{\circ}$ C to 150°C, $V_{DD} = 5$ V, $V_{BB} = 5.5$ to 50 V, unless otherwise specified

| Characteristic                                 | Symbol              | Test Conditions                                                    | Min.                  | Тур.                  | Max.                                  | Unit |

|------------------------------------------------|---------------------|--------------------------------------------------------------------|-----------------------|-----------------------|---------------------------------------|------|

| GATE OUTPUT DRIVE (continued)                  | )                   |                                                                    |                       |                       |                                       |      |

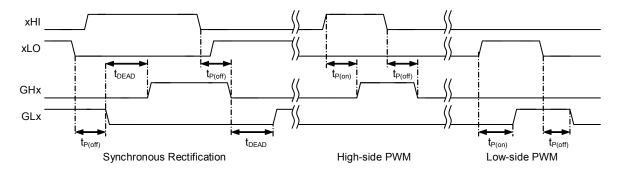

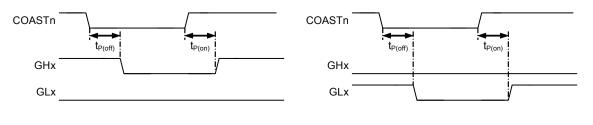

| Turn-Off Propagation Delay                     | t <sub>P(off)</sub> | Input change to unloaded gate output change (see figure 5)         | 60                    | 90                    | 140                                   | ns   |

| Turn-On Propagation Delay                      | t <sub>P(on)</sub>  | Input change to unloaded gate output change (see figure 5)         | 50                    | 80                    | 130                                   | ns   |

| Propagation Delay Matching<br>(Phase-to-Phase) | ∆t <sub>PP</sub>    | Same phase change, DT[60] = 0                                      | -                     | 5                     | 15                                    | ns   |

| Propagation Delay Matching<br>(On-to-Off)      | Δt <sub>OO</sub>    | Single phase, DT[60] = 0                                           | -                     | 15                    | 30                                    | ns   |

| Propagation Delay Matching<br>(GHx-to-GLx)     | $\Delta t_{\rm HL}$ | Rising to rising edges, falling to falling edges,<br>DT[60] = 0    | -                     | _                     | 20                                    | ns   |

| LOGIC INPUTS AND OUTPUTS                       |                     |                                                                    |                       | ~                     | · · · · · · · · · · · · · · · · · · · |      |

|                                                | N                   | RESETn pin                                                         | -                     | _                     | 0.2 × V <sub>DD</sub>                 | V    |

| Input Low Voltage                              | V <sub>IL</sub>     | All other logic pins                                               | -                     | _                     | 0.3 × V <sub>DD</sub>                 | V    |

| Input High Voltage                             | V <sub>IH</sub>     |                                                                    | 0.7 × V <sub>DD</sub> | _                     | _                                     | V    |

|                                                |                     | RESETn pin                                                         | 200                   | 350                   | _                                     | mV   |

| Input Hysteresis                               | V <sub>lhys</sub>   | All other logic pins                                               | 250                   | 500                   | _                                     | mV   |

| Input Pull-Up Resistor                         | R <sub>PU</sub>     | STRn                                                               | 30                    | 50                    | 70                                    | kΩ   |

| Input Pull-Down Resistor                       | R <sub>PD</sub>     | COASTn, RESETn, SCK, SDI, AHI, ALO, BHI,<br>BLO, CHI, and CLO pins | 30                    | 50                    | 70                                    | kΩ   |

| Output Low Voltage                             | V <sub>OL</sub>     | I <sub>OL</sub> = 1 mA                                             | -                     | 0.2                   | 0.4                                   | V    |

| Output High Voltage <sup>1</sup>               | V <sub>OH</sub>     | $I_{OL} = -1 \text{ mA}$                                           | V <sub>DD</sub> - 0.4 | V <sub>DD</sub> - 0.2 | _                                     | V    |

| Output Leakage (SDO pin) <sup>1</sup>          | I <sub>SDOlkg</sub> | 0 V < V <sub>SDO</sub> < V <sub>DD</sub> , STRn = 1                | -1                    | _                     | 1                                     | μA   |

| LOGIC INPUTS AND OUTPUTS DY                    | NAMIC PARA          | METERS                                                             |                       | ·                     | · · · · · · · · · · · · · · · · · · · |      |

| Reset Pulse Width                              | t <sub>RST</sub>    |                                                                    | 0.2                   | _                     | 4.5                                   | μs   |

| Reset Shutdown Time                            | t <sub>RSD</sub>    |                                                                    | 10                    | _                     | -                                     | μs   |

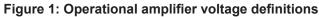

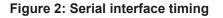

| Clock High Time                                | t <sub>scкн</sub>   | A in Figure 2                                                      | 50                    | _                     | _                                     | ns   |

| Clock Low Time                                 | t <sub>SCKL</sub>   | B in Figure 2                                                      | 50                    | _                     | -                                     | ns   |

| Strobe Lead Time                               | t <sub>STLD</sub>   | C in Figure 2                                                      | 30                    | _                     | _                                     | ns   |

| Strobe Lag Time                                | t <sub>STLG</sub>   | D in Figure 2                                                      | 30                    | _                     | _                                     | ns   |

| Strobe High Time                               | t <sub>STRH</sub>   | E in Figure 2                                                      | 300                   | _                     | _                                     | ns   |

| Data Out Enable Time                           | t <sub>SDOE</sub>   | F in Figure 2                                                      | -                     | _                     | 40                                    | ns   |

| Data Out Disable Time                          | t <sub>SDOD</sub>   | G in Figure 2                                                      | -                     | _                     | 30                                    | ns   |

| Data Out Valid Time from<br>Clock Falling      | t <sub>SDOV</sub>   | H in Figure 2                                                      | -                     | _                     | 40                                    | ns   |

| Data Out Hold Time from<br>Clock Falling       | t <sub>SDOH</sub>   | I in Figure 2                                                      | 5                     | _                     | _                                     | ns   |

### **ELECTRICAL CHARACTERISTICS** (continued): Valid at $T_J = -40^{\circ}$ C to $150^{\circ}$ C, $V_{DD} = 5$ V, $V_{BB} = 5.5$ to 50 V, unless otherwise specified

| Characteristic                             | Symbol                  | Test Conditions                                                                                                                                                                                      | Min. | Тур. | Max.                                  | Unit  |

|--------------------------------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|---------------------------------------|-------|

| LOGIC INPUTS AND OUTPUTS DYNA              | AMIC PARA               | METERS (continued)                                                                                                                                                                                   |      |      |                                       |       |

| Data In Set-Up Time to Clock Rising        | t <sub>SDIS</sub>       | J in Figure 2                                                                                                                                                                                        | 15   | _    | -                                     | ns    |

| Data In Hold Time from Clock Rising        | t <sub>SDIH</sub>       | K in Figure 2                                                                                                                                                                                        | 10   | -    | -                                     | ns    |

| Wake Up from Reset                         | t <sub>EN</sub>         | RESETn high to POR bit set                                                                                                                                                                           | _    | _    | 1                                     | ms    |

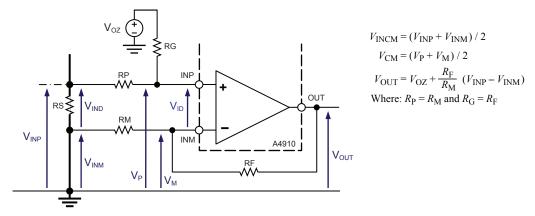

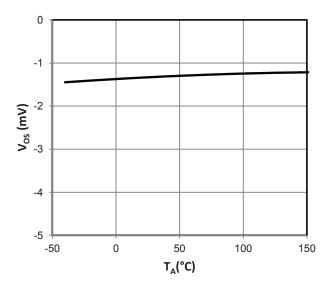

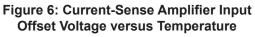

| CURRENT SENSE AMPLIFIERS <sup>2</sup> (ref | er to Figure            | 1 for definitions)                                                                                                                                                                                   |      | ·    | · · · · · · · · · · · · · · · · · · · |       |

| Input Offset Voltage                       | V <sub>IOS(SA)</sub>    |                                                                                                                                                                                                      | -10  | _    | +10                                   | mV    |

| Input Offset Voltage Drift <sup>3</sup>    | ΔV <sub>IOS(SA)</sub>   |                                                                                                                                                                                                      | _    | ±10  | -                                     | µV/°C |

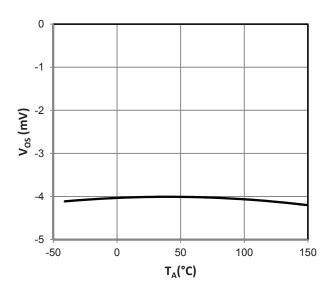

| Input Bias Current <sup>1</sup>            | I <sub>BIAS(SA)</sub>   | $0 V < V_{P} < V_{DD}, 0 V < V_{M} < V_{DD}$                                                                                                                                                         | -1   | 0    | +1                                    | μA    |

| Input Offset Current <sup>1</sup>          | I <sub>OS(SA)</sub>     | V <sub>ID</sub> = 0 V, V <sub>CM</sub> in range                                                                                                                                                      | -1   | -    | +1                                    | μA    |

| Input Common-Mode Range (DC)               | V <sub>CM(SA)</sub>     | $V_{ID} = 0 V$                                                                                                                                                                                       | -1   | -    | 2                                     | V     |

| Differential Input Voltage                 | V <sub>ID(SA)</sub>     |                                                                                                                                                                                                      | _    | -    | 200                                   | mV    |

| Open Loop Gain <sup>3</sup>                | A <sub>VOL(SA)</sub>    | V <sub>CM</sub> in range                                                                                                                                                                             | 80   | 100  | -                                     | dB    |

| Closed Loop Gain                           | A <sub>VCL(SA)</sub>    | V <sub>CM</sub> in range                                                                                                                                                                             | 5    | -    | -                                     | V/V   |

|                                            | DW                      | Gain = 20, $V_{IND}$ = 10 m $V_{pp}$ , $R_P$ = $R_M$ = 4 k $\Omega$ , CSB bit = 1                                                                                                                    | 500  | -    | -                                     | kHz   |