# **Description**

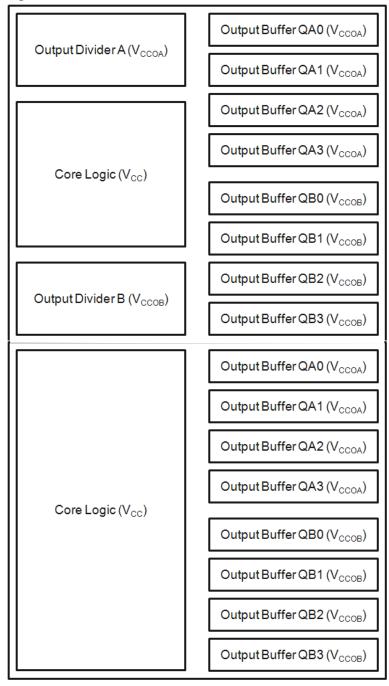

The device is intended to take 1 or 2 reference clocks, select between them, using a pin or register selection and generate up to 8 outputs that may be the same as the reference frequency or integer-divider versions of it.

The 8P79818 supports two output banks, each with its own divider and power supply. All outputs in one bank would generate the same output frequency, but each output can be individually controlled for output type, output enable or even powered-off.

The device supports a serial port for configuration of the parameters while in operation. The serial port can be selected to use the I<sup>2</sup>C or SPI protocol. After power-up, all outputs will come up in LVDS mode and may be programmed to other configurations over the serial port. Outputs may be enabled or disabled under control of the OE input pin.

The device can operate over the -40°C to +85°C temperature range.

#### **Features**

- Two differential inputs support LVPECL, LVDS, HCSL or LVCMOS reference clocks

- Accepts input frequencies ranging from 1PPS (1Hz) to 700MHz

- Select which of the two input clocks is to be used as the reference clock for which divider via pin or register selection

- Switchover will not generate any runt clock pulses on the output

- Generates eight differential outputs or eight LVCMOS outputs, Bank A only

- Differential outputs selectable as LVPECL, LVDS, CML or **HCSL**

- Differential outputs support frequencies from 1PPS to 700MHz

- LVCMOS outputs support frequencies from 1PPS to 200MHz

- LVCMOS outputs in the same pair may be inverted or in-phase relative to one another

- Outputs arranged in 2 banks of 4 outputs each

- Each bank supports a separate power supply of 3.3V, 2.5V or 1.8V

- 1.5V output voltage is also supported for LVCMOS, Bank A

- One divider per output bank, supporting divide ratios of 2...511 or divider bypass

- Output enable control pin

- Output enable or disable will not cause any runt pulses

- Register programmable via I<sup>2</sup>C / SPI serial port

- Individual output enables, output type selection and output power-down control bits supported

- Input mux selection control bit

- Core voltage supply of 3.3V, 2.5V or 1.8V

- -40°C to +85°C ambient operating temperature

- Lead-free (RoHS 6) packaging

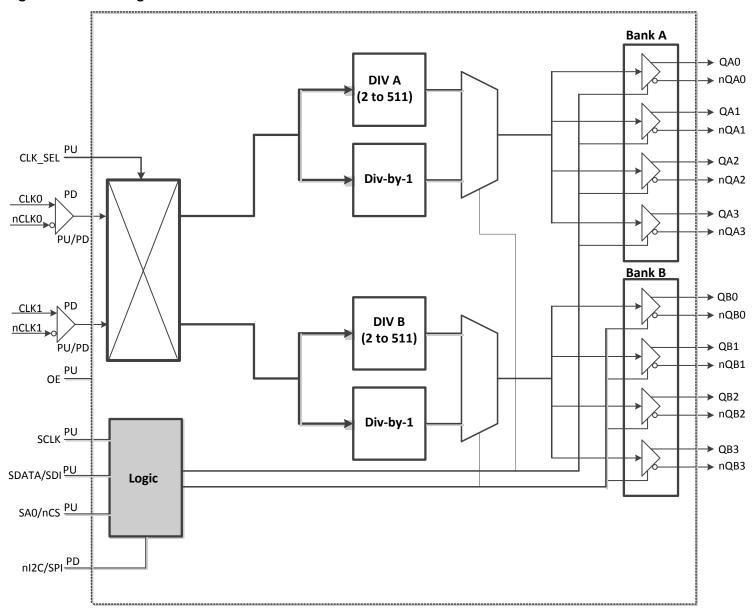

# **Block Diagram**

Figure 1: Block Diagram

8P79818 transistor count: 33,394

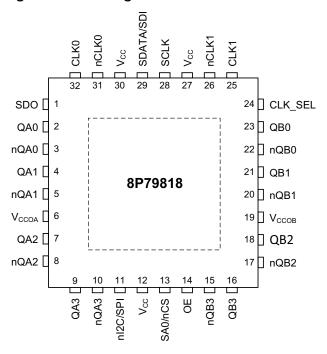

# **Pin Assignment**

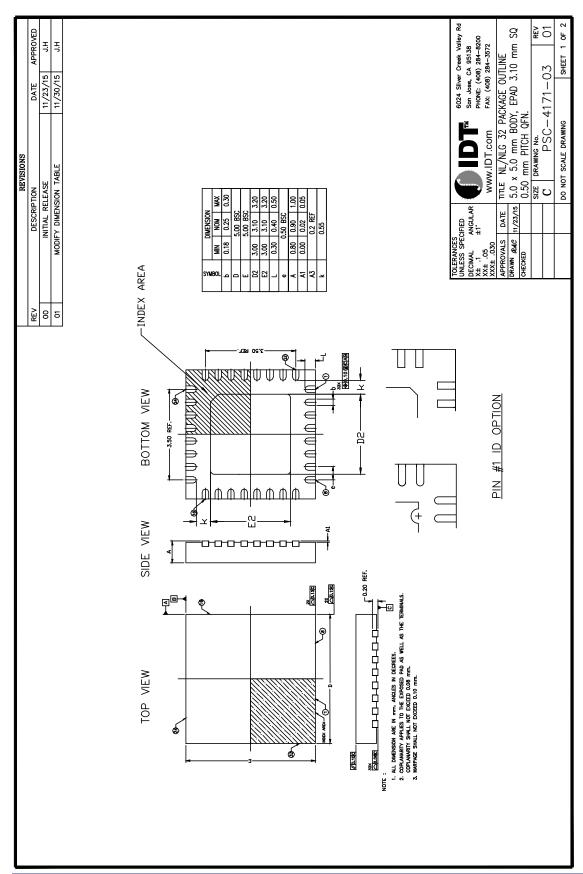

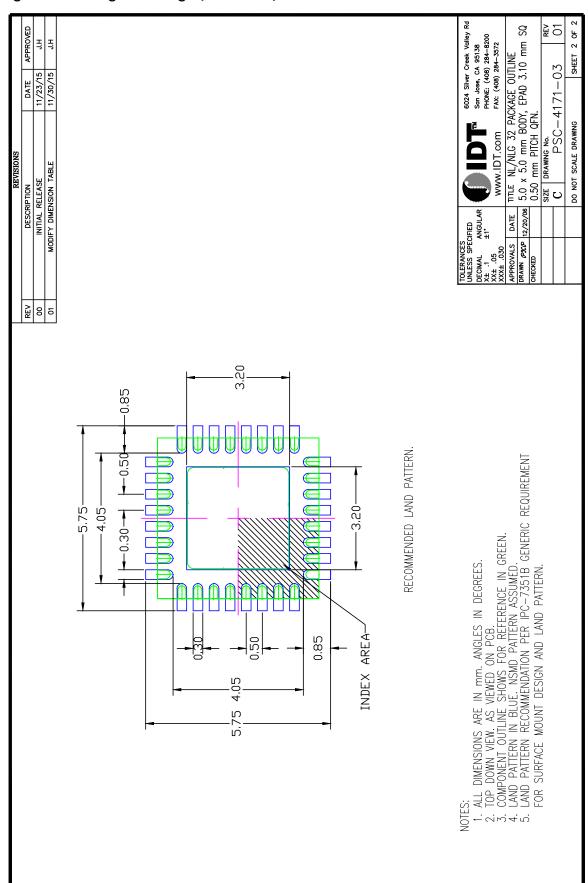

Figure 2: Pin Assignments for 5mm x 5mm 32-Lead VFQFN Package (Top View)

# **Pin Description and Characteristic Tables**

**Table 1: Pin Description**

| Number | Name              | Type <sup>[a]</sup> | Description                                                                                          |

|--------|-------------------|---------------------|------------------------------------------------------------------------------------------------------|

| 1      | SDO               | Output              | SPI mode data output signal. Unused in I <sup>2</sup> C mode.                                        |

| 2      | QA0               | Output              | Positive differential clock output. Included in Bank A. Refer to Output Drivers section for details. |

| 3      | nQA0              | Output              | Negative differential clock output. Included in Bank A. Refer to Output Drivers section for details. |

| 4      | QA1               | Output              | Positive differential clock output. Included in Bank A. Refer to Output Drivers section for details. |

| 5      | nQA1              | Output              | Negative differential clock output. Included in Bank A. Refer to Output Drivers section for details. |

| 6      | V <sub>CCOA</sub> | Power               | Output supply for output Bank A.                                                                     |

| 7      | QA2               | Output              | Positive differential clock output. Included in Bank A. Refer to Output Drivers section for details. |

| 8      | nQA2              | Output              | Negative differential clock output. Included in Bank A. Refer to Output Drivers section for details. |

| 9      | QA3               | Output              | Positive differential clock output. Included in Bank A. Refer to Output Drivers section for details. |

| 10     | nQA3              | Output              | Negative differential clock output. Included in Bank A. Refer to Output Drivers section for details. |

|        |                   |                     | Select protocol for serial port:                                                                     |

| 11     | nI2C/SPI          | Input (PD)          | 0 = I <sup>2</sup> C mode                                                                            |

|        |                   |                     | 1 = SPI mode                                                                                         |

| 12     | V <sub>CC</sub>   | Power               | Core logic supply.                                                                                   |

| 13     | SA0/nCS           | Input (PU)          | SPI chip select input (active low) in SPI mode. Base address bit 0 in I <sup>2</sup> C mode.         |

## **Table 1: Pin Description (Cont.)**

|    |                   |                                    | Master output enable control                                                                                                                     |  |  |  |  |  |

|----|-------------------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 14 | OE                | OE Input (PU)                      | 0 = All outputs high-impedance                                                                                                                   |  |  |  |  |  |

|    |                   |                                    | 1 = All outputs enabled or disabled under control of register bits                                                                               |  |  |  |  |  |

| 15 | nQB3              | Output                             | Negative differential clock output. Included in Bank B. Refer to Output Drivers section for details.                                             |  |  |  |  |  |

| 16 | QB3               | Output                             | Positive differential clock output. Included in Bank B. Refer to Output Drivers section for details.                                             |  |  |  |  |  |

| 17 | nQB2              | Output                             | Negative differential clock output. Included in Bank B. Refer to Output Drivers section for details.                                             |  |  |  |  |  |

| 18 | QB2               | Output                             | Positive differential clock output. Included in Bank B. Refer to Output Drivers section for details.                                             |  |  |  |  |  |

| 19 | V <sub>CCOB</sub> | Power                              | Output supply for output Bank B.                                                                                                                 |  |  |  |  |  |

| 20 | nQB1              | Output                             | Negative differential clock output. Included in Bank B. Refer to Output Drivers section for details.                                             |  |  |  |  |  |

| 21 | QB1               | Output                             | Positive differential clock output. Included in Bank B. Refer to Output Drivers section for details.                                             |  |  |  |  |  |

| 22 | nQB0              | Output                             | Negative differential clock output. Included in Bank B. Refer to Output Drivers section for details.                                             |  |  |  |  |  |

| 23 | QB0               | Output                             | Positive differential clock output. Included in Bank B. Refer to Output Drivers section for details.                                             |  |  |  |  |  |

| 24 | CLK_SEL           | Input (PU)                         | Input clock selection control pin. This pin may be disabled by register control, but if enabled (default) its function is:  0 = CLK0 is selected |  |  |  |  |  |

|    |                   |                                    | 1 = CLK1 is selected                                                                                                                             |  |  |  |  |  |

| 25 | CLK1              | Input (PD)                         | Non-inverting differential clock input.                                                                                                          |  |  |  |  |  |

| 26 | nCLK1             | Input (PU/ PD)                     | Inverting differential clock input. $V_{\rm CC}/2$ when left floating (set by the internal pull-up and pull-down resistors).                     |  |  |  |  |  |

| 27 | V <sub>CC</sub>   | Power                              | Core logic supply.                                                                                                                               |  |  |  |  |  |

| 28 | SCLK              | Input (PU)                         | Serial port input clock for either SPI or I <sup>2</sup> C mode.                                                                                 |  |  |  |  |  |

| 29 | SDATA/<br>SDI     | Input/Output<br>(PU)<br>Input (PU) | In I <sup>2</sup> C mode, this is the bi-directional data signal for the serial port In SPI mode, this is the data input signal.                 |  |  |  |  |  |

| 30 | V <sub>CC</sub>   | Power                              | Core logic supply.                                                                                                                               |  |  |  |  |  |

| 31 | nCLK0             | Input (PU/ PD)                     | Inverting differential clock input. $V_{\rm CC}/2$ when left floating (set by the internal pull-up and pull-down resistors).                     |  |  |  |  |  |

| 32 | CLK0              | Input (PD)                         | Non-inverting differential clock input.                                                                                                          |  |  |  |  |  |

| EP | V <sub>EE</sub>   | Ground                             | Must be connected to ground (GND).                                                                                                               |  |  |  |  |  |

|    | I .               | 1                                  |                                                                                                                                                  |  |  |  |  |  |

a. Pull-up (PU) and pull-down (PD) resistors are indicated in parentheses. *Pullup* and *Pulldown* refer to internal input resistors. See Table 10, *DC Input/ Output Characteristics*, for typical values.

## **Principles of Operation**

#### **Input Selection**

The 8P79818 supports two input references: CLK0 and CLK1 that may be driven with differential or single-ended clock signals. Either or both may be used as the source frequency for either output divider under control of the CLK. SEL input pin or under register control.

The CLK\_SEL pin is the default selection mechanism and selects whether both dividers are driven by the CLK0, nCLK0 input (CLK\_SEL = Low) or by the CLK1, nCLK1 input (CLK\_SEL = High).

If the user enables register control via the SEL\_REG control bit, then there are 4 selection options available as shown in Table 2.

Table 2: Input Selection Register Control (SEL\_REG = 1)

| CLK_S | EL [1:0] | Description                                             |

|-------|----------|---------------------------------------------------------|

| 0     | 0        | Divider A & B both driven from CLK0                     |

| 0     | 1        | Divider A driven from CLK1 & Divider B driven from CLK0 |

| 1     | 0        | Divider A driven from CLK0 & Divider B driven from CLK1 |

| 1     | 1        | Divider A & B both driven from CLK1                     |

### **Output Dividers**

Each bank of outputs has its own divider. All outputs in the same bank will be driven by that divider and so will all have the same frequency. Divider A supplies the QA output bank and Divider B supplies the QB output bank. Each divider is capable of being driven by the same or a different input frequency. Each divider can pass that input frequency directly to the outputs or to divide it by any integer from 2 up to 511.

## **Output Drivers**

The QA[0:3] and QB[0:3] clock outputs are provided with register-controlled output drivers. By selecting the output drive type in the appropriate register, any of these outputs can support LVCMOS, LVPECL, CML, HCSL or LVDS logic levels.

CML operation supports both a 400mV peak-peak swing and an 800mV peak-peak swing selection.

The operating voltage ranges of each output bank is determined by its independent output power pin ( $V_{CCOA}$  or  $V_{CCOB}$ ). Output voltage levels of 1.8V, 2.5V or 3.3V are supported for differential operation and LVCMOS operation. In addition, LVCMOS output operation supports 1.5V  $V_{CCO}$ .

A global OE input pin is provided. If the OE pin is negated (Low), then all outputs will be in a high-impedance state. If the OE pin is asserted (High), then each output will behave as indicated by its individual register enable bit. Using the global OE pin to enable or disable outputs will not result in any 'runt' clock pulses on the outputs.

Each output bank may be enabled or disabled using the SYNC\_DISx register bit. Using these bits to enable or disable outputs will not result in any 'runt' clock pulses on the outputs.

Individual outputs within a bank may be enabled or disabled using the DIS\_Qxm register bits. These bits however may result in 'runt' pulses on the outputs if the output is otherwise enabled, so it is recommended that the entire bank be disabled via the appropriate SYNC\_DISx register bit while an individual output is being enabled using the DIS\_Qxm bit to avoid a possible 'runt' pulse on the output. If 'runt' pulses are not a concern, then the DIS\_Qxm bits may be used directly.

#### **LVCMOS Operation**

When a given output is configured to provide LVCMOS levels, then both the Q and nQ outputs will toggle at the selected output frequency. All the previously described configuration and control apply equally to both outputs. Frequency, voltage levels and enable / disable status apply to both the Q and nQ pins.

When configured as LVCMOS, the Q & nQ outputs can be selected to be phase-aligned with each other or inverted relative to one another. Phase-aligned outputs will have increased simultaneous switching currents which can negatively affect phase noise performance and power consumption. It is recommended that use of this selection be kept to a minimum.

### **Power-Saving Modes**

To allow the device to consume the least power possible for a given application, the following functions are included under register control:

- Any unused output can be individually powered-off.

- If either bank is completely unused, all logic, including the dividers for that bank may be completely powered-off.

- Clock gating on logic that is not being used.

### **Device Start-up Behavior**

The device will power-up with all outputs enabled in LVDS mode and all dividers bypassed.

## **Serial Control Port Description**

## **Serial Control Port Configuration Description**

The device has a serial control port capable of responding as a slave in an  $I^2C$  or SPI compatible configuration, to allow access to any of the internal registers for device programming or examination of internal status. All registers are configured to have default values. See the specifics for each register for details. Selection of  $I^2C$  versus SPI protocol will be done via the nI2C/SPI input pin.

## **SPI Mode Operation**

SPI mode can be enabled via pin selection from power-up. The following information assumes SPI mode has been selected.

In a read operation (R/W bit is '1'), data on SDO will be clocked out on the falling edge of SCLK.

In a write operation (R/W bit is '0'), data on SDI will be clocked in on the rising edge of SCLK.

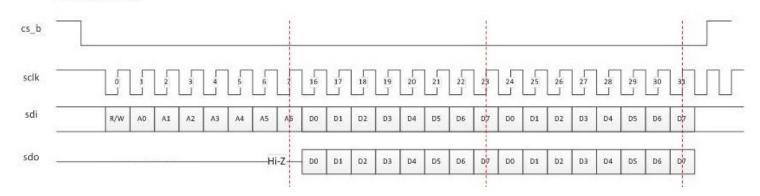

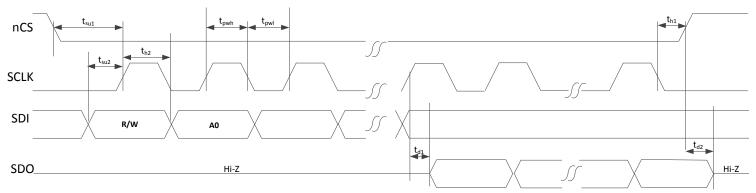

Figure 3: SPI Read Sequencing Diagram

Read (LSB first)

During SPI Write operations, the user may continue to hold nCS low and provide further bytes of data for up to a total of 16 bytes in a single block write. Data is written directly into the appropriate register as it is received.

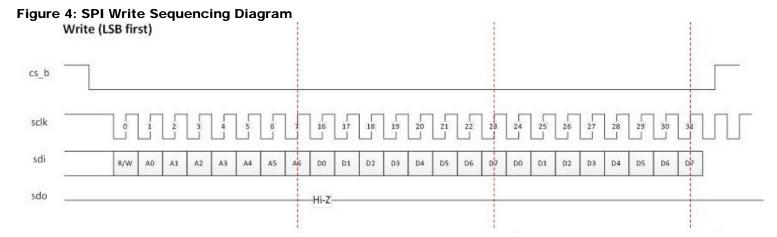

Figure 5: SPI Read/Write Timing Diagram

Table 3: Timing Characteristics in SPI Mode<sup>[a]</sup>

| Symbol           | Parameter                                                                                       | Min | Тур | Max | Unit |

|------------------|-------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>pw</sub>  | SCLK Period                                                                                     | 20  |     |     | ns   |

| t <sub>pw1</sub> | SCLK Pulse Width Low                                                                            | 8   |     |     | ns   |

| t <sub>pw2</sub> | SCLK Pulse Width High                                                                           | 8   |     |     | ns   |

| t <sub>su1</sub> | Valid nCS to SCLK Rising Setup Time                                                             | 10  |     |     | ns   |

| t <sub>h1</sub>  | Valid nCS After Valid SCLK Hold Time (CLKE = 0/1)                                               | 10  |     |     | ns   |

| t <sub>su2</sub> | Valid SDI to SCLK Rising Setup Time                                                             | 5   |     |     | ns   |

| t <sub>h2</sub>  | Valid SDI after valid SCLK Hold Time                                                            | 5   |     |     | ns   |

| t <sub>d1</sub>  | SCLK falling (rising in CLKE = 1 case) to Valid Data Delay Time                                 |     |     | 5   | ns   |

| t <sub>d2</sub>  | nCS rising edge to SDO High Impedance Delay Time                                                |     |     | 10  | ns   |

| t <sub>csh</sub> | Time between Consecutive Read-Read or Read-Write Accesses (nCS rising edge to nCS falling edge) | 20  |     |     | ns   |

a. Specifications guaranteed by design and characterization.

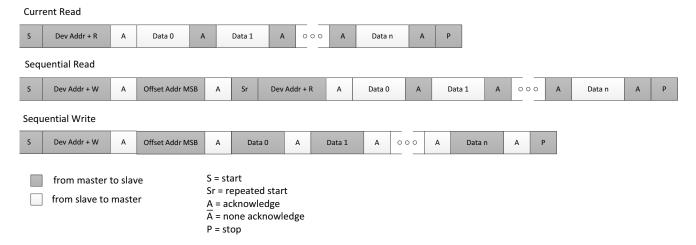

# I<sup>2</sup>C Mode Operation

The I<sup>2</sup>C interface is designed to fully support v1.0 of the I<sup>2</sup>C specification for *normal* and *fast* mode operation. The device acts as a slave device on the I<sup>2</sup>C bus at 100kHz or 400kHz using an address of 110110x (binary), where the value of 'x' is set by the SA0/nCS input pin. The interface accepts byte-oriented block write and block read operations. One address byte specifies the register address of the byte position of the first register to write or read. Data bytes (registers) are accessed in sequential order from the lowest to the highest byte (most significant bit first). Read and write block transfers can be stopped after any complete byte transfer. During a write operation, data will be written to the registers directly as each byte is received.

For full electrical I<sup>2</sup>C compliance, it is recommended to use external pull-up resistors for SDATA and SCLK. The internal pull-up resistors have a size of  $51k\Omega$  typical.

Figure 6: Slave Read and Write Cycle Sequencing

# **Register Descriptions**

## Table 4: Register Blocks

| Register Ranges Offset (Hex) | Register Block Description |

|------------------------------|----------------------------|

| 0 – 1                        | Device control             |

| 2 – 5                        | Bank A control             |

| 6 – 9                        | Bank B control             |

| A – B                        | Reserved                   |

| C – F                        | Divide ratios              |

## **Table 5: Device Control Register Bit Field Locations**

| Address (Hex) | D7      | D6           | D5        | D4        | D3      | D2      | D1       | D0       |

|---------------|---------|--------------|-----------|-----------|---------|---------|----------|----------|

| 0             | CLKMODE | CLK_SEL[1:0] |           | SEL_REG   | Rsvd    | Rsvd    | Rsvd     | DIV_SYNC |

| 1             | BKA_Vx  | BKB_Vx       | SYNC_DISA | SYNC_DISB | PWR_DNA | PWR_DNB | DIS_DIVA | DIS_DIVB |

| Bit Field Name | Field Type | Default Value | Description                                                                                                                                                                                                                                                     |

|----------------|------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                |            |               | Clock switchover mode selection:                                                                                                                                                                                                                                |

| CLKMODE        | R/W        | 0b            | 0 = Forced clock switch (may result in glitches as clocks switch)                                                                                                                                                                                               |

| GENWOBE        | 17,44      | ob            | 1 = Glitch-less clock switch (may remain on original clock source if that source is no longer toggling)                                                                                                                                                         |

|                |            |               | Select which input clock is to be used as the reference clock. These bits are only in effect when SEL_REG = 1:                                                                                                                                                  |

| CLK_SEL[1:0]   | R/W        | 00b           | 00 = CLK0, nCLK0 input drives both Divider A & Divider B 01 = CLK1, nCLK1 input drives Divider A & CLK0, nCLK0 drives Divider B 10 = CLK0, nCLK0 input drives Divider A & CLK1, nCLK1 drives Divider B 11 = CLK1, nCLK1 input drives both Divider A & Divider B |

|                |            |               | Determines if input clock selection is to be performed by pin or register:                                                                                                                                                                                      |

| SEL_REG        | R/W        | 0b            | 0 = CLK_SEL input pin controls reference selection mux 1 = CLK_SEL register bits controls reference selection mux                                                                                                                                               |

| Rsvd           | R/W        | _             | Reserved. Always write '0' to this bit location. Read values are not defined.                                                                                                                                                                                   |

| <del></del>    |            |               | Divider synchronization control:                                                                                                                                                                                                                                |

| DIV_SYNC       | R/W        | 0b            | 0 = Dividers running normally 1 = Dividers in reset (output clocks halted) 1->0 transition on this bit will synchronize the Bank A & Bank B output dividers                                                                                                     |

|                |            |               | Bank A voltage setting for optimal performance:                                                                                                                                                                                                                 |

| BKA_Vx         | R/W        | 0b            | $0 = V_{CCOA}$ is 3.3V                                                                                                                                                                                                                                          |

|                |            |               | 1 = V <sub>CCOA</sub> is 2.5V,1.8V, and 1.5V                                                                                                                                                                                                                    |

|                |            |               | Bank B voltage setting for optimal performance:                                                                                                                                                                                                                 |

| BKB_Vx         | R/W        | 0b            | 0 = V <sub>CCOB</sub> is 3.3V                                                                                                                                                                                                                                   |

|                |            |               | $1 = V_{CCOB}$ is 2.5V,1.8V                                                                                                                                                                                                                                     |

|                |            |               | Glitch-free output enable bit for Bank A outputs:                                                                                                                                                                                                               |

| SYNC_DISA      | R/W        | 0b            | 0 = Outputs in Bank A are enabled glitch-lessly as indicated by their individual DIS_QAm bits 1 = All outputs for Bank A are high-impedance                                                                                                                     |

|                |            |               | Glitch-free output enable bit for Bank B outputs:                                                                                                                                                                                                               |

| SYNC_DISB      | R/W        | 0b            | 0 = Outputs in Bank B are enabled glitch-lessly as indicated by their individual DIS_QBm bits 1 = All outputs for Bank B are high-impedance                                                                                                                     |

| Bit Field Name | Field Type | Default Value | Description                                                                                                                                                                                                   |

|----------------|------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PWR_DNA        | R/W        | 0b            | Power-down control for Bank A outputs:  0 = All outputs for Bank A are powered (SYNC_DISA should be 1 when powering-up the bank to prevent glitches on the output)  1 = All outputs in Bank A are powered-off |

| PWR_DNB        | R/W        | 0b            | Power-down control for Bank B outputs:  0 = All outputs for Bank B are powered (SYNC_DISB should be 1 when powering-up the bank to prevent glitches on the output)  1 = All outputs in Bank B are powered-off |

| DIS_DIVA       | R/W        | 0b            | Power-down output divider for Bank A (DIVA must be set to 000h to bypass):  0 = Output divider for Bank A is powered  1 = Output divider for Bank A is powered-down                                           |

| DIS_DIVB       | R/W        | 0b            | Power-down output divider for Bank B (DIVB must be set to 000h to bypass):  0 = Output divider for Bank B is powered  1 = Output divider for Bank B is powered-down                                           |

## **Table 6: Bank A Control Register Bit Field Locations**

| Address (Hex) | D7              | D6   | D5            | D4      | D3            | D2            | D1      | D0      |

|---------------|-----------------|------|---------------|---------|---------------|---------------|---------|---------|

| 2             |                 | Rsvd |               | TERM_A  | QA_POL3       | QA_POL2       | QA_POL1 | QA_POL0 |

| 3             | Rs              | svd  | MODE_QA3[2:0] |         | MODE_QA2[2:0] |               |         |         |

| 4             | Rsvd            |      | MODE_QA1[2:0] |         | ]             | MODE_QA0[2:0] |         |         |

| 5             | DIS_QA3 DIS_QA2 |      | DIS_QA1       | DIS_QA0 |               | Rs            | svd     |         |

| Bit Field Name | Field Type | Default Value | Description                                                                                                                                                                                           |

|----------------|------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TERM_A         | R/W        | 0b            | Indicates termination used on Bank A outputs when HCSL mode is selected: $0=33\Omega/50\Omega$ $1=50\Omega$                                                                                           |

| QA_POLm        | R/W        | 0h            | Output polarity selection for output pair nQAm, QAm in LVCMOS mode:  0 = nQAm pin is inverted relative to QAm pin when in LVCMOS mode  1 = nQAm and QAm pins are in-phase when in LVCMOS mode         |

| MODE_QAm[2:0]  | R/W        | 010b          | Output driver mode of operation for output pair QAm, nQAm:  000 = high-impedance 001 = LVPECL 010 = LVDS (default) 011 = LVCMOS 100 = HCSL 101 = CML 400mV swing 110 = CML 800mV swing 111 = Reserved |

| DIS_QAm        | R/W        | 0b            | Disable output pair QAm, nQAm:  0 = Output pair QAm, nQAm is enabled (disable output bank using SYNC_DISA to prevent runt pulses when enabling)  1 = Output pair QAm, nQAm is powered-down            |

| Rsvd           | R/W        | -             | Reserved. Always write 0 to this bit location. Read values are not defined.                                                                                                                           |

## Table 7: Bank B Control Register Bit Field Locations

| Address (Hex) | D7              | D6   | D5            | D4           | D3            | D2   | D1           | D0   |

|---------------|-----------------|------|---------------|--------------|---------------|------|--------------|------|

| 6             |                 | Rsvd |               | TERM_B       | Rsvd          | Rsvd | Rsvd         | Rsvd |

| 7             | Rs              | svd  | MODE_QB3[2:0] |              | MODE_QB2[2:0] |      |              |      |

| 8             | Rsvd            |      | ľ             | MODE_QB1[2:0 | ]             | I    | MODE_QB0[2:0 | ]    |

| 9             | DIS_QB3 DIS_QB2 |      | DIS_QB1       | DIS_QB0      |               | Rs   | svd          |      |

| Bit Field Name | Field Type | Default Value | Description                                                                                                                                                                                         |

|----------------|------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TERM_B         | R/W        | 0b            | Indicates termination used on Bank B outputs when HCSL mode is selected: $0=33\Omega/50\Omega$ $1=50\Omega$                                                                                         |

| MODE_QBm[2:0]  | R/W        | 010b          | Output driver mode of operation for output pair QBm, nQBm:  000 = high-impedance 001 = LVPECL 010 = LVDS (default) 011 = Rsvd 100 = HCSL 101 = CML 400mV swing 110 = CML 800mV swing 111 = Reserved |

| DIS_QBm        | R/W        | 0b            | Disable output pair QBm, nQBm:  0 = Output pair QBm, nQBm is enabled (disable output bank using SYNC_DISB to prevent runt pulses when enabling)  1 = Output pair QBm, nQBm is powered-down          |

| Rsvd           | R/W        | -             | Reserved. Always write 0 to this bit location. Read values are not defined.                                                                                                                         |

## **Table 8: Divide Ratio Register Field Locations**

| Address (Hex) | D7 | D6                   | D5 | D4 | D3 | D2 | D1 | D0 |  |  |  |

|---------------|----|----------------------|----|----|----|----|----|----|--|--|--|

| С             |    | DIVA[7:0]            |    |    |    |    |    |    |  |  |  |

| D             |    | DIVB[7:0]            |    |    |    |    |    |    |  |  |  |

| E             |    | Rsvd DIVB[8] DIVA[8] |    |    |    |    |    |    |  |  |  |

| F             |    | Rsvd                 |    |    |    |    |    |    |  |  |  |

| Bit Field Name | Field Type | Default Value | Description                                                                                                                                                 |

|----------------|------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                |            |               | Divider ratio for Bank A outputs:                                                                                                                           |

| DIVA[8:0]      | R/W        | 000h          | 00h - 01h = Bypass divider and pass reference clock directly to the Bank A outputs                                                                          |

|                |            |               | 02h – 1FFh = ratio to be used by the A divider is value written here. For example writing a 4 in this field will results in a divide ratio of 4 being used. |

|                |            |               | Divider ratio for Bank B outputs:                                                                                                                           |

| DIVB[8:0]      | R/W        | 000h          | 00h – 01h = Bypass divider and pass reference clock directly to the Bank B outputs                                                                          |

|                |            |               | 02h – 1FFh = ratio to be used by the B divider is value written here. For example writing a 4 in this field will results in a divide ratio of 4 being used. |

| Rsvd           | R/W        | _             | Reserved. Always write 0 to this bit location. Read values are not defined.                                                                                 |

# **Absolute Maximum Ratings**

The absolute maximum ratings are stress ratings only. Stresses greater than those listed below can cause permanent damage to the device. Functional operation of the 8P79818 at absolute maximum ratings is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

**Table 9: Absolute Maximum Ratings**

| Item                                                                             | Rating         |

|----------------------------------------------------------------------------------|----------------|

| Supply voltage, V <sub>CCX</sub> <sup>[a]</sup> to GND                           | 3.6V           |

| Inputs SCLK, SDATA/SDI, SA0/nCS, CLK_SEL, CLK0, nCLK0, CLK1, nCLK1, OE, nI2C/SPI | -0.5V to 3.6V  |

| Outputs, I <sub>O</sub> QA[0:3], nQA[0:3], QB[0:3], nQB[0:3]                     |                |

| Continuous current                                                               | 40mA           |

| Surge current                                                                    | 60mA           |

| Outputs, V <sub>O</sub> QA[0:3], nQA[0:3], QB[0:3], nQB[0:3]                     | -0.5V to 3.6V  |

| Outputs, V <sub>O</sub> SDO, SDATA/SDI                                           | -0.5V to 3.6V  |

| Operating junction temperature                                                   | 125°C          |

| Storage temperature, T <sub>STG</sub>                                            | -65°C to 150°C |

| Lead temperature (Soldering, 10s)                                                | +260°C         |

a.  $V_{CCx}$  denotes  $V_{CC}$ ,  $V_{CCOA}$ , or  $V_{CCOB}$ .

## **DC Characteristics**

**Table 10: DC Input/ Output Characteristics**

| Symbol                     |                | Paramete                      | r                 | Test Conditions                                         | Minimum | Typical | Maximum | Units |

|----------------------------|----------------|-------------------------------|-------------------|---------------------------------------------------------|---------|---------|---------|-------|

| C <sub>in</sub>            | Input capacit  | ance                          |                   |                                                         |         | 0.5     |         | pF    |

|                            |                | LVPECL                        |                   |                                                         |         | 0.8     |         | pF    |

|                            |                | LVDS                          | QA[0:3], nQA[0:3] | V <sub>CCOX</sub> <sup>[a]</sup> = 3.465V or 2.625V     |         | 1.2     |         | pF    |

|                            |                | CML 400mV                     | QB[0:3], nQB[0:3] | V <sub>CCOX</sub> - 3.405 V 01 2.025 V                  |         | 0.48    |         | pF    |

|                            | Power          | CML 800mV                     |                   |                                                         |         | 0.44    |         | pF    |

| 0                          | dissipation    | LVCMOS                        | Bank A            | V <sub>CCOA</sub> = 3.465V or 2.625V                    |         | 2.33    |         | pF    |

| C <sub>PD</sub>            | capacitance    | LVPECL                        |                   |                                                         |         | 1.4     |         | pF    |

|                            | (per output)   | LVDS                          | QA[0:3], nQA[0:3] | V - 1.00V                                               |         | 1.5     |         | pF    |

|                            |                | CML 400mV                     | QB[0:3], nQB[0:3] | V <sub>CCOX</sub> = 1.89V                               |         | 0.53    |         | pF    |

|                            |                | CML 800mV                     |                   |                                                         |         | 0.3     |         | pF    |

|                            |                | LVCMOS                        | Bank A            | V <sub>CCOA</sub> = 1.89V or 1.575V                     |         | 2.1     |         | pF    |

| R <sub>PULLUP</sub>        | Input pull-up  | resistor                      |                   |                                                         |         | 51      |         | kΩ    |

| R <sub>PULLDOWN</sub>      | Input pull-dov | wn resistor                   |                   |                                                         |         | 51      |         | kΩ    |

|                            |                |                               |                   | LVCMOS output type selected $V_{CCOA} = 3.3V \pm 5\%$   |         | 24      |         | Ω     |

| D                          | Output impos   | lanca                         | OVI3:01 20VI3:01  | LVCMOS output type selected V <sub>CCOA</sub> = 2.5V±5% |         | 15      |         | Ω     |

| R <sub>OUT</sub> Output ir | Output impet   | t impedance QA[3:0], nQA[3:0] |                   | LVCMOS output type selected V <sub>CCOA</sub> = 1.8V±5% |         | 26      |         | Ω     |

|                            |                |                               |                   | LVCMOS output type selected V <sub>CCOA</sub> = 1.5V±5% |         | 46      |         | Ω     |

a.  $V_{CCOx}\, denotes\, V_{CCOA}$  and  $V_{CCOB}.$

# Supply Voltage Characteristics

Table 11: Power Supply Characteristics,  $V_{CC}$  = 3.3V ±5%,  $V_{EE}$  = 0V,  $T_A$  = -40°C to +85°C<sup>[a], [b], [c]</sup>

| Symbol                                   | Parameter              | Test Conditions   | Minimum | Typical | Maximum         | Units |

|------------------------------------------|------------------------|-------------------|---------|---------|-----------------|-------|

| V <sub>CC</sub>                          | Core supply voltage    |                   | 3.135   |         | 3.465           | V     |

| V <sub>CCOA</sub> ,<br>V <sub>CCOB</sub> | Output supply voltage  |                   | 1.71    |         | V <sub>CC</sub> | V     |

| I <sub>CC</sub>                          | Core supply current    |                   |         | 23      | 26              | mA    |

| I <sub>CCOA</sub> +                      | Output supply current  | DIV-by-1          |         | 157     | 177             | mA    |

| I <sub>CCOB</sub>                        | Output supply culterit | DIV A = DIV B = 2 |         | 125     | 140             | mA    |

| I <sub>EE</sub>                          | Power supply current   |                   |         | 183     | 206             | mA    |

a. Internal dynamic switching current at maximum f<sub>OUT</sub> is included.

Table 12: Power Supply Characteristics,  $V_{CC}$  = 2.5V ±5%,  $V_{EE}$  = 0V,  $T_A$  = -40°C to +85°C<sup>[a], [b], [c]</sup>

| Symbol                                   | Parameter             | Test Conditions   | Minimum | Typical | Maximum         | Units |

|------------------------------------------|-----------------------|-------------------|---------|---------|-----------------|-------|

| V <sub>CC</sub>                          | Core supply voltage   |                   | 2.375   |         | 2.625           | V     |

| V <sub>CCOA</sub> ,<br>V <sub>CCOB</sub> | Output supply voltage |                   | 1.71    |         | V <sub>CC</sub> | V     |

| I <sub>CC</sub>                          | Core supply current   |                   |         | 18      | 20              | mA    |

| I <sub>CCOA</sub> +                      | Output outply ourrent | DIV-by-1          |         | 156     | 175             | mA    |

| I <sub>CCOB</sub>                        | Output supply current | DIV A = DIV B = 2 |         | 124     | 139             | mA    |

| I <sub>EE</sub>                          | Power supply current  |                   |         | 177     | 199             | mA    |

a. Internal dynamic switching current at maximum  $f_{\mbox{\scriptsize OUT}}$  is included.

b. All outputs configured for LVEPCL logic levels and not terminated.

c.  $V_{CC} \ge V_{CCOA}$  and  $V_{CCOB}$ .

b. All outputs configured for LVEPCL logic levels and not terminated.

c.  $V_{CC} \ge V_{CCOA}$  and  $V_{CCOB}$ .

Table 13: Power Supply Characteristics,  $V_{CC}$  = 1.8V ±5%,  $V_{EE}$  = 0V,  $T_A$  = -40°C to +85°C<sup>[a], [b], [c]</sup>

| Symbol                                   | Parameter             | Test Conditions   | Minimum | Typical | Maximum         | Units |

|------------------------------------------|-----------------------|-------------------|---------|---------|-----------------|-------|

| V <sub>CC</sub>                          | Core supply voltage   |                   | 1.71    |         | 1.89            | V     |

| V <sub>CCOA</sub> ,<br>V <sub>CCOB</sub> | Output supply voltage |                   | 1.71    |         | V <sub>CC</sub> | V     |

| I <sub>CC</sub>                          | Core supply current   |                   |         | 14      | 16              | mA    |

| I <sub>CCOA</sub> +                      | Output cumply ourrent | DIV-by-1          |         | 143     | 160             | mA    |

| I <sub>CCOB</sub>                        | Output supply current | DIV A = DIV B = 2 |         | 117     | 132             | mA    |

| I <sub>EE</sub>                          | Power supply current  |                   |         | 161     | 181             | mA    |

- a. Internal dynamic switching current at maximum  $f_{\mbox{\scriptsize OUT}}$  is included.

- b. All outputs configured for LVEPCL logic levels and not terminated.

- c.  $V_{CC} \ge V_{CCOA}$  and  $V_{CCOB}$ .

Table 14: Output Supply Current,  $V_{CC}$  = 3.3V, 2.5V or 1.8V,  $V_{EE}$  = 0V,  $T_A$  = 25°C<sup>[a], [b]</sup>

|                   |                          | S                                                     |        | $V_{CCOx}^{[d]} = 3.3V$ |      |        | V <sub>CCOx</sub> <sup>[d]</sup> = 2.5V |        |      |      | V <sub>CCOx</sub> <sup>[d]</sup> = 1.8V |             |        |      | $V_{CCOx}[d] = 1.5V$<br>$V_{CCOx}[d] = 1.5V + 5\%$ |        |             |        |       |

|-------------------|--------------------------|-------------------------------------------------------|--------|-------------------------|------|--------|-----------------------------------------|--------|------|------|-----------------------------------------|-------------|--------|------|----------------------------------------------------|--------|-------------|--------|-------|

| Symbol            | Parameter <sup>[c]</sup> | Test Conditions                                       | LVPECL | LVDS                    | HCSL | LVCMOS | CML                                     | LVPECL | LVDS | HCSL | LVCMOS                                  | CML (400mV) | LVPECL | LVDS | HCSL                                               | LVCMOS | CML (400mV) | LVCMOS | Units |

|                   | Bank A output            | V <sub>CC</sub> = 3.3V,<br>T <sub>A</sub> = 25°C      | 76     | 96                      | 73   | 119    | 60                                      | 75     | 96   | 67   | 92                                      | 58          | 68     | 87   | 66                                                 | 72     | 53          | 60     | mA    |

| I <sub>CCOA</sub> | supply                   | V <sub>CC</sub> = 3.3V + 5%,<br>T <sub>A</sub> = 85°C | 88     | 114                     | 87   | 149    | 70                                      | 88     | 113  | 85   | 111                                     | 67          | 80     | 104  | 78                                                 | 86     | 63          | 71     | mA    |

| 1                 | Bank B output            | V <sub>CC</sub> = 3.3V,<br>T <sub>A</sub> = 25°C      | 76     | 96                      | 73   | 119    | 60                                      | 75     | 96   | 67   | 92                                      | 58          | 68     | 87   | 66                                                 | 72     | 53          | 60     | mA    |

| I <sub>CCOB</sub> | supply<br>current        | V <sub>CC</sub> = 3.3V,<br>T <sub>A</sub> = 85°C      | 88     | 114                     | 87   | 149    | 70                                      | 88     | 113  | 85   | 111                                     | 67          | 80     | 104  | 78                                                 | 86     | 63          | 71     | mA    |

- a. All outputs not terminated.

- b.  $V_{CC} \ge V_{CCOA}$  and  $V_{CCOB}$ .

- c. Internal dynamic switching current at maximum  $f_{\mbox{\scriptsize OUT}}$  is included.

- d.  $V_{CCOx}$  denotes  $V_{CCOA}$  and  $V_{CCOB}$ .

## **DC Electrical Characteristics**

Table 15: LVCMOS/LVTTL Control / Status Signals DC Characteristics,  $V_{EE}$  = 0V,  $T_A$  = -40°C to +85°C

| Symbol          |                        | Parameter                                | Test Conditions                                                           | Minimum | Typical | Maximum              | Units |

|-----------------|------------------------|------------------------------------------|---------------------------------------------------------------------------|---------|---------|----------------------|-------|

|                 |                        |                                          | V <sub>CC</sub> = 3.3V                                                    | 2.20    |         | V <sub>CC</sub> +0.3 | V     |

| $V_{IH}$        | Input high voltage     | je                                       | V <sub>CC</sub> = 2.5V                                                    | 1.85    |         | V <sub>CC</sub> +0.3 | V     |

|                 |                        |                                          | V <sub>CC</sub> = 1.8V                                                    | 1.25    |         | V <sub>CC</sub> +0.3 | V     |

|                 |                        |                                          | V <sub>CC</sub> = 3.3V                                                    | -0.3    |         | 0.8                  | V     |

| $V_{IL}$        | Input low voltage      | e                                        | V <sub>CC</sub> = 2.5V                                                    | -0.3    |         | 0.7                  | V     |

|                 |                        |                                          | V <sub>CC</sub> = 1.8V                                                    | -0.3    |         | 0.7                  | V     |

| I <sub>IH</sub> | Input                  | SA0/nCS, SDATA/SDI,<br>SCLK, CLK_SEL, OE | V <sub>CC</sub> = V <sub>IN</sub> = 3.465V, 2.625V or<br>- 1.89V          |         |         | 5                    | μΑ    |

|                 | high current           | nI2C/SPI                                 | - 1.097                                                                   |         |         | 150                  | μΑ    |

| I <sub>IL</sub> | Input                  | SA0/nCS, SDATA/SDI,<br>SCLK, CLK_SEL,OE  | V <sub>CC</sub> = 3.465V, 2.625V or 1.89V,                                | -150    |         |                      | μΑ    |

|                 | low current            | nI2C/SPI                                 | $V_{IN} = 0V$                                                             | -5      |         |                      | μΑ    |

|                 |                        |                                          | $V_{CC} = 3.3V \pm 5\%, I_{OH} = -5mA$                                    | 2.6     |         |                      | V     |

| V <sub>OH</sub> | Output<br>high voltage | SDATA/SDI, SDO                           | V <sub>CC</sub> = 2.5V ±5%, I <sub>OH</sub> = –5mA                        | 1.8     |         |                      | V     |

|                 |                        |                                          | V <sub>CC</sub> = 1.8V ±5%, I <sub>OH</sub> = –5mA                        |         |         |                      | V     |

| V <sub>OL</sub> | Output<br>low voltage  | SDATA/SDI, SDO                           | V <sub>CC</sub> = 3.3V ±5% or 2.5V ±5% or 1.8V ±5%, I <sub>OL</sub> = 5mA |         |         | 0.5                  | V     |

Table 16: Differential Input DC Characteristics,  $V_{CC}$  = 3.3V±5%, 2.5V±5% or 1.8V±5%,  $V_{EE}$  = 0V,  $T_A$  = -40°C to +85°C

| Symbol           | Paran                 | neter                           | Test Conditions                                          | Minimum    | Typical | Maximum         | Units |

|------------------|-----------------------|---------------------------------|----------------------------------------------------------|------------|---------|-----------------|-------|

| I <sub>IH</sub>  | Input<br>high current | CLKx, nCLKx <sup>[a]</sup>      | V <sub>CC</sub> = V <sub>IN</sub> = 3.465V or 2.625V     |            |         | 150             | μΑ    |

| ı                | Input                 | CLKx <sup>[a]</sup>             | V <sub>CC</sub> = 3.465V or 2.625V, V <sub>IN</sub> = 0V | <b>-</b> 5 |         |                 | μΑ    |

| ¹IL              | low current           | nCLKx <sup>[a]</sup>            | V <sub>CC</sub> = 3.465V or 2.625V, V <sub>IN</sub> = 0V | -150       |         |                 | μΑ    |

| V <sub>PP</sub>  | Peak-to-peak volta    | age <sup>[b]</sup>              |                                                          | 0.15       |         | 1.3             | V     |

| V <sub>CMR</sub> | Common mode in        | put voltage <sup>[b], [c]</sup> |                                                          | 0          |         | V <sub>CC</sub> | V     |

a. CLKx denotes CLK0, CLK1. nCLKx denotes nCLK0, nCLK1.

b.  $\rm\,V_{IL}$  should not be less than –0.3V.  $\rm\,V_{IH}$  should not be higher than  $\rm\,V_{CC}.$

c. Common mode voltage is defined as the cross-point.

Table 17: LVPECL DC Characteristics,  $V_{CC}$  = 3.3V±5%, 2.5V±5% or 1.8V±5%,  $V_{EE}$  = 0V,  $T_A$  = -40°C to +85°C

|                 |                                       |                           | V <sub>CCO</sub>         | $V_{CCOx}^{[a]} = 3.3V \pm 5\%$ |                             |                             | $V_{CCOx}^{[a]} = 2.5V \pm 5\%$ |                          |                             | $V_{CCOx}^{[a]} = 1.8V \pm 5\%$ |                             |       |  |

|-----------------|---------------------------------------|---------------------------|--------------------------|---------------------------------|-----------------------------|-----------------------------|---------------------------------|--------------------------|-----------------------------|---------------------------------|-----------------------------|-------|--|

| Symbol          | Paramete                              | er                        | Min                      | Тур                             | Max                         | Min                         | Тур                             | Max                      | Min                         | Тур                             | Max                         | Units |  |

| V <sub>OH</sub> | Output<br>high voltage <sup>[b]</sup> | Qx,<br>nQx <sup>[c]</sup> | V <sub>CCOx</sub> - 1.30 |                                 | V <sub>CCOx</sub> -<br>0.80 | V <sub>CCOx</sub> -<br>1.35 |                                 | V <sub>CCOx</sub> - 0.80 | V <sub>CCOx</sub> -<br>1.50 |                                 | V <sub>CCOx</sub> -<br>0.90 | V     |  |

| V <sub>OL</sub> | Output<br>low voltage                 | Qx,<br>nQx <sup>[c]</sup> | V <sub>CCOx</sub> - 2.00 |                                 | V <sub>CCOx</sub> -<br>1.75 | V <sub>CCOx</sub> -<br>2.00 |                                 | V <sub>CCOx</sub> - 1.75 | V <sub>EE</sub>             |                                 | 0.25                        | V     |  |

- a.  $V_{CCOx}$  denotes  $V_{CCOA}$  and  $V_{CCOB}$ .

- b. Outputs terminated with  $50\Omega$  to  $V_{CCOx}$  2V when  $V_{CCOx}$  = 3.3V±5% or 2.5V±5%. Outputs terminated with  $50\Omega$  to ground when  $V_{CCOx}$  = 1.8V±5%.

- c. Qx denotes QA0, QA1, QA2, QA3, QB0, QB1, QB2, QB3. nQx denotes nQA0, nQA1, nQA2, nQA3, nQB0, nQB1, nQB2, nQB3.

Table 18: LVDS DC Characteristics,  $V_{CC}$  = 3.3V ±5%, 2.5V ±5% or 1.8V ±5%,  $V_{CCOA}$  =  $V_{CCOB}$  = 3.3V ±5%, 2.5V ±5% or 1.8V ±5%,  $T_A$  = -40°C to +85°C

| Symbol           | Parameter                        |                        | Test Conditions               | Minimum | Typical | Maximum | Units |

|------------------|----------------------------------|------------------------|-------------------------------|---------|---------|---------|-------|

| V <sub>OD</sub>  | Differential output voltage      | Qx, nQx <sup>[a]</sup> |                               | 247     |         | 480     | mV    |

| $\Delta V_{OD}$  | V <sub>OD</sub> magnitude change | Qx, nQx <sup>[a]</sup> | Terminated $100\Omega$ across |         |         | 50      | mV    |

| V <sub>OS</sub>  | Offset voltage                   | Qx, nQx <sup>[a]</sup> | Qx and nQx                    | 1.125   |         | 1.375   | V     |

| ΔV <sub>OS</sub> | V <sub>OS</sub> magnitude change | Qx, nQx <sup>[a]</sup> |                               |         |         | 50      | mV    |

a. Qx denotes QA0, QA1, QA2, QA3, QB0, QB1, QB2, QB3.nQx denotes nQA0, nQA1, nQA2, nQA3, nQB0, nQB1, nQB2, nQB3.

# Table 19: CML (400mV Swing) DC Characteristics, $V_{CC}$ = 3.3V ±5%, 2.5V ±5% or 1.8V ±5%, $V_{CCOA}$ = $V_{CCOB}$ = 3.3V ±5%, 2.5V ±5% or 1.8V ±5%, $T_A$ = -40°C to +85°C

| Symbol           | Parameter            |                        | Test Conditions                                | Minimum                                 | Typical | Maximum                                 | Units |

|------------------|----------------------|------------------------|------------------------------------------------|-----------------------------------------|---------|-----------------------------------------|-------|

| V <sub>OH</sub>  | Output high voltage  | Qx, nQx <sup>[a]</sup> | T                                              | V <sub>CCOx</sub> <sup>[b]</sup> – 0.10 |         | V <sub>CCOx</sub> [b]                   | V     |

| V <sub>OL</sub>  | Output low voltage   | Qx, nQx <sup>[a]</sup> | Terminated with $50\Omega$ to $V_{CCOx}^{[b]}$ | V <sub>CCOx</sub> <sup>[b]</sup> – 0.50 |         | V <sub>CCOx</sub> <sup>[b]</sup> – 0.30 | V     |

| V <sub>OUT</sub> | Output voltage swing | Qx, nQx <sup>[a]</sup> | COOX                                           | 300                                     |         | 500                                     | mV    |

- a. Qx denotes QA0, QA1, QA2, QA3, QB0, QB1, QB2, QB3.nQx denotes nQA0, nQA1, nQA2, nQA3, nQB0, nQB1, nQB2, nQB3.

- b.  $V_{CCOx}$  denotes  $V_{CCOA}$  and  $V_{CCOB}$ .

# Table 20: CML (800mV Swing) DC Characteristics, $V_{CC}$ = 3.3V ±5%, 2.5V ±5% or 1.8V ±5%, $V_{CCOA}$ = $V_{CCOB}$ = 3.3V ±5%, 2.5V ±5% or 1.8V ±5%, $T_A$ = -40°C to +85°C

| Symbol           | Parameter            |                        | Test Conditions                                | Minimum                                 | Typical | Maximum                       | Units |

|------------------|----------------------|------------------------|------------------------------------------------|-----------------------------------------|---------|-------------------------------|-------|

| V <sub>OH</sub>  | Output high voltage  | Qx, nQx <sup>[a]</sup> | T                                              | V <sub>CCOx</sub> <sup>[b]</sup> – 0.10 |         | V <sub>CCOx</sub>             | V     |

| V <sub>OL</sub>  | Output low voltage   | Qx, nQx <sup>[a]</sup> | Terminated with $50\Omega$ to $V_{CCOx}^{[b]}$ | V <sub>CCOx</sub> <sup>[b]</sup> – 0.95 |         | $V_{\rm CCOx}^{\rm [b]}-0.70$ | V     |

| V <sub>OUT</sub> | Output voltage swing | Qx, nQx <sup>[a]</sup> | 1 000%                                         | 575                                     |         | 1000                          | mV    |

- a. Qx denotes QA0, QA1, QA2, QA3, QB0, QB1, QB2, QB3.nQx denotes nQA0, nQA1, nQA2, nQA3, nQB0, nQB1, nQB2, nQB3.

- b. V<sub>CCOx</sub> denotes V<sub>CCOA</sub> and V<sub>CCOB</sub>.

Table 21: LVCMOS Clock Outputs DC Characteristics,  $V_{CC}$  = 3.3V±5%, 2.5V±5% or 1.8V±5%,  $V_{EE}$  = 0V,  $T_A$  = -40°C to +85°C

|                 |                                              | Test                   | V <sub>CCO</sub> | A = 3.3 | V±5% | V <sub>CCO</sub> | A = 2.5 | V±5% | V <sub>CCO</sub> | A = 1.8 | V ±5% | V <sub>CCO</sub> | A = 1.5 | V ±5% |       |

|-----------------|----------------------------------------------|------------------------|------------------|---------|------|------------------|---------|------|------------------|---------|-------|------------------|---------|-------|-------|

| Symbol          | Parameter                                    | Conditions             | Min              | Тур     | Max  | Min              | Тур     | Max  | Min              | Тур     | Max   | Min              | Тур     | Max   | Units |

| V <sub>OH</sub> | Output high voltage QAx, nQAx <sup>[a]</sup> | I <sub>OH</sub> = -8mA | 2.6              |         |      | 1.1              |         |      | 1.1              |         |       | 1.1              |         |       | V     |

| V <sub>OL</sub> | Output low voltage QAx, nQAx <sup>[a]</sup>  | I <sub>OL</sub> = 8mA  |                  |         | 0.5  |                  |         | 0.5  |                  |         | 0.5   |                  |         | 0.5   | V     |

a. QAm denotes QA0, QA1, QA2, QA3. nQAm denotes nQA0, nQA1, nQA2, nQA3.

Table 22: Input Frequency Characteristics,  $V_{CC}$  = 3.3V±5%, 2.5V±5% or 1.8V±5%,  $T_A$  = -40°C to +85°C

| Symbol          | Parameter                       |                            | Test Conditions | Minimum | Typical | Maximum | Units |

|-----------------|---------------------------------|----------------------------|-----------------|---------|---------|---------|-------|

| f <sub>IN</sub> | Input frequency,                | LVPECL,LVDS,<br>HCSL, CML  |                 | 1PPS    |         | 700MHz  |       |

|                 | CLKx, nCLKx                     | LVCMOS                     |                 | 1PPS    |         | 200MHz  |       |

| idc             | Input duty cycle <sup>[a]</sup> |                            |                 |         | 50      |         | %     |

| t               | Carial part alask CCLK          | I <sup>2</sup> C operation |                 | 100     |         | 400     | kHz   |

| †SCLK           | Serial port clock SCLK          | SPI operation              |                 |         |         | 50      | MHz   |

a. Any deviation from a 50% duty cycle on the input may be reflected in the output duty cycle.

### **AC Electrical Characteristics**

Table 23: AC Characteristics,  $V_{CC}$  = 3.3V ±5%, 2.5V ±5% or 1.8V ±5%,  $V_{CCOA}$  =  $V_{CCOB}$  = 3.3V ±5%, 2.5V ±5% or 1.8V ±5%,  $T_A$  = -40°C to +85°C

| Symbol              | Parame                             | ter <sup>[a]</sup>        | Test                                       | Conditions                 | Minimum | Typical | Maximum | Units  |

|---------------------|------------------------------------|---------------------------|--------------------------------------------|----------------------------|---------|---------|---------|--------|

|                     |                                    | LVPECL, LVDS              |                                            |                            | 4DDC    |         | 700MH-  |        |

| f <sub>OUT</sub>    | Output frequency                   | HCSL, CML <sup>[b]</sup>  |                                            |                            | 1PPS    |         | 700MHz  |        |

|                     |                                    | LVCMOS                    |                                            |                            | 1PPS    |         | 200MHz  |        |

|                     |                                    | LVPECL                    | 20% to 80%                                 |                            | 125     |         | 700     | ps     |

|                     |                                    |                           | $V_{CCOx}^{[c]} = 3.3V$                    | 20% to 80%                 | 125     |         | 550     | ne     |

|                     |                                    | LVDS                      | $V_{CCOx}^{[c]} = 2.5V$                    | 20% to 80%                 | 125     |         | 330     | ps     |

|                     |                                    |                           | $V_{CCOx}^{[c]} = 1.8V$                    | 20% to 80%                 | 175     |         | 550     | ps     |

| +_ / +_             | Output rise and fall               | CML, 400mV                | 20% to 80%                                 |                            | 100     |         | 675     | ps     |

| $t_R / t_F$         | times                              | CML, 800mV                | 20% to 80%                                 |                            | 125     |         | 825     | ps     |

|                     |                                    |                           | V <sub>CCOA</sub> = 3.3V                   | 20% to 80%                 |         |         |         |        |

|                     |                                    | LVCMOS                    | V <sub>CCOA</sub> = 2.5V                   | 20% to 80%                 | 200     |         | 800     | ps     |

|                     |                                    | LVGIVIOS                  | V <sub>CCOA</sub> = 1.8V                   | 20% to 80%                 |         |         |         |        |

|                     |                                    |                           | V <sub>CCOA</sub> = 1.5V                   | 20% to 80%                 |         | 650     | 1300    | ps     |

|                     |                                    | LVPECL                    |                                            |                            |         | 15      | 50      | ps     |

|                     |                                    | LVDS                      |                                            |                            |         | 20      | 60      | ps     |

| t <sub>sk</sub> (b) | Bank skew <sup>[d], [e], [f]</sup> | CML                       |                                            |                            |         | 10      | 35      | ps     |

|                     |                                    | HCSL                      |                                            |                            |         | 10      | 35      | ps     |

|                     |                                    | LVCMOS                    |                                            |                            |         | 50      | 100     | ps     |

|                     |                                    | LVPECL,LVDS,<br>HCSL, CML | Even divide ratios                         | S                          | 45      | 50      | 55      | %      |

|                     |                                    | LVPECL,LVDS,<br>HCSL, CML | Odd divide ratios                          | / bypass                   | 43      | 50      | 57      | %      |

| o do                | Output                             |                           | \/ - 2 2\/                                 | Even divide ratios         | 45      | 50      | 55      | %      |

| odc                 | duty cycle <sup>[g]</sup>          | LVCMOS                    | V <sub>CCOA</sub> = 3.3V,<br>2.5V, or 1.8V | Odd divide ratios / bypass | 40      | 50      | 60      | %      |

|                     |                                    |                           |                                            | Even divide ratios         | 40      | 50      | 60      | %      |

|                     | LVC                                | LVCMOS                    | V <sub>CCOA</sub> = 1.5V                   | Odd divide ratios / bypass | 38      | 50      | 62      | %      |

| MUX <sub>ISOL</sub> | Mux isolation                      |                           | 156.25MHz, V <sub>SW</sub>                 | <sub>ING</sub> = 800mV     |         | 61      |         | dB     |

|                     | Noise floor                        |                           | Offset >10MHz fr                           | om156.25MHz carrier        |         | -154    |         | dBc/Hz |

a. Electrical parameters are guaranteed over the specified ambient operating temperature range, which is established when the device is mounted in a test socket with maintained transverse airflow greater than 500lfpm. The device will meet specifications after thermal equilibrium has been reached under these conditions.

b. CML denotes CML 400mV and CML 800mV, unless otherwise stated.

c.  $V_{CCOx}$  denotes  $V_{CCOA}$  and  $V_{CCOB}$ .

- d. This parameter is guaranteed by characterization. Not tested in production.

- e. This parameter is defined in accordance with JEDEC Standard 65.

- f. Defined as skew within a bank of outputs at the same supply voltage and with equal load conditions.

- g. Measured using 50% duty cycle on input reference.

Table 24: HCSL AC Characteristics,  $V_{CC}$  = 3.3V ±5%, 2.5V ±5% or 1.8V ±5%,  $V_{CCOA}$  =  $V_{CCOB}$  = 3.3V ±5%, 2.5V ±5% or 1.8V ±5%,  $T_A$  = -40°C to +85°C

| Symbol             | Parameter <sup>[a]</sup>                                                 | Test Conditions <sup>[b]</sup>       | Minimum | Typical | Maximum | Units |

|--------------------|--------------------------------------------------------------------------|--------------------------------------|---------|---------|---------|-------|

| t                  | Rise/ fall edge rate <sup>[c]</sup>                                      | V <sub>CCOx</sub> = 3.3V or 2.5V     | 0.6     |         | 4       | V/ns  |

| t <sub>SLEW</sub>  | Trise/ fail edge fale-                                                   | V <sub>CCOx</sub> = 1.8V             | 0.45    |         | 4       | V/ns  |

| V <sub>MAX</sub>   | Absolute max. output voltage <sup>[d], [e]</sup>                         | V <sub>CCOx</sub> = 3.3V, 2.5V, 1.8V |         |         | 1150    | mV    |

| V <sub>MIN</sub>   | Absolute min. output voltage <sup>[d], [f]</sup>                         | V <sub>CCOx</sub> = 3.3V, 2.5V, 1.8V | -150    |         |         | mV    |

| V <sub>CROSS</sub> | Absolute crossing voltage <sup>[g], [h]</sup>                            | V <sub>CCOx</sub> = 3.3V, 2.5V, 1.8V |         |         | 550     | mV    |

| $\Delta V_{CROSS}$ | Total variation of V <sub>CROSS</sub> over all edges <sup>[g], [i]</sup> | V <sub>CCOx</sub> = 3.3V, 2.5V, 1.8V |         |         | 140     | mV    |

- a. Electrical parameters are guaranteed over the specified ambient operating temperature range, which is established when the device is mounted in a test socket with maintained transverse airflow greater than 500lfpm. The device will meet specifications after thermal equilibrium has been reached under these conditions.

- b.  $V_{CCOx}$  denotes  $V_{CCOA}$  and  $V_{CCOB}$ .

- c. Measured from –150mV to +150mV on the differential waveform (derived from Qx minus nQx). The signal must be monotonic through the measurement region for rise and fall time. The 300mV measurement window is centered on the differential zero crossing.

- d. Measurement taken from single ended waveform.

- e. Defined as the maximum instantaneous voltage including overshoot.

- f. Defined as the minimum instantaneous voltage including undershoot.

- g. Measured at crossing point where the instantaneous voltage value of the rising edge of Qm equals the falling edge of nQm.

- h. Refers to the total variation from the lowest crossing point to the highest, regardless of which edge is crossing. Refers to all crossing points for this measurement.

- i. Defined as the total variation of all crossing voltages of rising Qm and falling nQm, This is the maximum allowed variance in V<sub>CROSS</sub> for any particular system.

Table 25: Additive Jitter,  $V_{CC}$  = 3.3V, 2.5V or 1.8V,  $V_{CCOA}$  =  $V_{CCOB}$  = 3.3V, 2.5V, 1.8V or 1.5V (1.5V only supported for LVCMOS outputs),  $T_A$  = 25°C

| Symbol               | Paramete                        | er        | Т                                       | est Conditions <sup>[a]</sup>                   | Minimum | Typical | Maximum | Units |

|----------------------|---------------------------------|-----------|-----------------------------------------|-------------------------------------------------|---------|---------|---------|-------|

|                      |                                 |           | f <sub>OUT</sub> =                      | V <sub>CCOx</sub> <sup>[b]</sup> = 3.3V or 2.5V |         | 77      | 92      | fs    |

|                      |                                 | LVPECL    | 156.25MHz                               | V <sub>CCOx</sub> <sup>[b]</sup> = 1.8V         |         | 90      | 117     | fs    |

|                      |                                 | LVFLOL    | f <sub>OUT</sub> =                      | $V_{CCOx}^{[b]} = 3.3V \text{ or } 2.5V$        |         | 50      | 60      | fs    |

|                      |                                 |           | 625MHz                                  | V <sub>CCOx</sub> <sup>[b]</sup> = 1.8V         |         | 60      | 84      | fs    |

|                      |                                 |           | f <sub>OUT</sub> =                      | V <sub>CCOx</sub> <sup>[b]</sup> = 3.3V or 2.5V |         | 85      | 104     | fs    |

|                      | RMS additive jitter             | 156.25MHz | V <sub>CCOx</sub> <sup>[b]</sup> = 1.8V |                                                 | 126     | 185     | fs      |       |

|                      |                                 | LVDS      | f <sub>OUT</sub> =                      | V <sub>CCOx</sub> <sup>[b]</sup> = 3.3V or 2.5V |         | 48      | 61      | fs    |

| t <sub>jit</sub> (f) | (random);<br>Integration range: |           | 625MHz                                  | V <sub>CCOx</sub> <sup>[b]</sup> = 1.8V         |         | 57      | 84      | fs    |

|                      | 12kHz – 20MHz                   |           | f <sub>OUT</sub> =                      | $V_{CCOx}^{[b]} = 3.3V \text{ or } 2.5V$        |         | 92      | 132     | fs    |

|                      |                                 | HCSL      | 156.25MHz                               | V <sub>CCOx</sub> <sup>[b]</sup> = 1.8V         |         | 92      | 133     | fs    |

|                      |                                 | TIOSE     | f <sub>OUT</sub> =                      | V <sub>CCOx</sub> <sup>[b]</sup> = 3.3V or 2.5V |         | 61      | 73      | fs    |

|                      |                                 | 625       | 625MHz                                  | V <sub>CCOx</sub> <sup>[b]</sup> = 1.8V         |         | 67      | 93      | fs    |

|                      |                                 |           | _                                       | V <sub>CCOA</sub> = 3.3V or 2.5V                |         | 98      | 166     | fs    |

|                      |                                 | LVCMOS    | 156.25MHz                               | V <sub>CCOA</sub> = 1.8V                        |         | 128     | 204     | fs    |

|                      |                                 |           |                                         | V <sub>CCOA</sub> = 1.5V                        |         | 198     | 314     | fs    |

a. All outputs configured for the specific output type, as shown in the table.

b.  $V_{CCOx}$  denotes  $V_{CCOA}$  and  $V_{CCOB}$ .

## **Applications Information**

### **Recommendations for Unused Input and Output Pins**

#### Inputs:

#### CLK/nCLK Inputs

For applications not requiring the use of the differential input, both CLK and nCLK can be left floating. Though not required, but for additional protection, a  $1k\Omega$  resistor can be tied from CLK to ground.

#### LVCMOS Control Pins

All control pins have internal pullups and pulldowns; additional resistance is not required but can be added for additional protection. A  $1k\Omega$  resistor can be used.

#### **Outputs:**

#### LVCMOS Outputs

All unused LVCMOS outputs can be left floating. It is recommended that there is no trace attached.

#### LVPECL Outputs

All unused LVPECL outputs can be left floating. We recommend that there is no trace attached. Both sides of the differential output pair should either be left floating or terminated.